Изобретение относится к вычислительной технике и предназначено для вычисления разности двух чисел в прямом коде.

Цель изобретения - увеличение быстродействия.

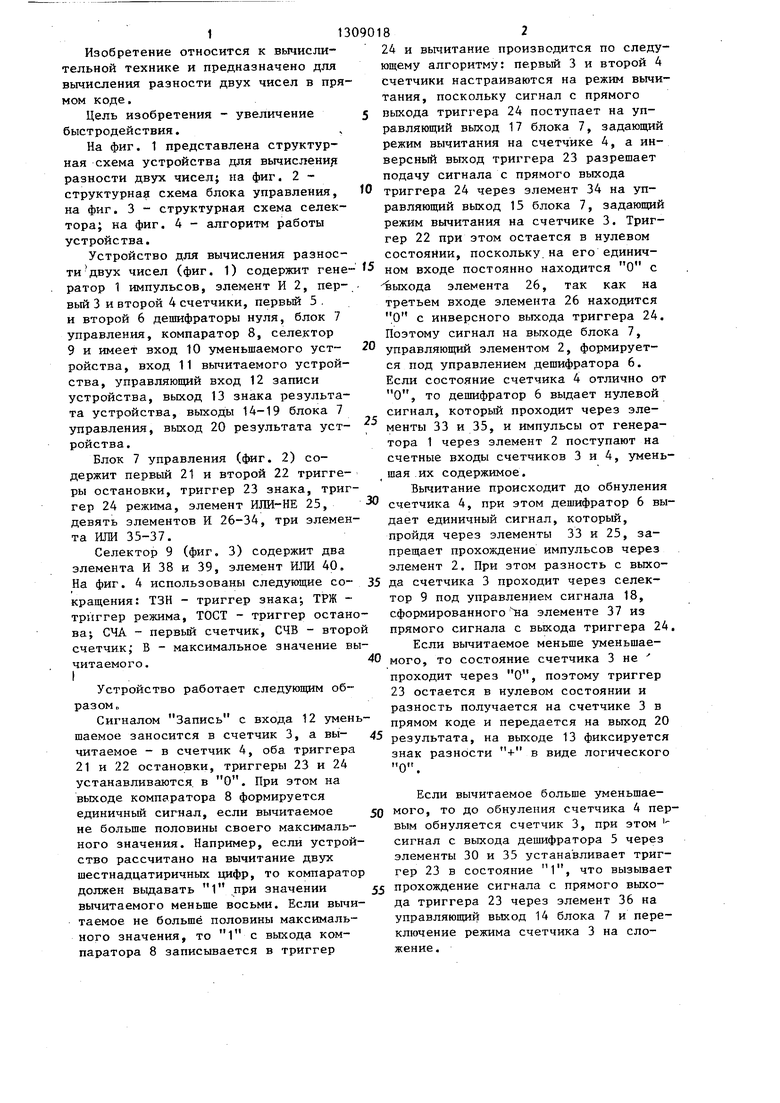

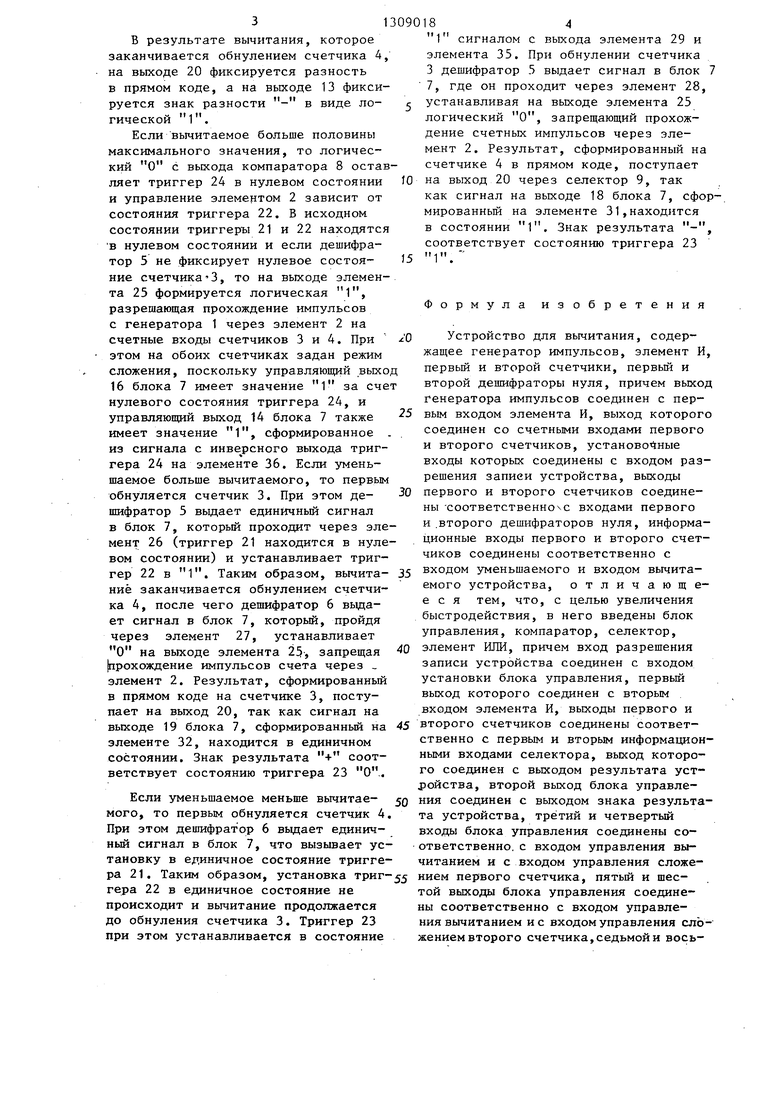

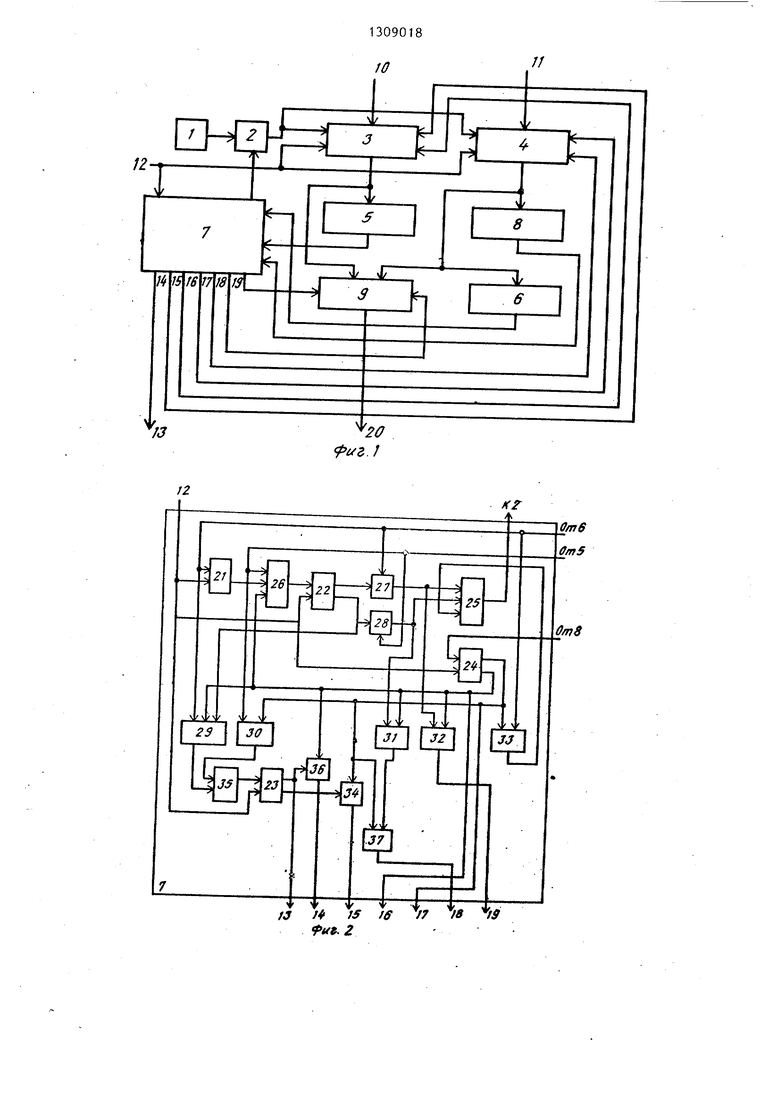

На фиг. 1 представлена структурная схема устройства для вычисление разности двух чисел; на фиг. 2 - структурная схема блока управления, на фиг. 3 - структурная схема селектора j на фиг. 4 - алгоритм работы устройства.

Устройство для вычисления разнос10

24 и вычитание производится по следу ющему алгоритму: первьй 3 и второй 4 счетчики настраиваются на режим вычи тания, поскольку сигнал с прямого выхода триггера 24 поступает на управляющий выход 17 блока 7, задающий режим вычитания на счетчике 4, а ин- версньй выход триггера 23 разрешает подачу сигнала с прямого выхода триггера 24 через элемент 34 на управляющий выход 15 блока 7, задающий режим вычитания на счетчике 3. Триггер 22 при этом остается в нулевом состоянии, поскольку.на его единичти двух чисел (фиг. 1) содержит гене- 5 ном входе постоянно находится О с

ратор 1 импульсов, элемент И 2, первый 3 и второй 4 счетчики, первый 5. и второй 6 депшфраторы нуля, блок 7 управления, компаратор 8, селектор 9 и имеет вход 10 уменьшаемого устройства, вход 11 вычитаемого устройства, управляющий вход 12 записи

устройства, выход 13 знака результата устройства, выходы 14-19 блока 7 управления, выход 20 результата устройства.

Блок 7 управления (фиг. 2) содержит первый 21 и второй 22 триггеры остановки, триггер 23 знака, триггер 24 режима, элемент ИЛИ-НЕ 25, девять элементов И 26-34, три элемента ИЛИ 35-37.

Селектор 9 (фиг. 3) содержит два элемента И 38 и 39, элемент ИЛИ 40. На фиг. 4 использованы следующие со- кращения: ТЗН - триггер знака-, ТРЖ - триггер режима, ТОСТ - триггер останова ; СЧА - первьй счетчик, СЧВ - второ счетчик; В - максимальное значение вычитаемого.

Устройство работает следующим образом „

Сигналом Запись с входа 12 уменьшаемое заносится в счетчик 3, а вычитаемое - в счетчик 4, оба триггера 21 и 22 остановки, триггеры 23 и 24 устанавливаются, в О. При этом на выходе компаратора 8 формируется единичньй сигнал, если вычитаемое не больше половины своего максимального значения. Например, если устройство рассчитано на вычитание двух шестнадцатиричных цифр, то компаратор должен выдавать 1 при значении вычитаемого меньше восьми. Если вычитаемое не больше половины максимального значения, то 1 с выхода компаратора 8 записывается в триггер

24 и вычитание производится по следующему алгоритму: первьй 3 и второй 4 счетчики настраиваются на режим вычитания, поскольку сигнал с прямого выхода триггера 24 поступает на управляющий выход 17 блока 7, задающий режим вычитания на счетчике 4, а ин- версньй выход триггера 23 разрешает подачу сигнала с прямого выхода триггера 24 через элемент 34 на управляющий выход 15 блока 7, задающий режим вычитания на счетчике 3. Триггер 22 при этом остается в нулевом состоянии, поскольку.на его единичном входе постоянно находится О с

5

35

выхода элемента 26, так как на третьем входе элемента 26 находится О с инверсного выхода триггера 24. Поэтому сигнал на выходе блока 7, управляющий элементом 2, формируется под управлением дешифратора 6. Если состояние счетчика 4 отлично от О, то дешифратор 6 выдает нулевой сигнал, который проходит через элементы 33 и 35, и импульсы от генератора 1 через элемент 2 поступают на счетные входы счетчиков 3 и 4, умень- шая их содержимое.

Вычитание происходит до обнуления 30 счетчика 4, при этом дешифратор 6 выдает единичный сигнал, который, пройдя через элементы 33 и 25, запрещает прохождение импульсов через элемент 2. При этом разность с выхода счетчика 3 проходит через селектор 9 под управлением сигнала 18, сформированного а элементе 37 из прямого сигнала с выхода триггера 24.

Если вычитаемое меньше уменьшае3 не

5055

мого, то состояние счетчика проходит через О, поэтому триггер 23 остается в нулевом состоянии и разность получается на счетчике 3 в прямом коде и передается на выход 20 45 результата, на выходе 13 фиксируется

знак разности О.

в виде логического

Если вычитаемое больше уменьшаемого, то до обнуления счетчика 4 первым обнуляется счетчик 3, при этом сигнал с выхода дешифратора 5 через элементы 30 и 35 устанавливает триггер 23 в состояние 1, что вызывает прохождение сигнала с прямого выхода триггера 23 через элемент 36 на управляющий выход 14 блока 7 и переключение режима счетчика 3 на сложение.

3

В результате вычитания, которое заканчивается обнулением счетчика 4 на выходе 20 фиксируется разность в прямом коде, а на выходе 13 фикси

руется знак разности - в виде логической 1.

Если вычитаемое больше половины максимального значения, то логический О с выхода компаратора 8 осталяет триггер 24 в нулевом состоянии и управление элементом 2 зависит от состояния триггера 22. В исходном состоянии триггеры 21 и 22 находятс в нулевом состоянии и если дешифратор 5 не фиксирует нулевое состояние счетчика 3, то на выходе элемента 25 формируется логическая 1, разрешающая прохождение импульсов с генератора 1 через элемент 2 на счетные входы счетчиков 3 и 4. При этом на обоих счетчиках задан режим сложения, поскольку управляющий вых 16 блока 7 имеет значение 1 за сч нулевого состояния триггера 24, и управляющий выход 14 блока 7 также имеет значение 1, сформированное из сигнала с инверсного выхода триггера 24 на элементе 36. Если уменьшаемое больше вычитаемого, то первы обнуляется счетчик 3. При этом дешифратор 5 вьщает единичный сигнал в блок 7, который проходит через элмент 26 (триггер 21 находится в нулвом состоянии) и устанавливает триггер 22 в 1. Таким образом, вычита ниё заканчивается обнулением счетчика 4, после чего дешифратор 6 вьщает сигнал в блок 7, которьй, пройдя через элемент 27, устанавливает О на выходе элемента 25, запрещая прохождение импульсов счета через элемент 2, Результат, сформированный в прямом коде на счетчике 3, поступает на выход 20, так как сигнал на вьпсоде 19 блока 7, сформированньй на элементе 32, находится в единичном состоянии. Знак результата + соответствует состоянию триггера 23 О.

Если уменьшаемое меньше вычитаемого, то первым обнуляется счетчик 4 При этом дешифратор 6 выдает единичный сигнал в блок 7, что вызывает установку в единичное состояние тригге

ра 21. Таким образом, установка триг-55 нием первого счетчика, пятый и шесгера 22 в единичное состояние не происходит и вычитание продолжается до обнуления счетчика 3. Триггер 23 при этом устанавливается в состояние

той выходы блока управления соединены соответственно с входом управления вычитанием и с входом управления сл жением второго счетчика,седьмой и вось

4

1 сигналом с выхода элемента 29 и элемента 35. При обнулении счетчика 3 дешифратор 5 выдает сигнал в блок 7 7, где он проходит через элемент 28, устанавливая на выходе элемента 25 логический О, запрещающий прохождение счетных импульсов через элемент 2. Результат, сформированный на счетчике 4 в прямом коде, поступает на выход 20 через селектор 9, так как сигнал на выходе 18 блока 7, сформированный на элементе 31,находится в состоянии 1. Знак результата -, соответствует состоянию триггера 23

t М

I .

О

5

5 5

0

0

0

Формула изобретения

Устройство для вычитания, содержащее генератор импульсов, элемент И, первьш и второй счетчики, первый и второй дешифраторы нуля, причем выход генератора импульсов соединен с первым входом элемента И, выход которого соединен со счетными входами первого и второго счетчиков, установо ные входы которых соединены с входом разрешения записи устройства, выходы первого и второго счетчиков соединены соответственно с входами первого и .второго дешифраторов нуля, информационные входы первого и второго счетчиков соединены соответственно с входом уменьшаемого и входом вычитаемого устройства, отличающееся тем, что, с целью увеличения быстродействия, в него введены блок управления, компаратор, селектор, элемент ИЛИ, причем вход разрешения записи устройства соединен с входом установки блока управления, первый выход которого соединен с вторым входом элемента И, выходы первого и второго счетчиков соединены соответственно с первым и вторьм информационными входами селектора, выход которого соединен с выходом результата устройства, второй выход блока управления соединен с выходом знака результата устройства, третий и четвертый входы блока управления соединены соответственно, с входом управления вычитанием и с входом управления сложе5 нием первого счетчика, пятый и шестой выходы блока управления соединены соответственно с входом управления вычитанием и с входом управления сложением второго счетчика,седьмой и восьмой выходы блока управления соединены соответственно с первьтм и вторым входами управления селектора, выход второго счетчика соединен с входом компаратора, ВЫХ.ОР, которого соединен с входом признака режима работы блока управления, выходы первого и второго дешифраторов нуля соединены соотве - ственно с первым и вторым входами признака окончания работы блока управления, причем блок управления содержит девять элементов И, три элемента ИЛИ, первьш и второй триггеры остановки, триггер знака, триггер режима и элемент ИЛИ-НЕ, причем вход установки блока управления соединен с входами установки в О первого и второго триггеров остановки, триггера знака и триггера режима, вход признака режима работы блока управления соединен с единичным входом триггера режима, прямой вькод которого соединен с шестым выходом блока управления, первыми входами первого, второго, третьего элементов И блока управления и первым входом первого элемента ИЛИ блока управления, выход которого соединен с седьмым выходом блока управления, первый вход признака окончания работы блока управления соединен с первыми входами четвертого и пятого элементов И блока управления и вторым входом третьего элемента И блока управления, выход которого соединен с первым входом второго элемента ИЛИ блока управления, вькод которого соединен с единичным входом триггера знака, прямой выход которого соединен с вторым выходом блока управления и с первым входом третьего элемента ИЛИ блока управления, второй вход которого соединен с вторым входом пятого элемента И блока управления, первыми входами шестого, седьмого, восьмого элементов И блока

управления, пятым выходом блока управления и инверсным выходом триггера режима, второй вход признака окончания работы блока управления соединен с первым входом девятого элемента И, единичным входом первого триггера остановки, вторыми входами первого и шестого элементов И блока управления, выход шестого элемента

И блока управления соединен с вторым входом второго элемента ИЛИ блока управления, выхода третьего элемента ИЛИ блока управления и второго элемента И блока управления соединены

соответственно с третьим и четвертым выходами блока управления, инверсный выход триггера знака соединен с вторым входом второго элемента И блока управления, второй вход первого

элемента ИЛИ блока управления соединен с выходом седьмого элемента И блока управления, второй вход которого соединен с выходом четвертого элемента И блока управления и первьы

входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента И блока управления, выход первого триггера остановки соединен с третьим входом пятого элемента И

блока управления, выход которого соединен с единичным входом второго триггера останов:, инверсный выход которого соединен с третьим входом шестого элемента И и вторым входом

четвертого элемента И блока управления, прямой выход второго триггера остановки соединен с вторым входом девятого элемента И блбка управления, выход которого соединен с вторым входом восьмого элемента И блока управления и третьим входом элемента ИЛИ-НЕ, выход которого соединен с первым выходом блока управления, выход восьмого элемента И блока управления соединен с восьмым выходом блока управления,

12

Kf

/7m J

Omfi

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычитающее устройство | 1979 |

|

SU771668A1 |

| Устройство для определения одномерных начальных моментов К-го порядка случайного сигнала | 1983 |

|

SU1108464A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| Устройство для регистрации подвижных объектов | 1987 |

|

SU1492356A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Функциональный генератор | 1981 |

|

SU962997A1 |

| Устройство для программного управления | 1986 |

|

SU1397880A1 |

| Устройство для вычисления разности двух чисел | 1979 |

|

SU788109A1 |

| СЕЛЕКТОР ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2085028C1 |

Изобретение относится к области вычислительной техники и предназначено для вычисления разности двух чисел В:прямом кГоде. Цель изобретения- увеличение быстродействия. Устройство для вычисления содержит генератор импульсов, элемент И, первый и второй счетчики, первый и второй дешифраторы нуля, компаратор, селектор и блок управления. 4 ил. 00

| Устройство для сложения | 1980 |

|

SU920709A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычитающее устройство | 1979 |

|

SU771668A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-06—Подача