(54) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Функциональный преобразователь | 1982 |

|

SU1037272A1 |

| Функциональный преобразователь | 1984 |

|

SU1176344A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU960837A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Функциональный преобразователь | 1981 |

|

SU1018127A1 |

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

1

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам кусочно-линейной аппроксимации, и может быть использовано в гибридных вычислительных системах.

Известно устройство для функционального преобразования цифровых сигналов, содержашее реверсивный счетчик, регистр, дешифратор, блок памяти, генератор, элемент И, управляемый делитель :астоты и блок вычитания кодов 1

Недостатками устройства являются пониженные точность и надежность работы.

Наиболее близким к предлагаемому является устройство для функционального преобразования цифровых сигналов, содержашее реверсивный счетчик, выходы которого являются выходами устройства, и регистр, соединенный информационными входами с входом аргумента, а выходами - с входами дешифратора, подключенного выходами через блок памяти к первой группе входов блока вычитания кодов, выход об1 уления которого соединен с первым

ВХОДОМ элемента И, подключенного вторым входом к выходу генератора импульсов, а выходом - к сигнальному входу управ- ляюшего делителя частоты, блок вычитания кодов соединен второй группой входов с выходами реверсивного счетчика, выходами кода разности - с управляющими входами управляемого делителя частоты, выходом знака разности - с входом управления реверсом реверсивного счетчика, а

to выходом обнуления - с управляющим входом регистра и с входом стробирования управляемого делителя частоты, подключенного выходом к счетному входу реверС11ВНОГО счетчика .

15

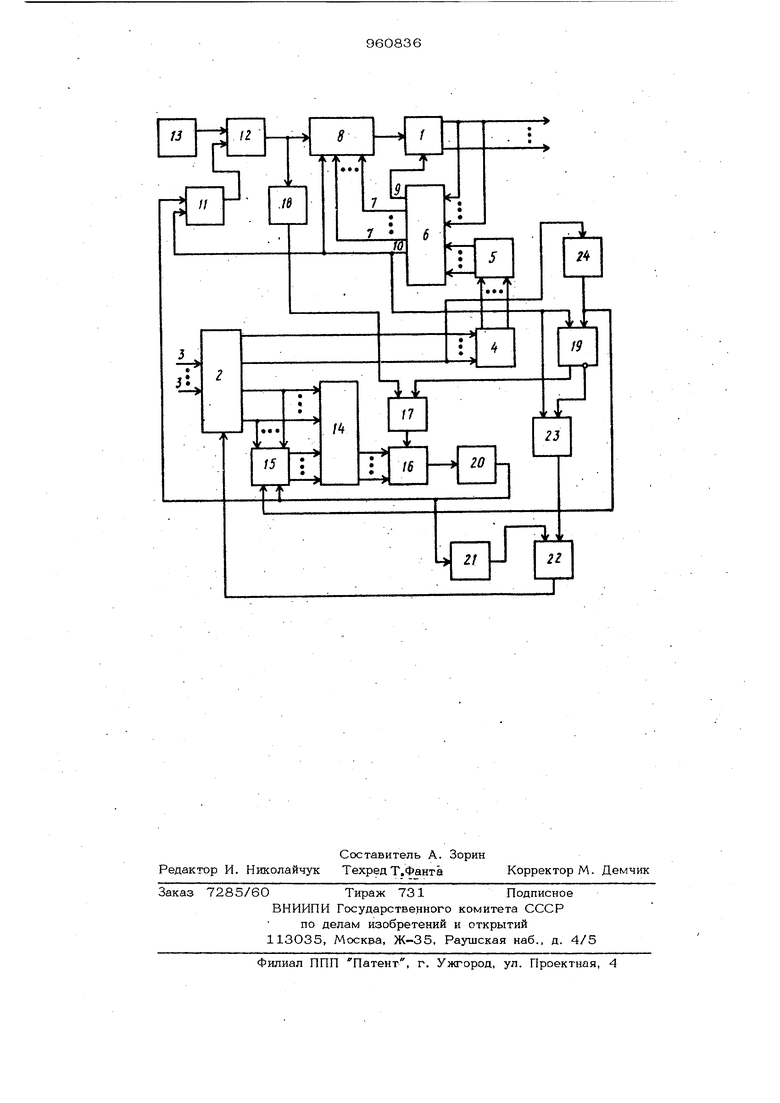

Недостатком данного устройства является пониженная точность работы, обусловленная нечувствительностью к изменениям аргумента в пределах каждого участка ап20проксимаций. При этом независимо от значения поступившего аргумента на выходе устройства воспроизводится весь интервал аппроксимации. Цепью изобретения является повышение точности. Поставленная цель достигается тем, что в функциональный преобразователь, содержащий входной регистр, дешифратор, блок памяти, первый блок вычитания, реверсивный счетчик, управляемый делитель частоты, первый элемент И и генератор импульсов, выход которого соединен с первым входом первого элемента И, выход которого соединен со счетным входом управЛяемого делителя частоты, управляющий вход, вход стробирования и выход которого соединены соответственно с кодовым выходом пер вого блока вычитания, выходом обнуления первого блока вычитания и счетным входом реверсивного счетчика, управляющий вход и выход которого соединены соответственно с выходом знака первого блока вычитания и выходом преобразователя, вход которюго соединен с информационным входом входного регистра, выход старших . разрядов которого соединен с входом аегшифратора, выход которого через блок памяти соединен с первым входом первого блока вычитания, второй вход которого соединен с выходом реверсивного счетчика, дополнительно введены второй блок вычитания, буферный регистр, вычитающий счетчик, элемент задержки, триггер, два формирователя импульсов, делитель частоты, два элемента ИЛИ и два элемента И, выход младших разрядов входного регистора соединен с первым входом второго блока вычитания и через буферный регистр с вторым входом блока вычитания, выход которого соединен с установоч ным входом вычитающего счетчика, счетный вход и выход которого соединены соответственно с выходом второго элемента И и входом первого формирователя импульсов, выход которого соединен с входом сброса буферного регистра и через элемент задержки с первым входом первого элемента ИЛИ, второй вход и вы ход которого соединень соответственно с выходом третьего элемента И и управляющим входом входного регистра, выход младшего из старших разрядов которого через второй формировательимпульса соединен с входом сброса буферного регист ра и входом обнуления триггера, установочный вход которого соединен с выходом обнуления блока вычитания, первым входом третьего элемента И и первым вхо- .дом, второго элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом первого формирователя 1ГМпульсов и вторым входом первого элемента И,, выход которого через делитель частоты соединен с первым входом второго элемента И, второй вход которого соединен с прямым выходом триггера, инверсный выход которого соединен с вторым входом третьего элемента И. На чертеже представлена блок-схема преобразователя. Функциональный преобразователь содержит реверсивный счетчик 1, входной ререгистр 2, вход 3 аргумента, дешифратор 4, блок 5 памяти, блок 6 вычитания, кодовый выход 7, управляемый делитель 8 частоты, выход 9 знака, выход 10 обнуления, элемент ИЛИ 11, элемент И 12, генера тор 13 импульсов, блок 14 вычитания, буферный регистр 15, вычитающий счетчик 16, элемент И 17, делитель 18 частоты, триггер 19, формирователь 20 импульсов, элемент 21 задержки, элемент ИЛИ 22, элемент И 23 и формирователь 24 импульсов. Устройство работает следующим образом. В блок 5 памяти заносятся ординаты узловых точек функции преобразования f (УК), причем в первую ячейку заносится нулевой код. Старшие разряды значения кода аргумента, поступающие на входной регистр 2, преобразуются дешифратором 4 в код адреса, по которому в блоке 5 памяти находится код узловой точки соответствующего значения функаии преобразования. С помощью блока 6 вычитания и управляемого делителя 8 частоты автоматически устанавливается коэффициент наклона аппроксимирующих; отрезков. С помощью блока 14 вычитания, по младшим разрядам кода аргумента, поступающим с регистра 2, вычисляется число, определяющее момен.т остановки воспроизведения функции, при котором на выходе счетчика 1 достигается значение, соответствующее поступившему аргументу. В исходном состоянии реверсивный счетчик 1, вычитающий счетчик 16, входной 2 и буферный 15 регистры и триггер 19 установлены в нуль, и нулевой код с вькода регистра 2 поступает на вход дешифратора 4. При этом нулевой код(Хо) из первой ячейки блока 5 памяти поступает в блок 6 вычитания, который вырабатывает разность кодов, поступающих с выхода блока 5 памяти и реверсивного счетчика 1. Передний фронт сигнала сравнения с выхода 10 .обнуления блока 6 поступает через элемент ИЛИ 11 на второй вход элемента И 12, закрывая его на время установки коэффиш1ента деления, на вход стробирования управляемого делителя 8 частоты, разрешая установку koэффипиeнта деления, и через элемент И 23, по вы сокому уровню с инверсного- выхода триггера 19, ,и элемент ИЛИ 22 на управляющий вход регистра 2, разрешая передачу кода следующего значения аргумента. Рассмотрим работу устройства при раз личных вариантах изменения аргумента на участке аппроксимации. При поступлении на входы регистра 2 кода первого значения аргумента дешиф ратор 4, по старшим разрядам кода аргу- мента, осуществляют выборку адреса узловой точки соответствующего значения функ ции JCx) на данном участке аппроксимации, которое поступает из блока 5 памяти на входы блока 6, формирующего разность кодов €(Х)и f(Xo). поступающую на управляющие входы делителя 8 частоты, в котором устанавливается соответствующий коэффициент деления. Младшие разряды кода аргумента Х поступают во второй блок 14 вычитания, формирующий разность кодов между входшлм 2 и буферным 15 регистрами. Разность кодов () с выхода блока 14 записывается в вычитающий счетчик 16, ;ia счетный вход которого поступают импулъсы с делителя 18 частоты. Причем коэффициент деленияДелителя 18 частоты равен К 2 , где И - число старших разрядов.После поступления на первую группу входов блока 6 значения функции { (X ) на выходе 10 блока б вырабатывается задний фронт сигнала сравнения, задержан ный на время, необходимое для установки коэффициента деления делителя 8 частоты По заднему фронту сигнала сравнения открьгоается элемент И 12, и импульсы с выхода генератора 13 поступают на счет ный вход реверсивного счетчика 1, через управляемый делитель 8 частоты, и счет- laift вход вычитающего счетчика 16, через делитель 18 частоты. Таким образом начинается линейная интерполяция функции на выбранном интервале аппроксимации, причем частота импульсов с выхода генератора 13, поступающая на счетчик 1, определяется коэффициентом деления делителя 8.При обнулении вычитающего счетчика 16 формирователем 2О формируется корот кий импульс, длительность которого определяется временем, необходимым для занесения в счетчик 16 разности кодов из блока 14. По переднему фронту импульса закрьшается элемент Vf 12, и код аргумента Х переписывается с входного регистра 2 в буферный регистр 15.,Задержанный линией 21 задержки на время, необходимое для перезаписи кода Х| с регистра 2 в регистр 15, передний фронт импульса с формирователя 2О разрешает прием очередного кода аргумента в регистр 2. При поступлении следующего кода аргумента в блоке 14 формируется разность кодов ( X-, ) которая заносит ся в счетчик 16. При этом, так как в блоке 6 сигнал сравнения не сформировался, коэффициент деления делителя 8 частоты останется прежним. По заднему фронту импульса с формирователя 20 открывается элемент И 12, и продолжается линейная интерполяция функции. При обнулении счетчика 16 на выходе; формирователя 20 вновь формируется короткий импульс, по которому закрьгоается элемент И 12 и разрешается прием очередного кода аргумента .- При этом изменяется код младшего разряда группы старших разрядов регистра 2, в результате чего на выходе формирователя 24 появляется короткий импульс, по которому триггер 19 меняет свое состояние, а регистр 15 обнуляется. По нулевому уровню с прямого выхода триггера 19 закрывается элемент И 17, и импульсы с генератора 13 не поступают на счетный вход счетчика 16. По заднему фронту импульса с выхода формирователя 20 открывается элемент И 12, и продолжается интерполяция функции. В связи с тем, что в блоке 6 сигнал сравнения еще не выдан, коэффициент деления делителя 8 частоты не меняется и линейная интерполяция осуществляется по закону, определяемому аппроксим1фующей функцией на участке XQ-X .При совпадении кода счетчика 1 и кода { (.у ) на выходе 10 блока 6 формируется импульсный сигнал сравнения. По переднему фронту сигнала сравнения с выхода 1О обнуления блока 6 элемент И 12 закрьшается на время, необходимое для установки коэффициента деления, на управляющий вход регистра 2, по высокому уровню с инверсного выхода триггера 19, через элемент И 23 подается сигнал разрешения приема кода следующего значения аргумента. При поступлении кода аргумента . в блоке 14 форм1фуется разность кодов X i ,- Хо которая заносится в счет796Очик 16, в блоке 6 формируется разность кодов(х.)и f ( , поступающая на управляюшие входы делителя 8 частоты и устанавливающая по сигналу сравнения коэффициент передачи на очередном участ ке аппроксимации. Задним фронтом импульса уравнения с выхода 10 блока 6 триггер 19 переводится в следующее состояние, элементы И 12 и 17 отпираются и начинается линейная интерполяция данного участка функции. На последующих участках аппроксимации устройство работает аналогично. При изменении знака крутизны функции в узловых точках разность кодов {(хц и (Хк.) изменяет знак и признак знака крутизны с выхода 9 блока б управляет реверсом счетчика 1. Таким образом, в предложенном функциональном преобразователе по сравнению с известным повьпиается точность работы, обеспечивается возможность однозначного преобразования ступенчатых сигналов и изменений аргумента в пределах одного участка аштроксимации. Формула изобретения Функциональный преобразователь, содержащий входной регистр, дещифратор, блок памяти, первый блок вычитания, реверсивный счетчик, управляемый делитель час тоты, первый элемент И и генератор импульсов, выходкоторого соединен с первым входом первого элемента И, выход которого соединен со счетным входом управляемого делителя частоты, управляющий вход, вход стробирования и выход которого соединены соответственно с кодовым выхо- Q дом первого блока вычитания, выходом обнуления первого блока вычитания и счетным входом реверсивного счетчика, управляющий вход и выход которого соединены ,соответственно с выходом знака первого j блока вычитания и выходом преобразователя, вход которого соединен с информационным входом входного регистра, выход старших разрядов которого соединен с входом дещифратора, выход которого через

выход которого через делитель частоты соединен с первым входом второго элемента И, второй вход которого соединен с прямым выходом триггера, инверсный выход которого соединен с вторым входом третьего элемента И.

Источники информации, принятые во внимание при экспертизе

кл. G06 F 15/31, 18.12.79 (прототип). 68 блок.памяти соединен с первым входом первого блока вычитания, второй вход которого соединен с вькодом реверсивного счетчика, отличающийся тем, что, с целью повьпиения точности, в него введены второй блок вычитания, буферный регистр, вычитающий счетчик, элемент задержки, триггер, два формирователя импульсов, делитель частоты, два элемен.та И и два элемента ИЛИ, выход младших разрядов входного регистра соединен с первым входом второго блока вычитания и через буферный регистр с вторым входом блока вычитания, выход которого соединен с установочным входом вычитающего счетчика, счетный вход и выход которого соединены соответственно с выходом второго элемента И и входом первого формирователя импулг сов, выход которого соединен с вхоДом сброса буферного регистра и через элемент задержки с первым входом первого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом третьего элемента И и управляющим входом входного регистра, выход младшего из старших разрядов которого через второй формирователь импульсов соединен с входом сброса буферного регистра и входом обнуления триггера, установочный вход которого соединен с выходом обнуления блока вычитания, первым входом третьего элемента И и первым входом второго элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом первого формирователя импуль ов и вторым входом первого элемента И,

Авторы

Даты

1982-09-23—Публикация

1981-02-27—Подача