(50 ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| Устройство для синусно-косинусного цифроаналогового преобразования | 1983 |

|

SU1278897A1 |

| Устройство для программного управления | 1981 |

|

SU987579A1 |

| Устройство для программного управления с самоконтролем | 1983 |

|

SU1130832A1 |

| Аппаратура акустического каротажа нефтяных и газовых скважин | 1980 |

|

SU898369A1 |

| Устройство регулирования и стабилизации мощности | 1987 |

|

SU1578703A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1231610A1 |

| Программное задающее устройство | 1986 |

|

SU1334107A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

1

изобретение относится к автоматике., вычислительной технике и радиосвязи и может найти применение при генерировании аналоговых-функций sint/t, используемых, в частности, для получения радиоимпульсов с ограниченным спектром.

Известен функциональный генератор, содержащий преобразователь временных инетрвалов в последовательность импульсов, реверсивный счетчик, блок памяти, блок декодирования линейных участков и блок весовых коэффициентов CrJ.

Известен также функциональный генератор, содержащий блок управления, счетчик, блок памяти, цифро-аналого- . вые преобразователи, сумматоры, управляемый инвертор, интегратор и компараторы С 2 J.

Недостатком известных генераторов является сложность технической реализации при повышенных требованиях к

точности воспроизведения функции вида sin t/t в широком диапазоне изменения аргумента.

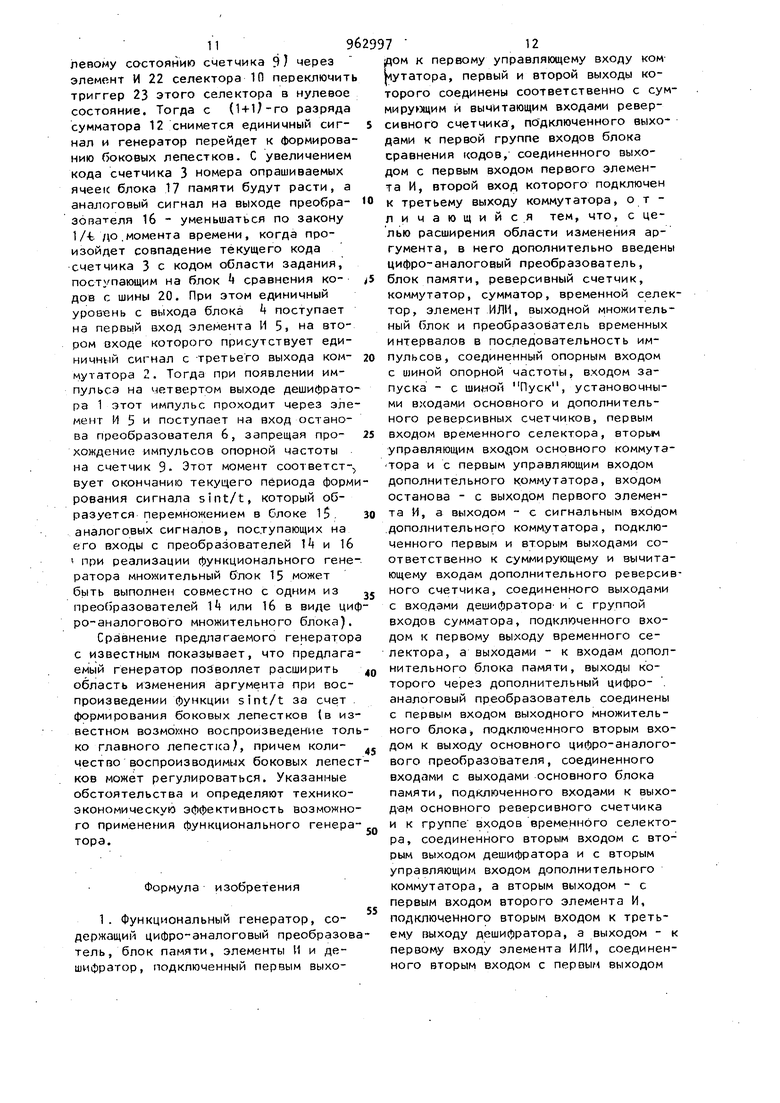

Наиболее близким к предлагаемому является функциональный генератор, содержащий цифро-аналоговый преобразователь, блок памяти, элементы И и дешифратор, подключенный первый выходом к первому управляющему входу коммутаторэу первый и второй выходы, ко10торого соединены соответственно с

. суммирующим и вычитающим входами реверсивного счетчика, подключенного выходами к первой группе входов блока сравнения кодов, соединенного выходами

с первым входом первого элемента И, второй вход которого подключен к третьему выходу коммутатора, соединенного вторым управляющим входом с вторым выходом дешифратора, сигнальным вхо20дом - с выходом управляемого делителя частоты, а четвертым выходом - с первым входом второго элемента И, подклю-ченного вторым входом к выходу блока сравнемия кодсэв, соединенного второй группой входов с первой группой выходов памяти, подключенного адрес иыми входами к выходам кольцевого реверсивного распределителя, входы которого соединены с выходами элементов И, причем вторая группа выходов блока памяти подключена к управляющим входам управляемого делителя частоты а выходы реверсивного счетчика подключены к входам упорно-аналогового преобразователя, выход которого является выходом функционального генератора, причем коммутатор содержит два элемента И и триггер, установочный и обнуляющий входы которого являются соответственно первым и вторым управляющими входами коммутатора, а прямой и мниерсный выходы подключены- к первым входам первого и второго элемен- тов И, выходы которых являются первым и вторым выходами коммутатора, а вторые входы объединены и являются си1- нальным входом коммутатора, причем прямой и инверсный выходы триггера являются третьим и четвертым выходами коммутатора 3j. Недостатком данного генератора является ограниченная область изменения аргумента при воспроизведении функции sint/t. Цель изобретения - расширение области изменения аргумента. С этой целью в функциональный генератор, содержащий циf po-aнaлoгoвый преобразователь, блок памяти, элементы И и.дешифратор, подключенный первым пыходом к первому управляющему входу коммутатора, первый и второй выходы которого соединены соответствено с суммирующим и вычитающим входами реверсивного счетчика, подключен ного выходами к первой группе входов блока сравнения кодов, .соединенного выходом с первым входом первого элемента И, вторрй вход которого подключен к третьему выходу коммутатора дополнительно введены цифро-аналоговый преобразователь, блок памяти, реверсивный счетчик, коммутатор,.сумматор, временной селектор, элемент ИЛИ выходной множительный блок и преобразователь временных интервалов в после довательность импульсов, соединенный опорным входом с шиной опорной частоты, входом запуска-- с шиной Пуск, установочными входами основного и дополнительного реверсивных счетчиков. первым входом временного селектору, вторым управляющим входом основного коммутатора и с первым управляющим входом дополнительного коммутатора и входом останова - с выходом первого элемента И, а выходом - с сигнальным входом дополнительного коммутатора, подключенного первым и вторым выходами соответственно к суммирующему и вычитающему входам дополнительного . реверсивного счетчика, соединенного выходами с входами дешифратора и с группой входов сумматора, подключенного входом к первому выходу временного селектора, а выходами - к входам дополнительного блока памяти, выходы которого через дополнительный цифроаналоговый преобразователь соединены с первым входом выходного множительного блока, подключенного вторым входом к выходу основного цифро-аналогового преобразователя, соединенного входами с выходами основного блока памяти, подключенного входами к выходам основного реверсивного счетчика и к группе входов временного селектора, соединенного вторым входом с вторым выходом дешифратора и. с вторь1м управляющим входом дополнительного коммутатора, а вторым выходом - с первым входом второго элемента И, подключенного вторым входом к третьему выходу де,шифратора, а выходом - к первому входу, элемента ИЛИ, соединенного вторым Б-ХОДОМ с первым выходом дешифратора, а выходом - с третьим управляющим входом дополнительного коммутатора, причем четвертый выход дешифратора подключен к сигнальному входу основного коммутатора и к третьему входу первого элемента И, а вторая группа входов блока сравнения кодов соединена с установочными входами разрядов основного реверсивного счетчика и с шиной ввода кода области задания функции. Временной селектор содержит дешийратор, элемент И и триггер, прямой и инперсный ВЫХОДА которого являются первым и вторым выходами временного селектора, а счетный вход подключен к выходу элемента И, соединенно.го первым входом с выходом дешифратора, входы которого являются группой входов временного селектора, а вход обнуления триггера и второй вход элемента И являются соответственно первым и вторым входами временного селектора. Кроме того, дополнительный коммутатор содержит два элемента И и триггер.. установочный, счетный и обнуляющий ; входы которого являются соответственно первым, вторым и третьим управляющими входами дополнительного коммутатора, а прямой и инверсный выходы под ключены к первым входам соответственно первого и второго элементов И, выходы которых являются первым и вторым выходами дополнительного коммутатора, а вторые входь объединены и являются сигнальным входом дополнительного коммутатора. На фиг. 1 дана блок-схема функционального генератора; на фиг. 2-i - . графики, поясняющие его принцип действия. Функциональный генератор (фиг. 1) содер)хит дешифратор 1 , подключенный первым выходом к первому управляющему входу основного коммутатора 2, первый и второй выходы которого соединены соответственно с суммирующим и вычита ющим входами основного реверсивного счетчика 3. Счетчик 3 подключен выходами к первой группе входов блока 4 сравнения кодов, соединенного выходом с первым входом первого элемента И 5, второй вход которого подключен к третьему выходу коммутатора 2. Преобразователь 6 временных интервалов в последовательность импульсов соединен опорным входом с шиной 7 опорной частоты, входом запуска - с шиной 8 Пуск, установочными входами основного и дополнительного реверсивных счетчиков 3 и 9 первым входом временного селектора 10, вторым управляю щим входом коммутатора 2 и с первым управляющим входом дополнительного коммутатора 11, входом останова - с выходом элемента И 5, а выходом - с сигнальным входом, коммутатора 11. Ком мутатор 11 подключен первым и вторым выходами соответственно к суммирующему и вычитающему входу дополнительного реверсивного счетчика 9, соединенного выходами с входами дешифратора 1 и с группой входов сумматора 12. Сумматор 12 подключен входом к первому выходу временного селектора 10 а выходами - к входам дополнительного блока 13 памяти. Выходы блока 13 через дополнительный цифро-аналоговый преобразователь Т соединены с первым входом выходного множительного блока 15. Блок 15 подключен вторым вхо дом к выходу основного цифро-аналогового преобразователя 1б, соединенного бходами с выходами.основного блока 17 амяти. Блок 17- подключен входами к ыходам реверсивного счетчика 3 и к группе входов временного селектора 10, оединенного вторым входом с вторым выходом дешифратора 1 и с вторым управляющим входом коммутатора 11, а вторым выходом - с первым входом втс рого элемента И 18. Элемент И 18 подключен вторым входом к третьему выходу дешиЛратора 1, а выходом - к первому входу элемента ИЛИ.19, среди ненного вторым входом с первым выходом дешиЛратора, а выходом - с третьим управляющим входом коммутатора. 11. Четвертый выход дешиЛратора 1 подключен к сигнальному входу коммутатора 2 и к третьему входу элемента И 5. Вторая группа входов блока ( сравнения кодов соединена с установочными входами разрядов реверсивного счетчика 3 и с шиной 20 ввода кода области задания функции. Временной селектор 10 может быть выполнен, например,на дешиЛратора 21, элементе И 22 и триггере 23, прямой и инверсный выходы которого являются первым и вторым выходами селектора 10, а счетный вход подключен к выходу элемента И 22, соединенного первым входом с выходом дешифратора 21. Входы дешиОратора 21 являются группой входов селектора 10, а вход обнуления триггера 23 и второй вход элемента И 22 являются соответственно первым и вторым входами селектора 10. Коммутатор 2 может быть выполнен на двух элементах И 2 и 25 и триггере 26, установочный и обнуляющий входы которого являются первым и вторым управляющими входами коммутатора 2 , а прямой и инверсный выходы подключены к первым входам соответственно первого и второго элементов И 2 и 25. Выходы элементов И и 25 являются первым и вторым выходами коммутатора 2, а вторые входы элементов И и 25 объединены и являются си1- нальным входом коммутатора 2, третьим выходом которого является прямой выход триггера 26. Коммутатор 11 может быть также выполнен на двух элементах И 27 и 28 и триггере 29, установочный, счетный . и обнуляхзщий входы которого являются соответсаенно первым, вторым , и третьим управляюи ими входами коммутатора 11, а прямой и инверсный выходы подключены к первым входам элементов 11 27 и 28. Выходы элементов И 27 79629 и 28 являются первым и вторым выходами коммутатора 11, а эторые входы элементов И 27 и 28 объединены и являются сигнальным входом коммутатора 11, Преобразователь 6 временных ин- 5 тервалов э последовательность импульсов может быть выполнен на триггере 30 и элементе И 31, первый вход и выход которого являются соответственно опорным входом и выходом преобразова-О теля 6, а второй вход элемента И 31 подключен к выходу триггера 30, установочный и обнуляющий входы которого являются соответственно входами заnycK.i и останова преобразователя 6, 15 Преобразователь 6 служит для преобразования интервалов времени, определяющих состояние триггера 30, в последовательность тактовых импульсов опорной частоты, поступающих на преоб-го разоиатель 6 с шины 7. Коммутаторы 2 и 11 предназначены для управления рех имами работы реверсивных счетчиков 3 и 9. Временной селектор 10 слу-жит для определения временного интер-25 вала, соответствующего длительности глагзного лепестка функции sin t/t. Общий принцип действия функционального генератора основан на формировании двух независимых функций sint и 1/t эо с некоторыми дополнениями и в последующем их перемножений. Коммутатор 11, счетчик 9, блок 13 памяти и преобразователь 1A выполняют главную роль фор1 миррвания функции sin t, а коммутатор 2, счетчик 3,-блок 17 памяти и преобразователь 1б выполняют главную роль формирования функции 1/t, На фиг, 2 изображен общий вид син-. тезируемого сигнала. Сигнал формируется по частям, при этом на выходе преобразователя формируется сигнал вида фиг, 3, а на выходе преобразования 16 - сигнал вида фиг. , Как еле-., дует из графиков (фиг,3). на интервале а -d синтезируется функция вида sin t, а на интервале d -О - вида sin t/t (главный лепесток), при этом последовательность значений функции sin t на интервале Ъ - записывается в двоичном коде в первые К ячейки блока 13 памяти, а последовательность значений функции 5int/t на интервале d-О записывается в двоичном коде в последующие ЗК/2 ячейки блока 13 памяти. Огибающая сигнала, изобракенно го на фиг, , на интервале прядстаоляет собой функции 1/t, л ил ин78 тepв;злcd О имеет постопнчс-г зилмение, так как на этом интервале в сигнале {фиг, З) (|юрмируется непосредствеино функция вида sint/t. Поэтому в ячейках блока 17 памяти (и- емкость блока 17) записывается последовательность значений функции 1/-t, за исключением нулевой и первой ячеек, в которые записано максимально возможное значение. Следует отметить, что у функции (фиг. ), аппроксимирующей l/-fc, скачки осуществляются в моменты, соответствующие переходам через нуль функции, изображенной на фиг, 3, что позволяет уменьшить искаженил и повысить точность формирования sin t/t, Функциональный генератор работает следующим образом, Стартовый импульс с шины 8 поступает на установочный вход счетчика 3, осуществляя запись в разряды счетчика 3 кода области задания функции с 0, соответствующего количест У формируемых боко-вых лепестков на периоде выходного сигнала функциональ ° ° генератора (количество боковых лепестков четное). Этот же стартовый yctaнaвливaeт триггер 2б коммутатора 2 и триггер 23 селектора 10 в нулевое состояние, а триггер 29 коммутатора 11 и триггер 30 преобразователя 6 - в единичное состояние и осуществляет установку счетчика 9 в исходное состояние, равное К/2 (К - количество ячеек блока 13 памяти, в которые записана функция sint). При этом триггер 30 открывает эле-, мент И 31 и разрешает прохождение импульсов.опорной частоты с шины 7 Мерез преобразователь 6 и коммутатор 11 на суммирующий вход счетчика 9. Последовательное накопление кода в счетчике 9 вызывает последовательный опрос ячеек блока 13 памяти (выходной КОД сумматора 12 соответствует коду, поступающему на группу его входов, так как на входе сумматора 12, соединенном с выходом селектора 10, присутствует нулевой потенциал). Когда на выходе счетчика 9 будет сформирован код, соответствующий адресу (К-1)-ой ячейки блока 13 памяти, на третьем выходе дешифратора 1 появляется импульс, который через элемент И ТВ, на втором входе которого имеется единичный сигнал с второго выхода селектора 10, и элемент ИЛИ 19 переключлет триггер 29 коммутатора 11. Всяедствис .этого имгтульсы опорной частоты начин-зпт поступать на вычитаю щий вход счетмика 9. Код адреса на вы ходе счетчика 9 начинает последовател но уменьшаться, что приводит к последовательному опросу ячеек блока 13 памяти в .обратном направлении. При нулевом состоянии счетчика 9, соответствующем адресу нулевой ячейки блока 13 памяти, на втором выходе дешифратора 1 появляется импульс, котopы 1 переключает триггер 29 в единичное состояние, и весь цикл работы повторяется. Цифровая информация о значении сигнала считывается с последовательно опрашиваемых в прямом и обратном направлении ячеек блока 13 памяти и затем с помощью преобразователя 1 преобразуется в аналоговый сигнал. Одновременно с этим сигналом на выходе преобразователя 16 формируется сигнал, изображенный на фиг. i. Форми рование данного сигнала осуществляется следующим образом. При переходе счетчика 9 через (К/2-1)-ое состояние на четвертом выходе дешифратора 1 образуется импульс, поступающий на сигнальный вход коммутатора 2. Так как стартовый импульс с шины 8 установил триггер 26 коммутатора 2 в нуле вое состояние, то импульс с четвертого выхода дешифратора 1 поступает на вычитающий вход счетчика 3, на выходе которого адресный код уменьшится на единицу. Следовательно, изменится и номер опрашиваемой ячейки блока 17 памяти, а значит и двоичная информация на выходе блока 17, которая с помощью преобразователя 1б преобразуется в. аналоговый сигнал. Последующие импульсы с четвертого выхода дешифратора 1 будут также уменьшать адресный код счетчика 3, что приводит к последовательному опросу ячеек блока 17 Памяти и т.д. Аналоговый сигнал на Ыходе преобразователя 16 будет нарастать до тех пор,, пока очередной импульс с четвертого выхода дешифратора 1 не переведет счетчик 3 в едини ное состояние. При этом на выходе дешифратора 21 селектора 10 образуется единичный сигнал, поступающий на эле меит И 22 селектора 10. Через некоторо ; время (соответствующее на фиг.З точке d) при очередном, обнулении счетмика 9 импульс со второго выхода дешифратора 1 через элемент И 22 селектора 10 переключит триггер 23 этого селектора в единичное состояние. При этом единичный сигнал с первого выхода селектора 10 поступит на сумматор 12, на вход его (1+1)-го двоичного разряда (1 1од,). Э.то объясняется тем, что точка d(. 3) соответствует переходу на формирование главного лепестка выходного сигнала генератора, а (как указывалось выше) последовательность значений си1- нала на интервале d-О записана в ячейки блока 13 памяти с номерами от К-ой до ()К/2-1)-ой при длине последовательности о 3/2 К. Временной селектор 10 позволяет, не меняя режима работы счетчика 9, автоматически перейти на считывание ячеек блока 13 памяти, начиная с К-ой ячейки. Единственное отличие в работе счетчика 9 состоит в том, что его максимальное состояние при этом не (К-1)-ое, как было при формировании боковых лепестков Функции, а(ЗК/2-1)-ое . Это достигается следующим образом. После того как триггер 23 селектора 10 перейдет в единичное состояние, нулевой сигнал с его инверсного выхода запретит прохождение очередного импульса с третьего выхода дешифратора 1 через элемент И 18. При этом счетчик 9 будет продолжать работать в рехиме суммирования, пока не достигнет {ЗК/2- 1)-го состояния (точка О на фиг. 3J. Тогда на первом выходе деши()ратора 1 появится импульс, который через элемент ИЛИ 19 переключит триггер 29 коммутатора 11, переводя счетчик 9 в режим вычитания. Этот же импульс переведет триггер 2б коммутатора 2 в единичное состояние и счетчик 3 начнет работать в режиме суммирования. Момент о на фиг. 2-А соответствует оси симметрии формируемого сигнала (для иллюстрации на фиг. 4 проставлены номера состояний счетчика 3). При формировании правой части относительно оси симметрии выходного сигнала первый импульс с четвертого выхода дешифратора 1, соответствующиС|( К/2-l}-ому состоянию счетчика 9, переведет счетчик 3 в единичное состояние. При этом на выходе дешифратора 21 селектора 10 образуется единичный уровень, который позволит очередному импульсу со второго выхода дешифратора. С соответствующего нулевому состоянию счетчика 9) через элемент И 22 селектора 1П переключит триггер 23 этого селектора в нулевое состояние. Тогда с (1 + U-ro разряда сумматора 12 снимется единичный сигнал и генератор перейдет к формирова нию боковых лепестков. С увеличением кода счетчика 3 номера опрашиваемых ячеек блока 17 памяти будут расти, а аналоговый сигнал на выходе преобразогаателя 16 - уменьшаться по закону 1/-fe До .момента времени, когда произойдет совпадение текущего кода счетчика 3 с кодом области задания, поступающим на блок сравнения кодов с шины 20. При этом единичный уровень с выхода блока поступает на первый вход элемента И 5, на втором входе которого присутствует единичный сигнал с -третьего выхода коммутатора 2. Тогда при появлении импульса на четвертом выходе дешифрато ра 1 этот импульс проходит через эле мент И 5 и поступает на вход останова преобразователя 6, запрещая прохождение импульсов опорной частоты на счетчик 9. Этот момент соответст-, вует окончанию текущего периода форм рования сигнала sint/t, который образуется перемножением в блоке 15. аналоговых сигналов, поступающих на его входы с преобразователей Il и 16 при реализации функционального гене ратора множительный блок 15 может быть выполнен совместно с одним из преобразователей или 1б в виде ци ро-аналогового множительного блока). Сравнение предлагаемого генератор с известным показывает, что предлага емый генератор позволлет расширить область изменения аргумента при воспроизведении функции sint/t за счет формирования боковых лепестков (в из вестном возмох но воспроизведение тол ко главного лепестка, причем количество воспроизводимых боковых лепес ков может регулироваться. Указанные обстоятельства и определяют техникоэкономическую эффективность возможно го применения функционального генера тора. Формула изобретения 1 . Функциональный генератор, содержащий цифро-аналоговый преобразов тель, блок памяти, элементы И и дешифратор, подключенный первым выхоДОМ к первому управляющему входу ком утатора, первый и второй выходы которого соединены соответственно с сумми рущим и вычитающим входами реверсивного счетчика, подключенного выходами к первой группе входов блока сравнения кодов, соединенного выходом с первым входом первого элемента И, второй вход которого подключен к третьему выходу коммутатора, о т личающийс.я тем, что, с целью расширения области изменения аргумента, в него дополнительно введены цифро-аналоговый преобразователь, блок памяти, реверсивный счетчик, коммутатор, сумматор, временной селектор, элемент ИЛИ, выходной множительный блок и преобразователь временных интервалов в последовательность импульсов, соединенный опорным входом с шиной опорной частоты, входом запуска - с шийой Пуск, установочными входами основного и дополнительного реверсивных счетчиков, первым входом временного селектора, вторым управляющим вхО(дом основного коммута тора и с первым управляющим входом дополнительного коммутатора, входом останове - с выходом первого элемента И, а выходом - с сигнальным входом .дополнительного коммутатора, подключенного первым и вторым выходами соответственно к суммирующему и вычитающему входам дополнительного реверсивного счетчика, соединенного выходами с входами дешифратора- и с группой входов сумматора, подключенного входом к первому выходу временного селектора, а выходами - к входам дополнительного блока памяти, выходы которого через дополнительный цифро- . аналоговый преобразователь соединены с первым входом выходного множительного блока, подключенного вторым входом к выходу основного цифро-аналогового преобразователя, соединенного входами с выходами основного блока памяти, подключенного входами к выход-ам основного р еверсивного счетчика и к группе входов временного селектора, соединенного вторым входом с вторым выходом дешифратора и с вторым управляющим входом дополнительного коммутатора, а вторым выходом - с первым входом второго элемента И, подключенного вторым входом к третьему выходу дешифратора, а выходом - к первому входу элемента ИЛИ, соединенного вторым входом с первым выходом дешифратора, а выходом - с трптьим управляющим входом дополнительного коммутатора, причем четвертый выход дешифратора подключен к сигнальному входу основного коммутатора и к тре|Тьему входу первого элемента И, а вто рая группа входов блока сравнения кодов соединена с установочными входами разрядов основного реверсивного счетчика и с шиной ввода кода области задания функции. 2. Генератор по г1. 1 , о т л и ч а ю щ и и с я тем, что временной селектор содержит дешифратор, элемент И и триг гер, прямой и инверсный выходы которо го являются первым и вторым выходами временного селектора, а счетный вход подключен к выходу элемента И, соединенного первым входом с выходом дешиф ратора , входы которого являются группой входов временного селектора, а вход обнуления триггера и второй вход элемента И являются соответственно первым и вторым входами временного {Селектора. 96 I }, Генератор по п. 1,отличаю щ и и с я тем, что дополнительный коммутатор содержит два элемента И и триггер,установочный, счетный и обнуляющий входы которого являются соответственно первым, вторым и третьим управляющими входами дополнительного коммутатора, а прямой и инверснь)й выходы подключены к первым входам соответственно первого и второго элементов И, выходы которых являются первым и вторым выходами дополнительного коммутатора, а вторые входы объединены и являются сигнальным входом дополнительного коммутатора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 51989, кл. G Об F 1/02, 19732.Авторское свидетельство СССР 72С)542, кл. G 06 G 7/26, 19773.Авторское свидетельство СССР № 389519, кл. G Об Т. 7/26, 1971 (прототип).

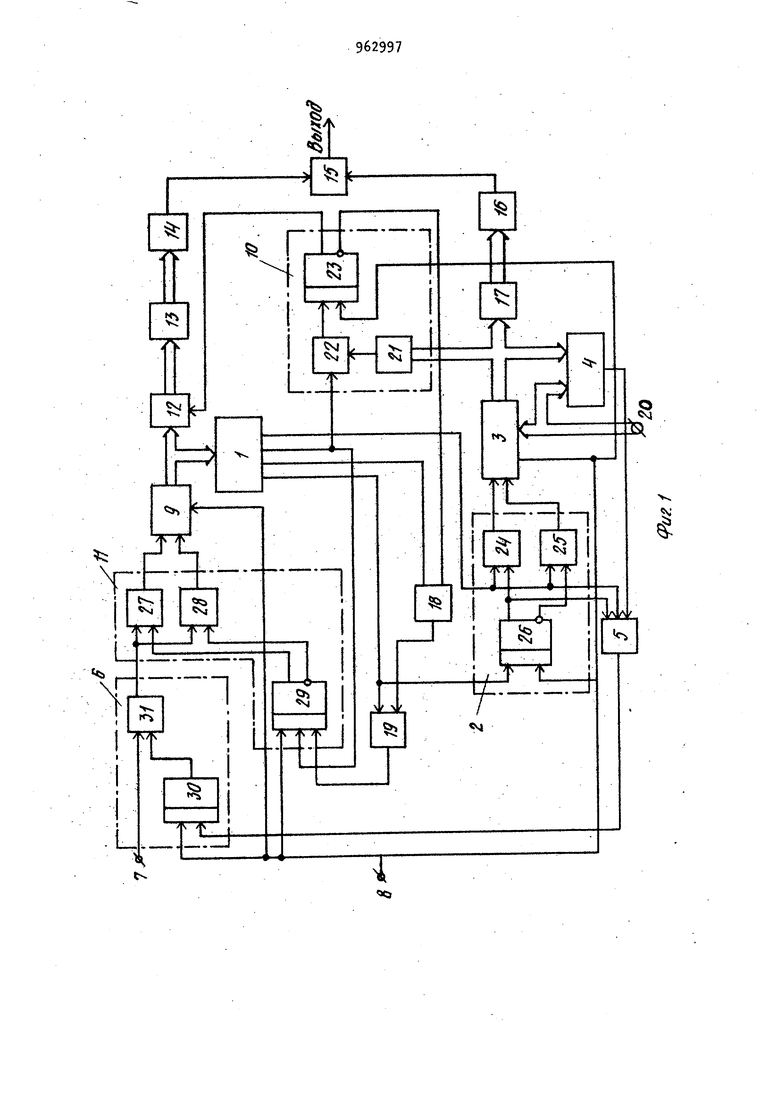

Scni/i

fP(J.

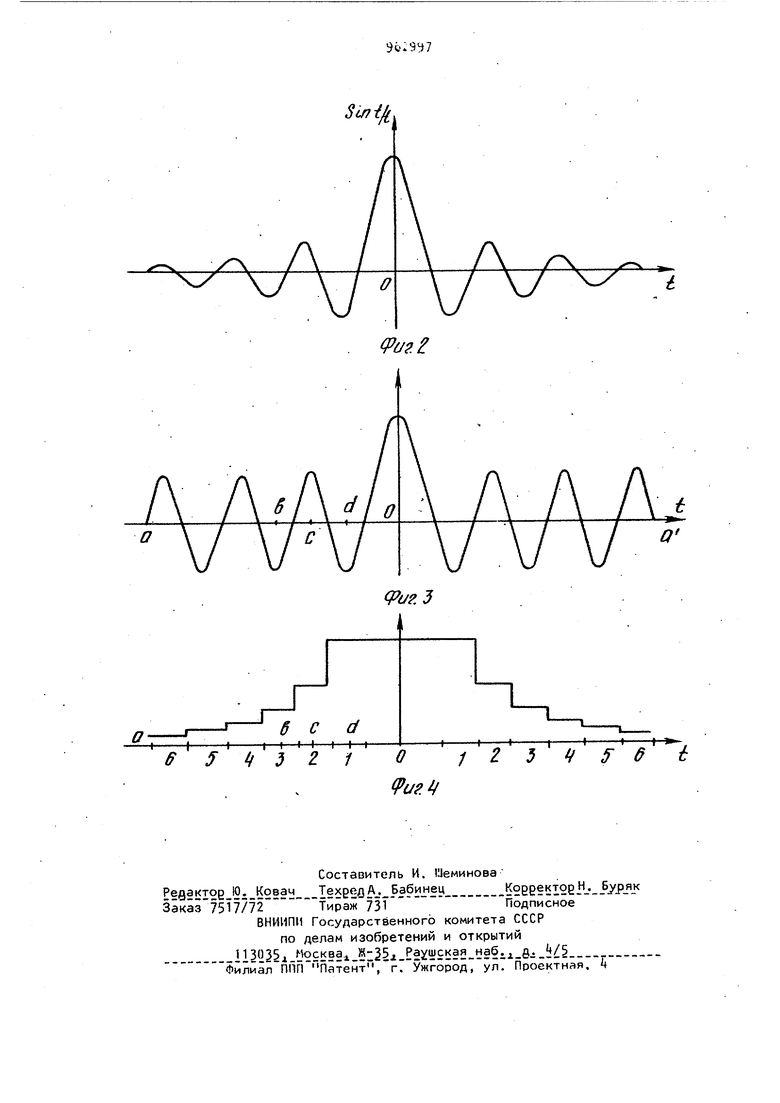

O

ff J д г 1

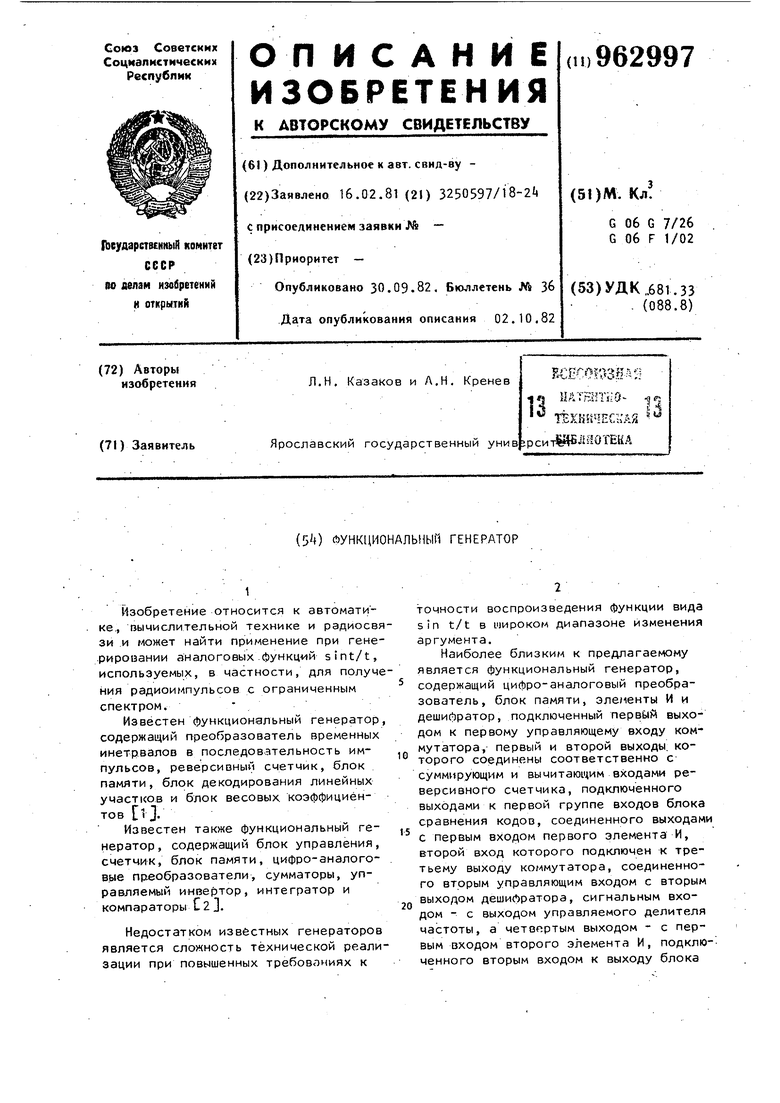

1 г 4

О

Авторы

Даты

1982-09-30—Публикация

1981-02-16—Подача