массивов или переупорядочиванием ранее записанных данных. Коррелятор содержит коммутатор 1 эталона, коммутатор 2 сигнала, регистры 3 сигнала, элементы И 4, регистры 5 эталона.

Изобретение относится к вычислительной технике, в частности к устройствам статистической обработки сигналов, и может найти применение в корреляционно-экстремальных системах

Цель изобретения - повышение быстродействия.

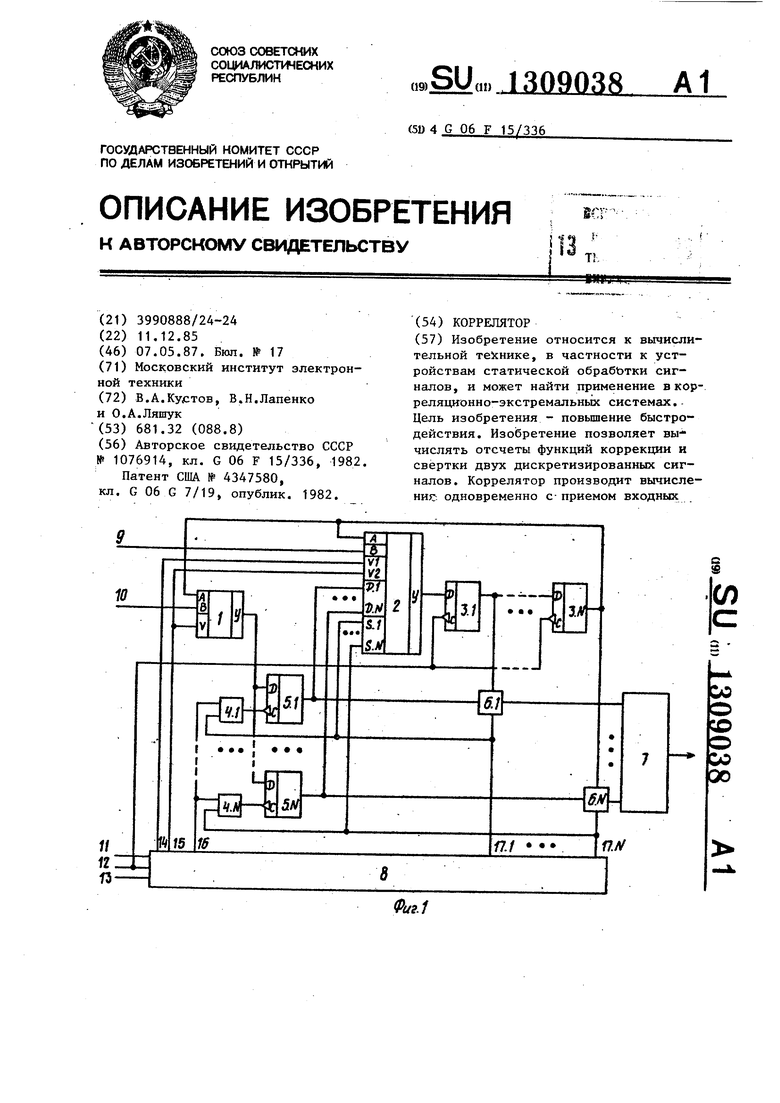

На фиг.1 представлена структурная схема коррелятора{ на фиг.2 - структурная схема блока синхрониза- ции на фиг.3 - структурная схема коммутатора сигналaf на фиг.4 -структурная временная диаграмма работы коррелятора в режиме вычисления свертки J на фиг.5 - временная диаграмма работы коррелятора в режиме перезаписи исходных данных и вьгаисления корреляции.

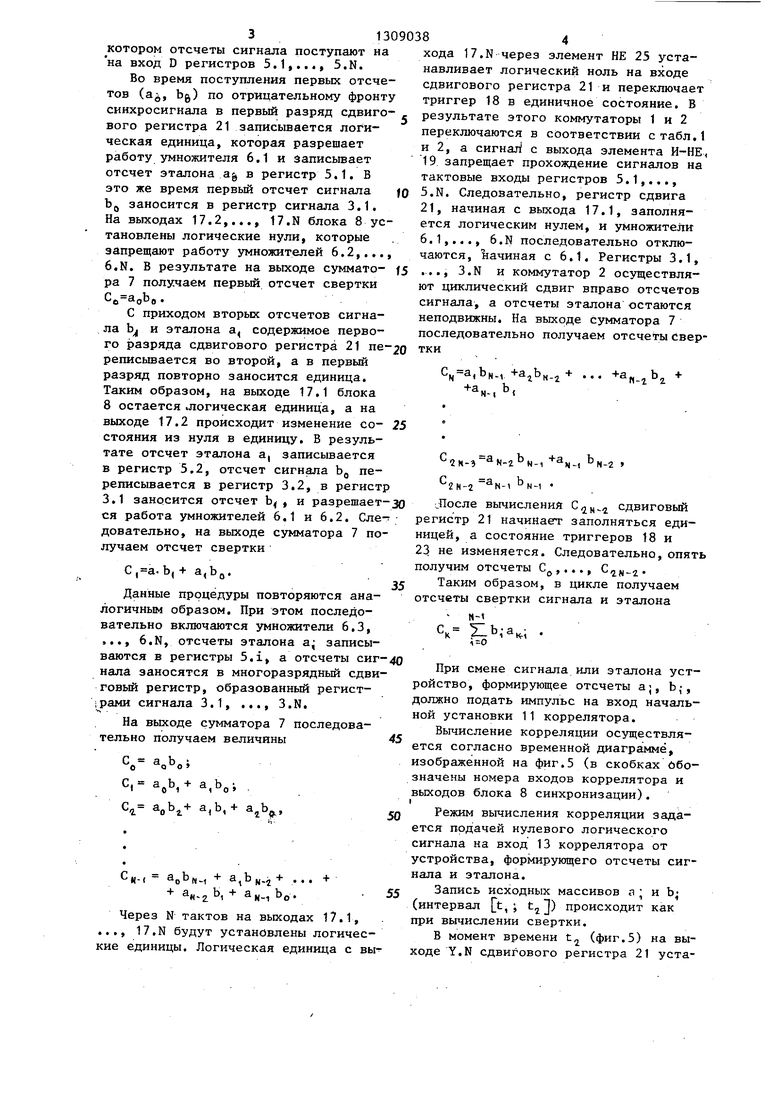

Коррелятор (фиг.1) содержит коммутатор 1 эталона, коммутатор 2 сигнала, регистры 3.1, ..., 3.N сигнала .элементы И 4.1, ..., 4.N, регистры 5.1,..., 5.N эталона, умножители 6,1, ..., 6.N, сумматор 7, блок 8 синхрониза-ции, входы 9 и 10 сигнала и эталона соответственно, входы 11- 13 - начальной установки, тактовый и задания режима работы соответственно, 14, 15, 16, 17.1,..., 17.N - выходы блока 8 синхронизации.

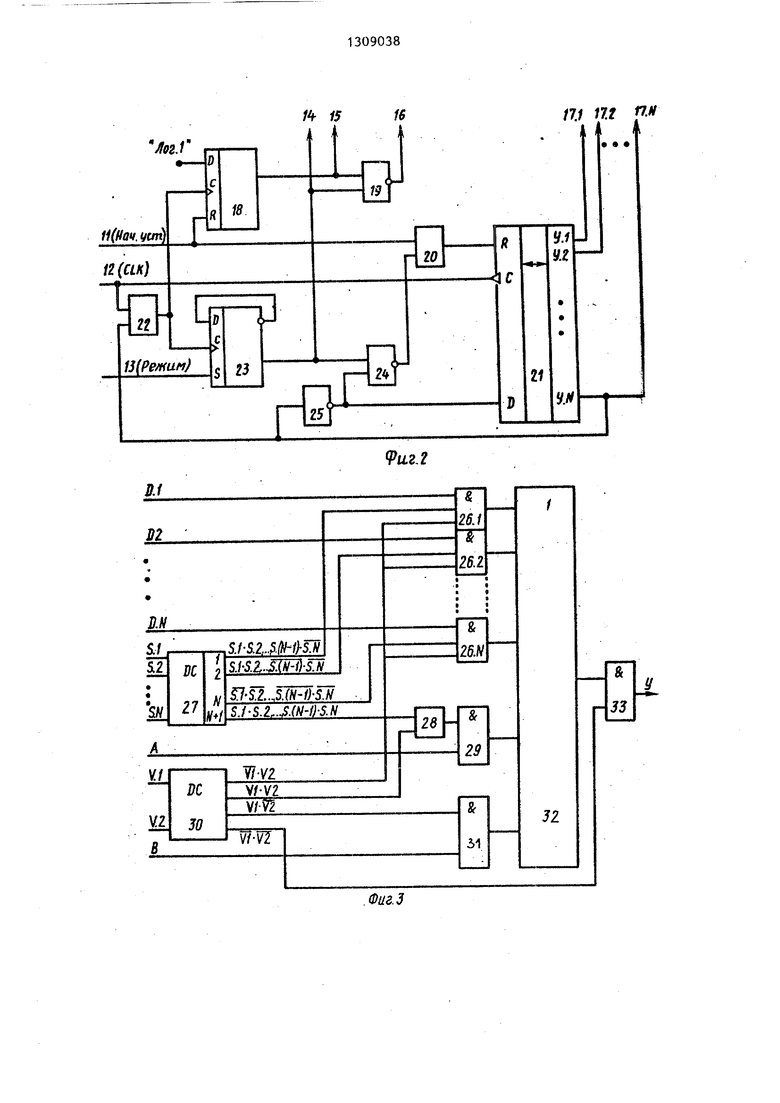

Блок 8 синхронизации (фиг.2) содержит триггер 18, элемент И-НЕ 19, элемент ИЛИ 20, сдвиговый регистр 21, элемент И 22, триггер 23, элемент 24 и элемент НЕ 25.

Коммутатрр сигнала 2 (фиг.З) содержит элементы И 26.1, ..., 26,N, первый дешифратор 27, элемент ИЛИ 28 .первый элемент И 29, второй дешифратор 30, второй элемент И 31, много- входовьм элемент ИЛИ 32 и третий элемент И 33.

Режимы работы коммутатора 1 эталона и лсоммутатора 2 сигнала показаны 45 в табл.1 и 2 соответственно.

умножители 6, сумматор 7, блок 8 синхронизации, информационные входы 9, 10, входы 11, 12, 13 - начальной установки, тактовый и задания режима работы соответственно. 5 ил, 2 таЬл.

5

0

5

0

5

0

5

Таким образом, получаем зависимость выходного сигнала от входных: для коммутатора 1 эталона

Y V А + V . Б

для коммутатора 2 сигнала

V2 B+(V1 V2+vl .V2. S 2. ....

S) A+V1 V2(S/1,S.2,...,S NiD-.N+S:1 .5-2:,...,, S.-N D (N-1) S-2,...,S . (N-1) SN-D-D.

.Коррелятор работает в двух режимах: вычисление свертки и вычисление корреляции сигнала и эталона, представленных N отсчетами.

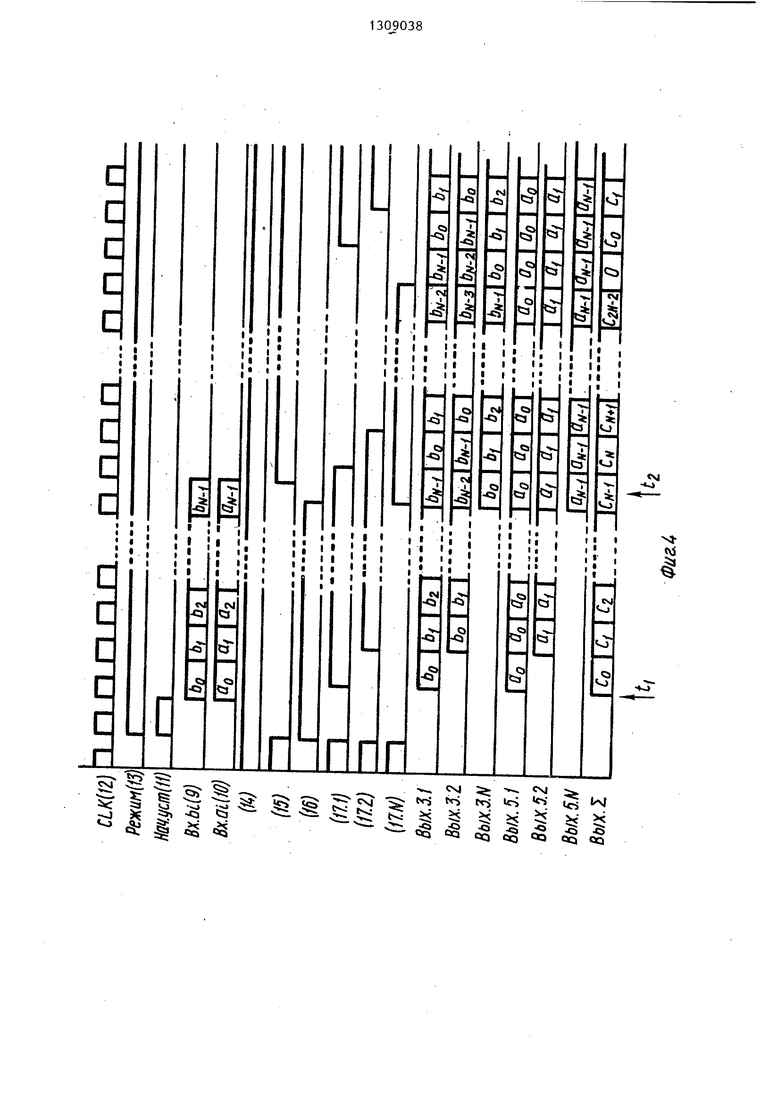

Вычисление свертки происходит согласно временной диаграмме, изображенной на фиг.4, при этом в скобках - обозначены номера входов Коррелятора и выходов блока 8 синхронизадаи.

Сигналы начальной установки (вход 11) и режима (вход 13), поступление отсчетов сигнала и эталона, а также коммутации внутри коррелятора тактированы синхросигналами, поступающими на вход 12 коррелятора.

Режим вычисления свертки задается . подачей единичного логического сигнала на вход 13 коррелятора, который блокирует триггер 23 в единичном состояний.

Перед выдачей отсчетов сигнала и эталона устройство, формирующее эти отсчеты, посылает на вход 11 начальной установки импульс с целью обнуления триггера 18 и сдвигового регистра 21. После окончания сигнала начальной установки на входы 9 и 10 поступают отсчеты сигналов Ь(,1, ..., N-1) и эталона aj (,1,...-, N-1). В соответствии с сигналами на выходах блока 8 (фиг.4 и табл.1 и 2), коммутатор 1 эталона, и коммутатор 2 сигнала находятся в состоянии, при

котором отсчеты сигнала поступают на на вход D регистров 5,1,..., 5.N.

Во время поступления первых отсчетов (а, bg) по отрицательному фронту синхросигнала в первый разряд сдвиго- вого регистра 21 записывается логическая единица, которая разрешает работу умножителя 6.1 и записывает отсчет эталона а в регистр 5.1. Б это же время первый отсчет сигнала Ьд заносится в регистр сигнала 3.1. На выходах 17.2,..., 17.N блока 8 установлены логические нули, которые запрещают работу умножителей 6.2,..., 6.N. В результате на выходе суммато- ра 7 получаем первый отсчет свертки .

С приходом вторых отсчетов сигнала bj и эталона а содержимое первого разряда сдвигового регистра 21 переписьшается во второй, а в первый разряд повторно заносится единица. Таким образом, на выходе 17.1 блока 8 остается .логическая единица, а на выходе 17.2 происходит изменение со- стояния из нуля в единицу. В результате отсчет эталона а, записьшается в регистр 5.2, отсчет сигнала Ь переписывается в регистр 3.2, в регистр 3.1 заносится отсчет Ь, и разрешается работа умножителей 6.1 и 6.2. Следовательно, на выходе сумматора 7 получаем отсчет свертки

С |-а. Ь( .

Данные процедуры повторяются аналогичным образом. При этом последовательно включаются умножители 6.3, ,.., 6.N, отсчеты эталона а записываются в регистры 5.1, а отсчеты сигнала заносятся в многоразрядный сдвиговый регистр, образованный регист- ;рами сигнала 3.1, ..., 3.N.

На выходе сумматора 7 последовательно получаем величины

С

С, ,+ а,Ь„1 . Сг а, а,Ь,+ ,

1|-( N.J + . . . + « 2 1 «-1 О

Через N тактов на выходах 17.1, ..., 17.N будут установлены логические единицы. Логическая единица с выхода 17.N через элемент НЕ 25 устанавливает логический ноль на входе сдвигового регистра 21 и переключает триггер 18 в единичное состояние. В результате этого коммутаторы 1 и 2 переключаются в соответствии с табл.1 и 2, а сигнал с выхода элемента И-НЕ, 19 запрещает прохождение сигналов на тактовые входы регистров 5.1,..., 5.N. Следовательно, регистр сдвига 21, начиная с выхода 17.1, заполняется логическим нулем, и умножители 6.1,..., 6.N последовательно отключаются, Начиная с 6.1. Регистры 3.1, ..., 3.N и коммутатор 2 осзтществля- ют циклический сдвиг вправо отсчетов сигнала, а отсчеты эталона остаются неподвижны. На выходе сумматора 7 последовательно получаем отсчеты свертки

,Ьм., +а,Ь„. +

,

... +а„.,Ь +

, bf,-2

Г я h

г N-2 N-1 N-1

Досле вычисления С,ц сдвиговый регистр 21 начинает заполняться единицей, а состояние триггеров 18 и 23 не изменяется. Следовательно, опять получим отсчеты С,...,

Таким образом, в цикле получаем отсчеты свертки сигнала и эталона

N- С, 1:Ь, .

-0

При смене сигнала или эталона устройство, формирующее отсчеты а;, Ь;, должно подать импульс на вход начальной установки 11 коррелятора.

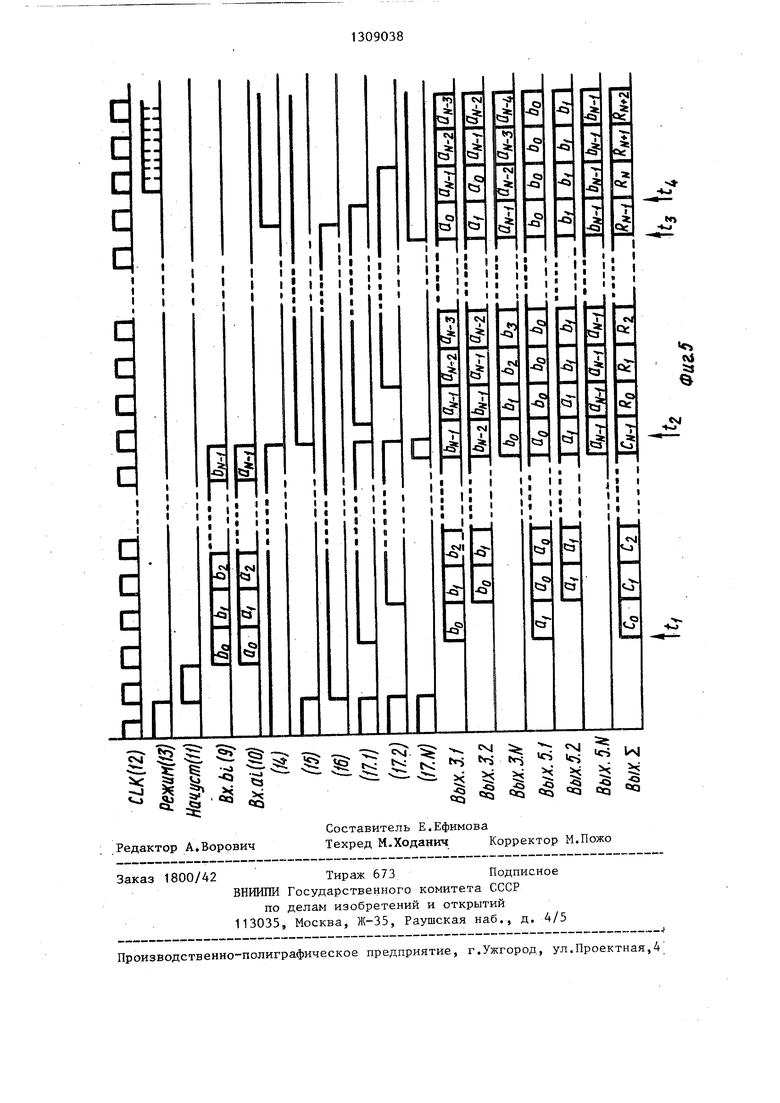

Вычисление корреляции осуществляется согласно временной диаграмме, изображенной на фиг.5 (в скобках ибо- значены номера входов коррелятора и выходов блока 8 синхронизации).

Режим вычисления корреляции задается подачей нулевого логического сигнала на вход 13 коррелятора от устройства, формирующего отсчеты сигнала и эталона.

Запись исходных массивов п и Ь (интервал t,; tjР происходит как при вычислении свертки.

В момент времени t (фиг.5) на выходе Y.N сдвигового регистра 21 уста513

.новлена логическая единица, которая стробирует элемент И 22. Вследствие этого по переднему фронту синхросигнала происходит переключение триггера 18 в единичное состояние, а триг- гера 23 - в нулевое состояние, что в свою очередь вызовет обнуление сдви- гового регистра 21 и переключение коммутаторов сигнала и эталона в со- ответдтвии с табл.1 и 2. В результа- те отсчеты сигнала bj переписываются в регис тры 5,1, а отсчеты эталона в регистры 3.1, ..., 3.N. При этом получаем результат как на интервале .( г (фиг.4) в случае, если бы на вход 9 подать отсчеты эталона а , а на вход 10 - отсчеты сигнала Ь ; . Следовательно, в интервале t, Ц (фиг.5) на выходе сумматора 7.получим отсчеты корреляции сигнала и эталона

RN-, Ь„а„ + Ь,а, +

+ Н-,-1

в момент времени tj (фиг.5) на выходах 17.1 17.N устанавливаются

логические единицы. Логическая единица с выхода 17.N через элемент НЕ 25 устанавливает логический ноль на входе сдвигового регистра 21 и переключает триггер 23 в единичное состояс- ние. По регистру 21 сдвига, начиная с выхода 17,1, распространяется логический ноль, умножители 6.1,..., 6.N последовательно отключаются, начиная с 6.1. Регистры 3.1,...,3.N и коммутатор 2 осуществляют циклический сдвиг вправо отсчетов эталона а, а отсчеты сигнала в регистрах 5.1,..., 5.N остаются неподвижны.

Аналогично вычислению свертки на выходе сумматора последовательно получаем отсчеты корреляции

R.

b,a,f b,a,+

b(j., а,, ,

R R,

г«-з н-2 0 + b., а,.

Ьи-, оЧм-г

В интервале времени от t (фиг.5) момента вычисления Rii.-j необходимо установить логическую единицу на входе 13. В результате после вычисления сдвиговом регистре 21 начинает:распространяться единица, а состояние триггеров 18 и 23 не изменяется. Следовательно, опять получим отсчеты Rg, ..., ,2

Таким образом, в цикле получаем отсчеты корреляции сигнала и эталона

Н-1 RK .

При вычислении свертки и корреляции одних и тех же массивов сигнала и эталона сначаша вычисляют свертку, затем устанавливают логический ноль на входе 13 реяоша и вычисляют корреляцию. Повторная подача нуля на вход 13 режима после вычисления R . восстанавливает режим вычисления свертки.

Вычисление автокорреляции (авто- свертки) осуществляется при закоро- ченных входах 9 и 10.

Формула изобретения

5

Коррелятор, содержащий коммутатор эталона, N последовательно соединенных регистров сигнала, N регистров эталона, N умножителей, N элементов ; И, сумматор, выход которого является) :выходом коррелятора, каждый i-й ( 1,2,...,N) информационный вход сумматора соединен с выходом соответствующего i-ro умножителя, первые входы всех умножителей подключены к выходу соответствующего регистра сиг-

нада, вторые входы умножителей подключены к выходу соответствующего регистра эталона, первый информационный вход коммутатора эталона является первьм информационным входом корс релятора, отличающийся тем, что, с целью повышения быстродействия, в него введены коммутатор сигнала и блок синхронизации, первый, второй и треткй входы которого являются входами начальной установки, тактовым и задания режима работы коррелятора соответственно, синхро- входы регистров сигнала соединены с вторьм входом блока синхронизации,

е информационный вход первого регистра сигнала подключен к выходу коммутатора сигнала, i-й информационный вход группы которого соединен с вьссодом i-ro регистра эталона, i-й вход уп0

713090388

равления группы коммутатора сигналавьйсодом 5лока синхронизации, шестой

соединен с первым входом i-ro элемен-выход которого подключен к третьему

та И, с третьим входом i-ro умножите-управляющему входу коммутатора эталя и подключен к i-му выходу группылона и к (Н+2)-му управляющему входу

выходов блока синхронизации, четвер- 5коммутатора сигнала, тый выход которого соединен с вторыми входами всех элементов И, выход i-ro

элемента И подключен к синхровходуТ а б л и ц а 1

i-ro регистра эталона, информацион-,.,.;

|ные входы всех регистров эталона сое-«О ,вход управления Г Сигнал на вьжодГ

динены с выходом коммутатора эталона,; 1

второй информационный вход которого

подключен к выходу N-fo регистра сиг- уY

нала и к ()-My инфомационному

входу коммутатора сигнала, (К+2)-й 5 Q

информационный вход которого являетВ

ся вторым информационным входом коррелятора, а (Ы+1)-й управляющий вход коммутатора сигнала соединен с пятым,

О 1

11

- любое состояние

В

Таблица 2

...00

D. (N-i)

Риг.2

.Фиг.З

Редактор А Ворович

Составитель Е.Ефимова Техред М.Ходанич

Заказ 1800/42Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор М.Пожо

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1988 |

|

SU1564645A1 |

| Устройство для цифровой обработки сигналов | 1989 |

|

SU1652981A1 |

| Устройство для цифровой фильтрации | 1987 |

|

SU1499374A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОЦЕНКИ ЛОКАЛЬНОГО СРЕДНЕГО ЗНАЧЕНИЯ СТРУКТУРНЫХ СИГНАЛОВ | 1990 |

|

RU2030786C1 |

| Устройство для вычисления свертки | 1989 |

|

SU1688259A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| Цифровой фильтр | 1988 |

|

SU1584084A2 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1989 |

|

SU1619299A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460225C1 |

| Устройство для вычисления преобразования Фурье-Галуа | 1989 |

|

SU1665385A1 |

Изобретение относится к вычислительной технике, в частности к устройствам статической обрабЬтки сигналов, и может найти применение в корреляционно-экстремальных системах. Цель изобретения - повышение быстродействия. Изобретение позволяет вычислять отсчеты функций коррекции и свертки двух дискретизированных сигналов. Коррелятор производит вычисление одновременно с- приемом входных САЭ О Ф О DO 00

| Цифровой коррелятор | 1982 |

|

SU1076914A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4347580, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-11—Подача