Изобретение относится к вычислительной технике, предназначено для вычисления отсчетов функций корреляции и свертки двух дискретизирован- ных сигналов и может найти применение в корреляционно-экстремальных системах.

Цель изобретения - попышение точности.

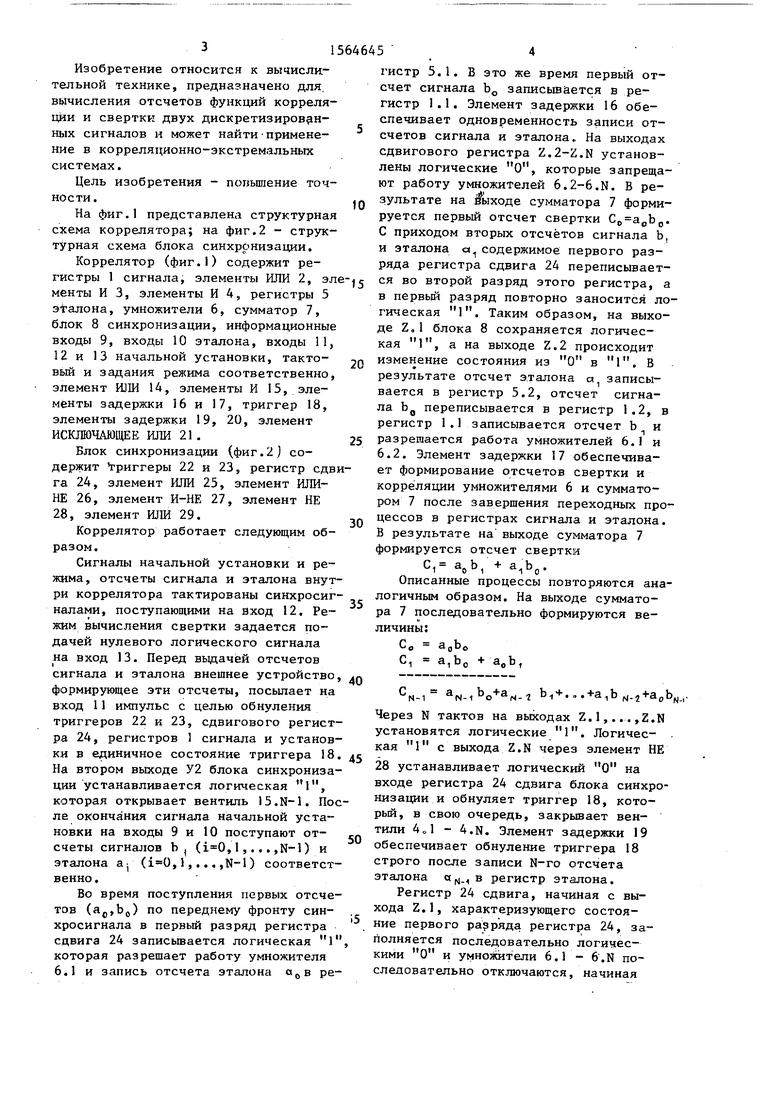

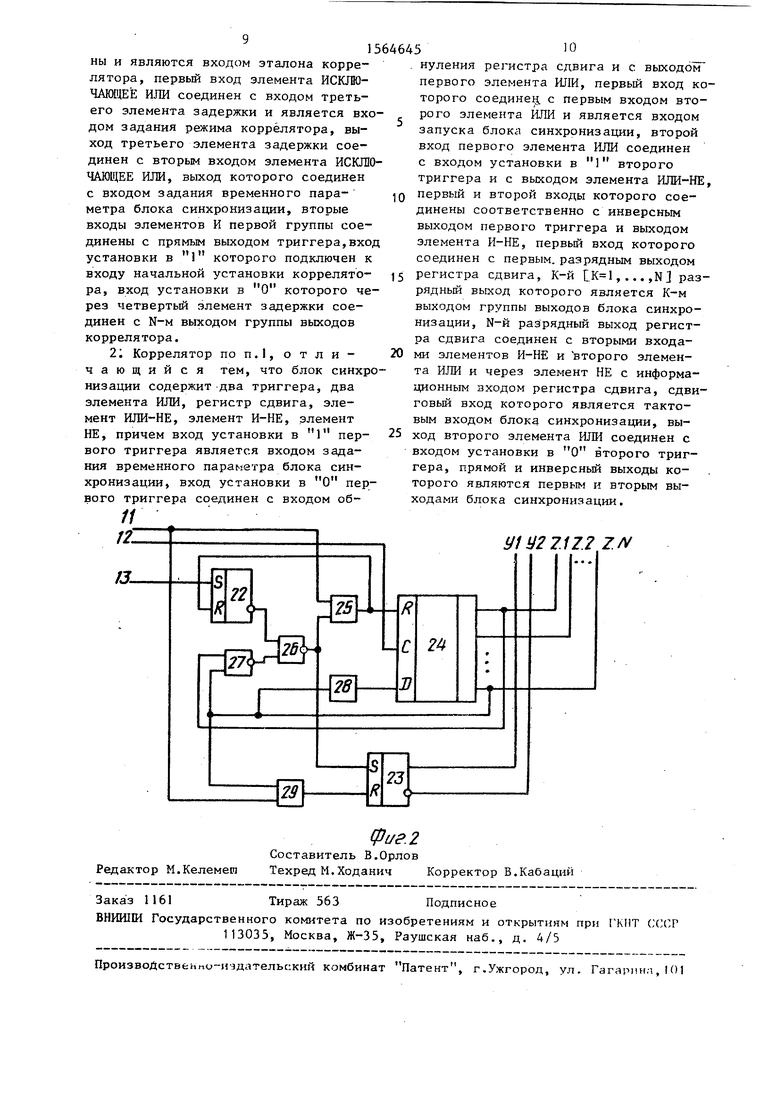

На фиг.1 представлена структурная схема коррелятора; на фиг.2 - структурная схема блока синхронизации.

Коррелятор (фиг.1) содержит ре

гистр 5.1. В это же время первый отсчет сигнала Ь0 записывается в регистр 1.1. Элемент задержки 16 обеспечивает одновременность записи отсчетов сигнала и эталона., На выходах сдвигового регистра Z.2-Z.N установлены логические О, которые запрещают работу умножителей 6.2-6.N. В результате на выходе сумматора 7 формируется первый отсчет свертки . С приходом вторых отсчётов сигнала Ь, и эталона о1 содержимое первого разряда регистра сдвига 24 переписывает

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1985 |

|

SU1309038A1 |

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| Цифровой коррелятор | 1986 |

|

SU1328825A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Цифровой коррелятор | 1989 |

|

SU1711181A1 |

| Адаптивный цифровой фильтр | 1986 |

|

SU1387173A1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1997 |

|

RU2127954C1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1439619A1 |

Изобретение относится к вычислительной технике, в частности к устройствам статистической обработки сигналов. Цель изобретения - повышение точности. Коррелятор содержит регистры сигнала 1 и эталона 5, элементы И 3,4,15 блок 8 синхронизации, элемент ИЛИ 14, умножители 6, сумматор 7. Элементы 16,17,19,20 задержки, триггер 18, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 21. Изобретение позволяет неоднократно переходить из режима вычисления свертки к вычислению корреляции и обратно, не требуя дополнительной синхронизации управляющего сигнала. 1 з.п.ф-лы, 2 ил.

гистры I сигнала, элементы ИЛИ 2, эле- ся во второй разряд этого регистра, а

20

30

35

менты И 3, элементы И 4, регистры 5 эталона, умножители 6, сумматор 7, блок 8 синхронизации, информационные входы 9, входы 10 эталона, входы 11, 12 и 13 начальной установки, тактовый и задания режима соответственно, элемент ИЛИ 14, элементы И 15, элементы задержки 16 и 17, триггер 18, элементы задержки 19, 20, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 21 .25

Блок синхронизации (фиг.2 ) содержит триггеры 22 и 23, регистр сдвига 24, элемент ИЛИ 25, элемент ИЛИ- НЕ 26, элемент И-НЕ 27, элемент НЕ 28, элемент ШШ 29.

Коррелятор работает следующим образом.

Сигналы начальной установки и режима, отсчеты сигнала и эталона внутри коррелятора тактированы синхросигналами, поступающими на вход 12. Режим вычисления свертки задается подачей нулевого логического сигнала на вход 13. Перед выдачей отсчетов сигнала и эталона внешнее устройство, Q формирующее эти отсчеты, посылает на вход 11 импульс с целью обнуления триггеров 22 и 23, сдвигового регистра 24, регистров 1 сигнала и установки в единичное состояние триггера 18. Д5 На втором выходе У2 блока синхронизации устанавливается логическая 1, которая открывает вентиль 15.N-1. После окончания сигнала начальной установки на входы 9 и 10 поступают от- CQ счеты сигналов Ь{ (,1,.,.,N-1) и эталона а (,1,...,N-1) соответственно.

Во время поступления первых отсчетов (а0,Ь0) по переднему фронту синхросигнала в первый разряд регистра сдвига 24 записывается логическая 1, которая разрешает работу умножителя 6.1 и запись отсчета эталона а0в ре15

в первый разряд повторно заносится логическая 1. Таким образом, на выходе Z, 1 блока 8 сохраняется логическая 1, а на выходе Z.2 происходит изменение состояния из О в 1. В

результате отсчет эталона а записывается в регистр 5.2, отсчет сигнала bfl переписывается в регистр 1.2, в регистр 1.1 записывается отсчет b и разрешается работа умножителей 6.1 и 6.2. Элемент задержки 17 обеспечивает формирование отсчетов свертки и корреляции умножителями 6 и сумматором 7 после завершения переходных процессов в регистрах сигнала и эталона. В результате на выходе сумматора 7 формируется отсчет свертки

С,в 0Ь, + iV

Описанные процессы повторяются аналогичным образом. На выходе сумматора 7 последовательно формируются величины:

пЪ0

Со

С, С

а,Ь(

aobf

N-1 аМ-1 1°о+аН-1

bi + ...+a,b rt-2+a0b

Через N тактов на выходах Z.l,...,Z.N установятся логические I. Логическая I с выхода Z.N через элемент НЕ 28 устанавливает логический О на входе регистра 24 сдвига блока синхронизации и обнуляет триггер 18, который, в свою очередь, закрывает вентили 4Л - 4.N. Элемент задержки 19 обеспечивает обнуление триггера 18 строго после записи N-ro отсчета эталона а в регистр эталона.

Регистр 24 сдвига, начиная с выхода Z.1, характеризующего состояние первого разряда регистра 24, заполняется последовательно логическими О и умножители 6.1 - 6.N последовательно отключаются, начиная

в первый разряд повторно заносится логическая 1. Таким образом, на выходе Z, 1 блока 8 сохраняется логическая 1, а на выходе Z.2 происходит изменение состояния из О в 1. В

результате отсчет эталона а записывается в регистр 5.2, отсчет сигнала bfl переписывается в регистр 1.2, в регистр 1.1 записывается отсчет b и разрешается работа умножителей 6.1 и 6.2. Элемент задержки 17 обеспечивает формирование отсчетов свертки и корреляции умножителями 6 и сумматором 7 после завершения переходных процессов в регистрах сигнала и эталона. В результате на выходе сумматора 7 формируется отсчет свертки

С,в 0Ь, + iV

Описанные процессы повторяются аналогичным образом. На выходе сумматора 7 последовательно формируются величины:

пЪ0

Со

bi + ...+a,b rt-2+a0bN,.

Через N тактов на выходах Z.l,...,Z.N установятся логические I. Логическая I с выхода Z.N через элемент НЕ 28 устанавливает логический О на входе регистра 24 сдвига блока синхронизации и обнуляет триггер 18, который, в свою очередь, закрывает вентили 4Л - 4.N. Элемент задержки 19 обеспечивает обнуление триггера 18 строго после записи N-ro отсчета эталона а в регистр эталона.

Регистр 24 сдвига, начиная с выхода Z.1, характеризующего состояние первого разряда регистра 24, заполняется последовательно логическими О и умножители 6.1 - 6.N последовательно отключаются, начиная

с умножителя 6.1. Регистры 1.1 - 1.N через открытый вентиль 15.N-1 осуществляют циклический сдвиг вправо отсчетов сигнала, а отсчеты эталона остаются неподвижны. На выходе сумматора 7 последовательно формируются отсчеты свертки:

,V, +a7bN i+...+aN.1 b,

CtN.3-3pJ-lbN-1 + aN-.1bN-1

1н-г

., bN-l .

После вычисления С.Јгч-7 регистр 24

сдвига вновь начинает заполняться логическими 1 и продолжает осуществляться циклический сдвиг отсчетов сигнала, В результате вновь формируются отсчеты свертки С0, Cf,. . . , Таким образом, в одном цикле формируются отсчеты свертки сигнала и эталона

w-t . С Т b,- a k, .

К

При смене сигнала или эталона устройство, формирующее отсчеты сигнала Ь, и эталона а- , должно сформировать импульс на вход 11 начальной установки.

Вычисление корреляции осуществляется подачей единичного логического сигнала на вход 13 от устройства, формирующего отсчеты сигнала и эталона. При этом изменение логического сигнала на входе 13 с О на 1 устанавливает триггер 22 в единичное сьстояние. Запись исходных массивов с, и Ь- происходит аналогично как при вычислении свертки. В некоторый момент времени на выходе Z.N устанавливается единичный сигнал. Вследствие этого на выходе элемента И-НЕ 27 формируется нулевой сигнал, а на выходах элементов ИЛИ-НЕ 26, ИЛИ 25 устанавливается единичный сигнал, что .приводит к обнулению регистра 24 сдвига и переходу триггера 23 в единичное состояние. Сигнал на выходе Y1 подготавливает срабатывание элементов И 15.1 - 15.N-2. С момента времени начинается вычисление корреляции. Появление логических / на выходах Z.I - Z.N обеспечивает поочередное включение умножителей. При этом в первых i регистрах сигнала посредством поочередного открытия на один такт одного из вентилей 15.1 - 15.N-2 происходит частичный цикличес0

5

кий сдвиг информации. Элемент 15.i (i l-(N-2)) открывается при установке на (1+1)-м и (1+2)-м выходах группы блока синхронизации логических 1 и О соответственно. Одновременно логическая 1 с (i+l)-ro выхода группы блока синхронизации проходит через элемент ИЛИ 2.1 и открывает элемент ИЗ. Таким образом, тактовый импульс, появляющийся на входе 12 устройства, через интервал задержки Ј , определяемой элементом 16, поступает на вход синхронизации первых регистров сигнала, в которых происходит частичный циклический сдвиг вправо. В результате в первых i регистрах сигнала образуется обратная последовательность отсчетов сигнала b N..,- , , b K 1 ,. . . ,b Nи , Следовательно, на выходе сумматора 7 получаем последовательно отсчеты корреляции:

RO

anb

Ы-1

25

R,

a0bN.i +a,bN,

5

0

, а на втором выходе Y2 - логичесП i И ч

RN i a0b0+a1b- +...+aN abM,

На выходе Z.N устанавливается логическая l.j которая обнуляет триггер . 0 23.На первом выходе Yl блока синхронизации устанавливается логический О

кая I, которая открывает вентили элементов И 15.N-1 и 3.N-1. В результате происходит полный циклический одноразрядный сдвиг информации вправо и в регистре сигнала образуется обратная последовательность отсчетов Ъв, b,,..., Ь.,. На выходе сумматора 7 формируется очередной отсчет корреляции

RN-,-a.

:,Ь0 +

а,Ь

+...а,

5

0

5

N-i u NH

Нулевой сигнал на выходе Y1 запирает вентили элементов И 15.1 - 15.N-2 и тем самым запрещает в дальнейшем частичные циклические сдвиги в регистрах сигнала, но через открытый вентиль 15.N-1 в регистрах 1.1 - 1.N в процессе поступления тактовых импульсов осуществляется циклический сдвиг вправо. На выходе сумматора 7 аналогично вычислению свертки формируются отсчеты корреляции

RN a1bo+a7b1+...-(-aN-,

R

1N-3

aN-lb°+a N-1 Ь1

R i M-I aN, b,

После вычисления отсчета R сдвиговый регистр 24 вновь начинает заполняться логическими 1 и осуществляется дальнейший циклический сдвиг отсчетов сигнала. Следовательно, вновь формируются отсчеты корреляции R0,R(,. .. ,R . Таким образом, в цикле получаем отсчеты корреляции сигнала и эталона

10

R,

N-1

Т

Ь, а N

При необходимости повторного возвращения к вычислению свертки этих же массивов в произвольный момент времени подается сигнал логический О на вход 13. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 21 импульсом с длительностью 2 о, где f гс - длительность задержки сигнала элементом задержки 20, установит триггер 22 в единичное состояние. В момент, когда регистр сдвига заполнится логическими

15

I1

отсчеты сигнала установятся в следующей последовательности bQ, b, . . . , b С этого момента в регистрах сигнала начнут осуществляться частичные циклические сдвиги информации аналогично частичным сдвигам при переходе к вычислению корреляции ,

.Таким образом, предложенный коррелятор обеспечивает точное вычисление отсчетов свертки и корреляции для многоразрядных сигналов и позволяет неоднократно переходить из режима вычисления свертки к вычислению корреляции и обратно, не требуя дополнительной синхронизации управляющего сигнала.

Формула изобретения

блок синхронизации, N умножителей и сумматор, вход запуска и тактовый вход блока синхронизации являются соответственно входом начальной установки и тактовым входом коррелятора, выход 1-го (,..,SN-1) регистра сигнала соединен с информационным входом (i+1) то регистра сиг- напа, выходы 1-го регистра сигнала и 1-го регистра эталона соединены соответственно с первым и вторым информационными входами 1-го умножителя, выход которого соединен с i-ым

20

25

15646458

входом сумматора, выход которого является выходом коррелятора, i-и выход группы выходов блока синхрониза-у ции соединен с синхровходом 1-го умножителя и с первым входом i-ro элемента И первой группы, выход которого соединен с синхровходом 1-го регистра эталона, отличающий- с я тем, что, с целью повышения точности, в него дополнительно введены вторая и третья группы элементов И, группа элементов ИЛИ, элемент ИЛИ, четыре элемента задержки, триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход JTO (j l ,. .. ,N-2) элемента И второй группы соединен с первым выходом блока синхронизации, первые входы элементов ИЛИ группы и первый вход (N-l)-ro элемента И второй группы соединены с вторым выходом блока синхронизации, второй вход JTO элемента ИЛИ группы соединен с (j+l)-M выходом группы выходов блока синхронизации, выходы элементов ИЛИ группы соединены с первыми входами соответствующих элементов И третьей группы, вторые входы которых соединены с выходом первого элемента задержки,вход которого подключен к тактовому входу коррелятора, тактовый вход, сумматора через второй элемент задержки соединен с выходом первого элемента задержки, первый вход (N-H)-ro элемента И второй группы соединен с вторым выходом блока синхронизации, выход первого элемента И третьей группы соединен с синхровходами первого и второго регистров сигнала группы, выход 1-го (,..„,N-1) элемента И третьей группы соединен с синхровходом (1+1)-го регистра сигнала, второй вход j-го элемента И второй группы соединен с выходом (j+l)-ro pe- 45 гистра сигнала группы, третий вход JTO элемента И второй группы соединен с (j+l)-M выходом группы выходов блока синхронизации, четвертый инверсный вход j-ro элемента И второй группы соединен с (j+2)-M выходом группы выходов блока синхронизации, выход Мто регистра сигнала группы соединен с вторым входом (N-I)- го элемента И второй группы, выход j-ro элемента И второй группы соединен с j-м входом элемента RJDi,(N+l)u вход которого является информационным входом коррелятора, информационные входы регистров эталона объединеЧ

30

35

40

50

55

У1У27.12.2 Z/V

| Коррелятор | 1985 |

|

SU1309038A1 |

Авторы

Даты

1990-05-15—Публикация

1988-08-29—Подача