Изобретение относится к электронной вычислительной технике и может быть исноль- зовано в качестве устройства формирования импульсов по фронтам входного сигнала с унравлением по длительности.

Целью изобретения является рас1нирение функциональных возможностей устройства, а именно обеснечение электронного дискретного унравления длительностью выходного сигнала нутем введения инвертирующего блока, состоянлего из п параллельно соединенных инвертирующих каскадов, один из входов которых подключен к унравляющей клемме устройства, благодаря чему достигается изменение числа одновременно включенных инвертирующих каскадов при подаче определенной комбинации сигналов на уп- равляюн1ие клеммы устройства, вследствие чего дискретно изменяется задержка сигнала в И1 вертируюи1,ем блоке i;, следовательно, длительность выходного сигнала.

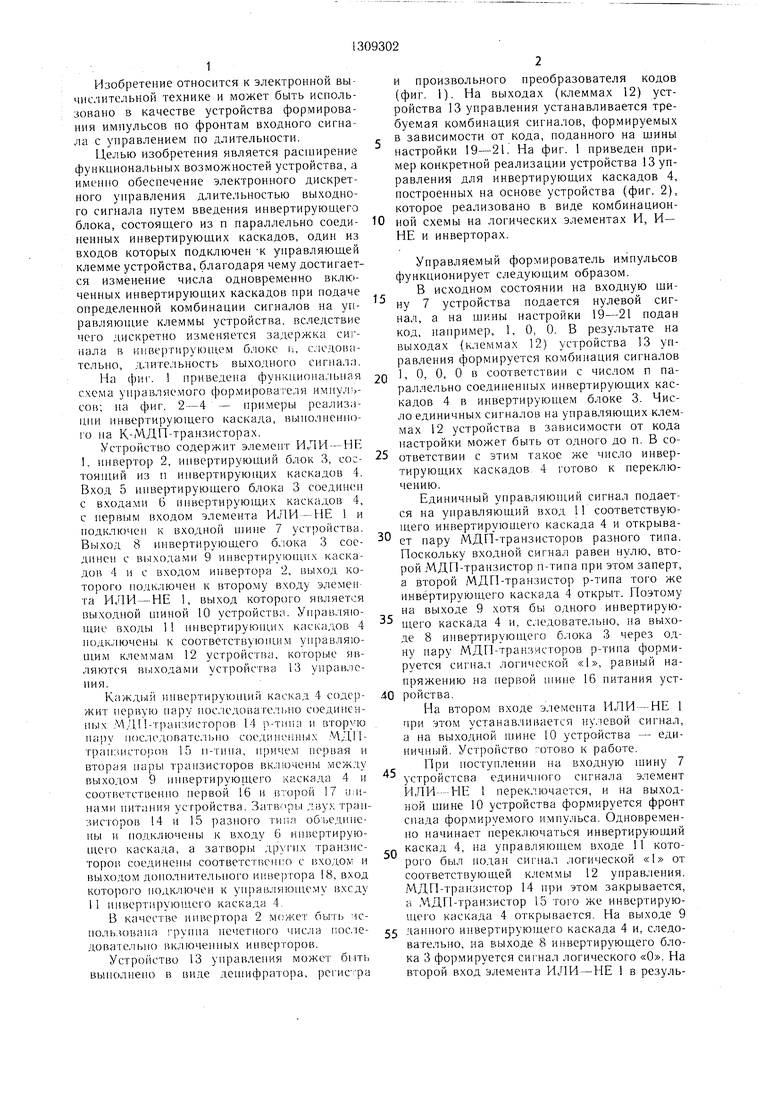

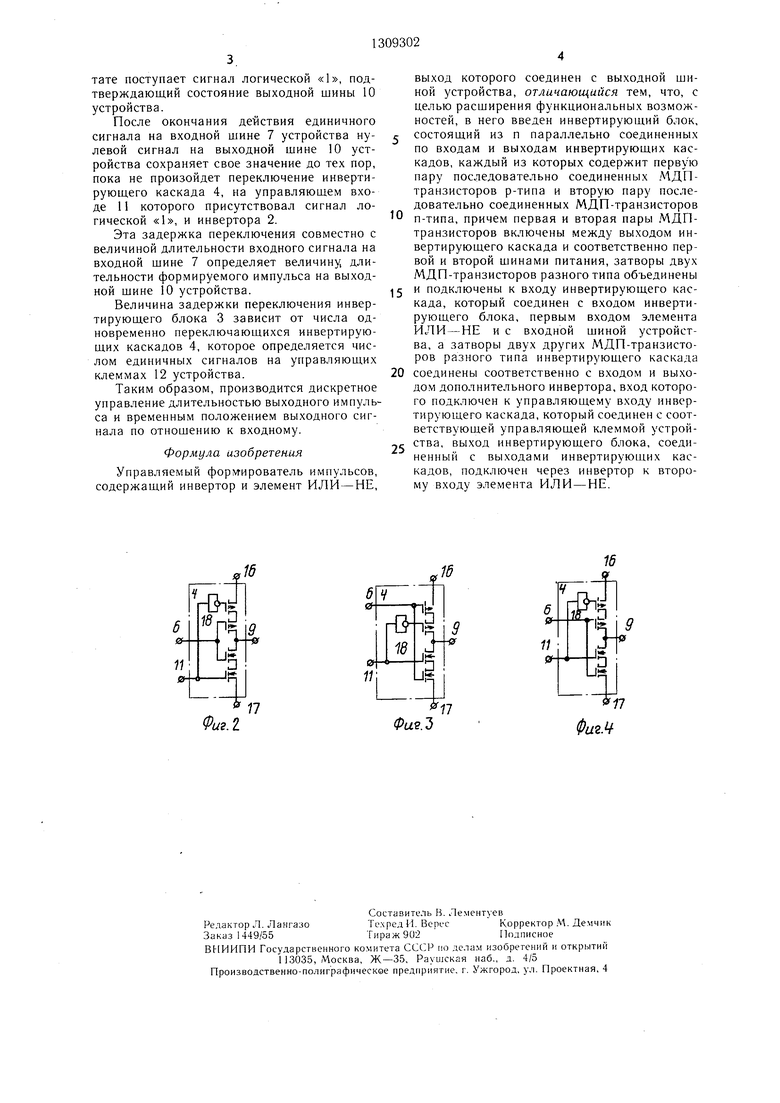

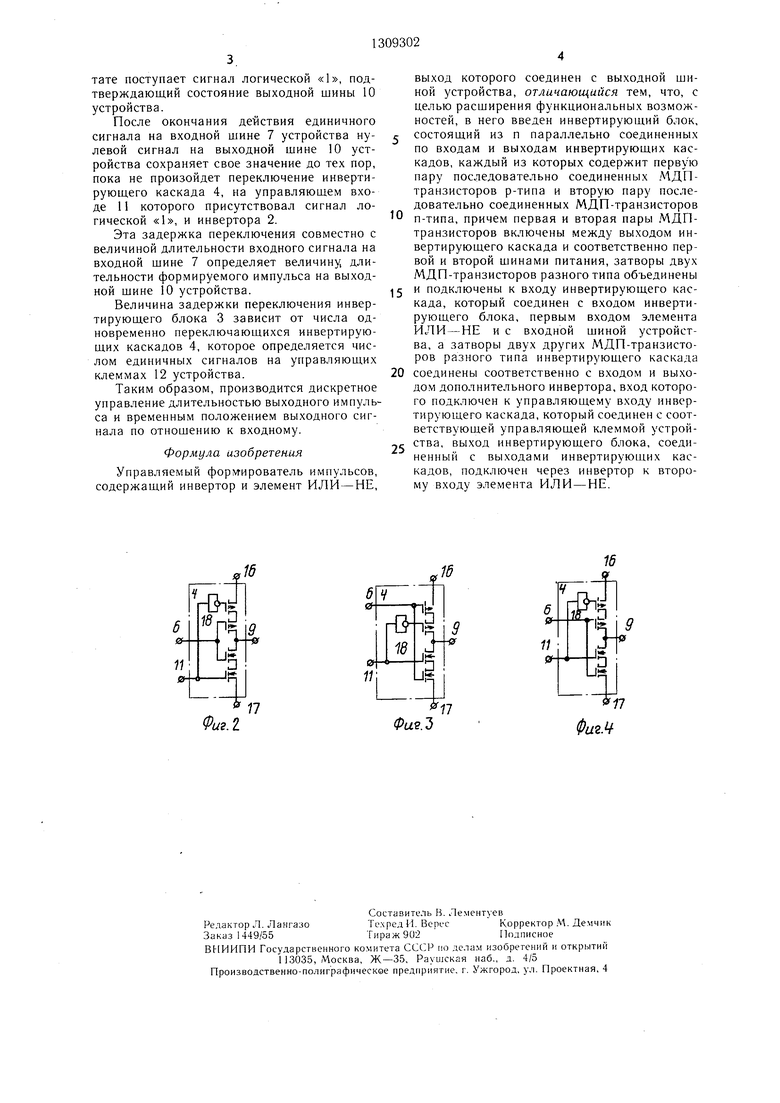

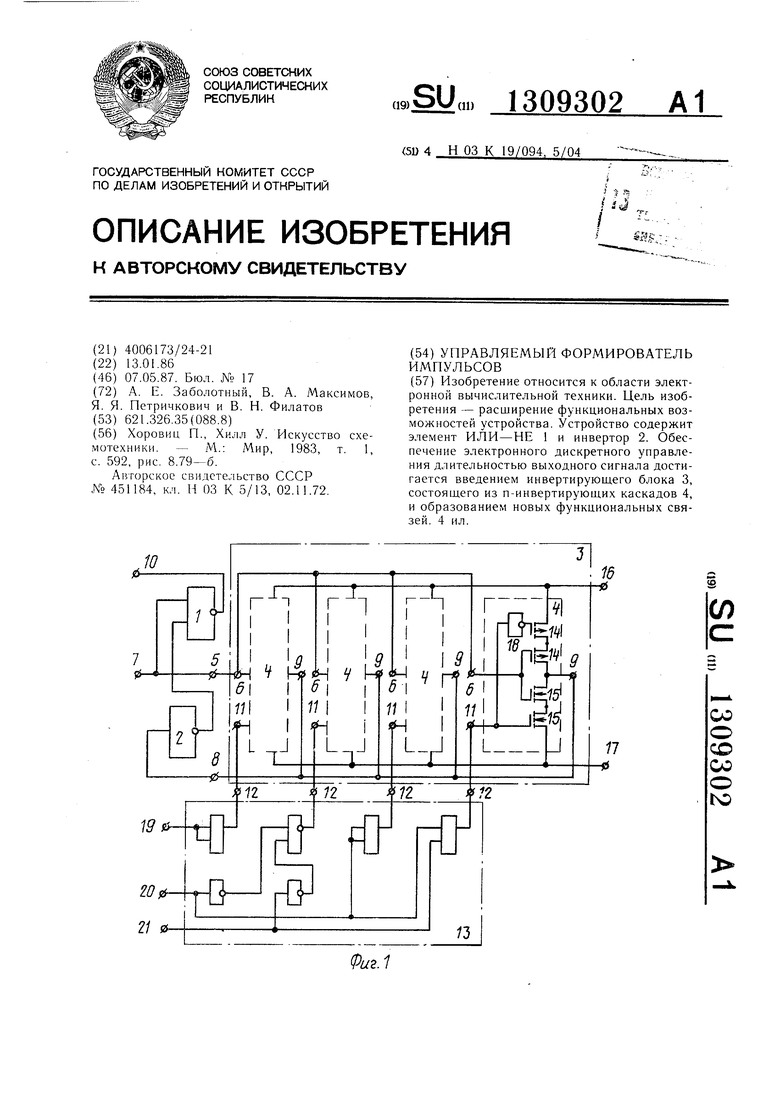

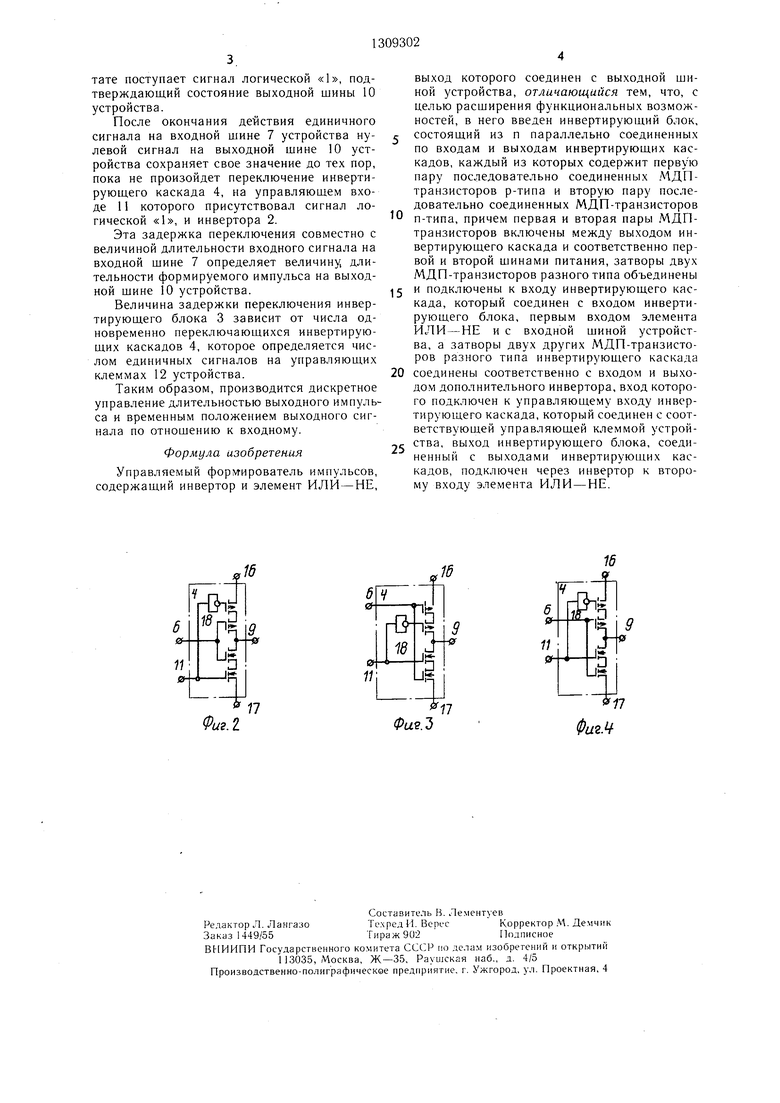

На фиг. 1 приведена функциональная схема управляемого формировагеля имнуль- сов; на фиг. 2-4 - примеры реа.лиза- цни инвертирующего каскада, вынолненно- го на К-МДП-транзисторах.

Устройство содержит элемент ИЛИ - НЕ 1, инвертор 2, инвертирующий блок 3, состоящий из п инвертирующих каскадов 4. Вход 5 инвертирующего блока 3 соединен с входами б инвертируюнщх каскадов 4, с первым входом элемента ИЛИ - НЕ 1 и нодключен к входной 7 устройства. Выход 8 инвертирующего б.юка 3 соединен с выходами 9 инвертирующих каскадов 4 и с входом инвертора 2, выход которого нодключен к второму входу элемен та ИЛИ-НЕ 1, выход которого является выходной тиной 10 устройства. Унравляю- щие входы 11 инвертируюни1х каскадов 4 подключены к соответствующим ун()авляю- щим клеммам 12 устройства, которые являются выходами устройства 13 управления.

Каждый инвертируюни-|й каскад 4 содержит первую пару 1и)с. 1едовагел1 но соедипен- niiix M/U -т 1анзисторов 14 Р-тииа и вторх-ю пару последовательно с()един ,л-:ных .ЧД П- трапзисторон 15 п-тина, причем первая и вторая пары транзисторов включены между выходом 9 ппвертирующего каскада 4 и соответственно первой 16 и второй 17 ;jin- нами питания устройства. Затвпр, д.вух трап- зисторов 14 и 15 разного гипа об ьедгше- ны и подключены к входу 6 и1П ертирую- щего каскада, а затворы друшх транзисторов соединены соответственно с 5ходок и выходом донолнительного инвертора 18, вход кото5)О1-о нодключен к управ.ляюп1ему вхсду П ннвертируюи1его каскада 4.

В качестве liiiBCpTOpa 2 может быть ис- нользована группа нечетного числа iioc/ie- довательпо включеппых инверторов.

Устройство 13 управлепия может быть вьпюлнено в виде деп1ифратора, регисфа

и произвольного преобразователя кодов (фиг. 1). На выходах (клеммах 12) устройства 13 управления устанавливается требуемая комбинация сигиалов, формируемых

в зависимости от кода, поданного на щины настройки 19-21. На фиг. 1 приведен пример конкретной реализации устройства 13 унравления для инвертирующих каскадов 4, ностроенных на основе устройства (фиг. 2), которое реализовано в виде комбинационной схемы на логических элементах И, И- НЕ и инверторах.

Управляемый формирователь импульсов функционирует следующим образом.

В исходном состоянии на входную щи- ну 7 устройства подается нулевой сигнал, а на щины настройки 19-21 подан код, например, 1, О, 0. В результате на выходах (клеммах 12) устройства 13 управления формируется комбинация сигналов 1, О, О, О в соответствии с числом п параллельно соединенных инвертирующих каскадов 4 в инвертирующем блоке 3. Число единичных сигналов на управляющих клеммах 12 устройства в зависимости от кода настройки может быть от одного до п. В соответствии с этим такое же число инвертирующих каскадов. 4 готово к переключению.

Единичный управляюп1ий сигнал подается на унравляющий вход 11 соответствующего инвертируюнхего каскада 4 и открывает пару МДП-транзисторов разного типа. Поскольку входной сигнал равен нулю, второй МДП-транзистор п-типа при этом заперт, а второй МДП-трапзистор р-тина того же инвертирующего каскада 4 открыт. Поэтому на выходе 9 хотя бы одного инвертирующего каскада 4 и, следовательно, на выходе 8 инвертирующе1 о блока 3 через одну пару МДП-транзисторов р-тина формируется сигнал логической «1, равный напряжению на 1ервой тине 16 питания устройства.

На втором входе элемента ИЛИ-НЕ 1 при этом устанавли15ается нулевой сигпал, а на выходной HJHHC 10 устройства - единичный. Устройство отово к работе.

При поступлении на входную тину 7 устройстсва единичного сигнала элемент ИЛИ-НЕ 1 переключается, и на выходной тине 10 устройства формируется фронт спада формируемого имнульса. Одновременно начинает переключаться инвертируюп.1.ий каскад 4, на управляюнгем входе 11 которого был подан си1 пал логической «1 от соответствующей клеммы 12 управления. МДП-транзистор 14 при этом закрывается, а МДП-транзистор 15 того же инвертирую- uiero каскада 4 открывается. На выходе 9

данного инвертирующего каскада 4 и, следовательно, на выходе 8 инвертирующего блока 3 формируется сигнал логического «О. На второй вход элемента ИЛИ -НЕ 1 в резуль

тате поступает сигнал логической «1, подтверждающий состояние выходной шины 10 устройства.

После окончания действия единичного сигнала на входной шине 7 устройства нулевой сигнал на выходной шине 10 устройства сохраняет свое значение до тех пор, пока не произойдет переключение инверти- руюш,его каскада 4, на управляющем входе 11 которого присутствовал сигнал логической «1, и инвертора 2.

Эта задержка переключения совместно с величиной длительности входного сигнала на входной шине 7 определяет величину, длительности формируемого импульса на выходной шине 10 устройства.

Величина задержки переключения инвертирующего блока 3 зависит от числа одновременно переключающихся инвертирующих каскадов 4, которое определяется числом единичных сигналов на управляющих клеммах 12 устройства.

Таким образом, производится дискретное управление длительностью выходного импульса и временным положением выходного сигнала по отношению к входному.

Формула изобретения

Управляемый форм ирователь импульсов, содержащий инвертор и элемент ИЛИ-НЕ,

выход которого соединен с выходной шиной устройства, отличающийся тем, что, с целью расширения функциональных возможностей, в него введен инвертирующий блок,

состоящий из п параллельно соединенных по входам и выходам инвертирующих каскадов, каждый из которых содержит первую пару последовательно соединенных .ИДП- транзисторов р-типа и вторую пару последовательно соединенных МДП-транзисторов

п-типа, причем первая и вторая пары МДП- транзисторов включены между выходом инвертирующего каскада и соответственно первой и второй щинами питания, затворы двух МДП-транзисторов разного типа объединены

и подключены к входу инвертирующего каскада, который соединен с входом инвертирующего блока, первым входом элемента ИЛИ - НЕ и с входной шиной устройства, а затворы двух других МДП-транзисторов разного типа инвертирующего каскада

соединены соответственно с входом и выходом дополнительного инвертора, вход которого подключен к управляющему входу инвертирующего каскада, который соединен с соответствующей управляющей клеммой устройства, выход инвертирующего блока, соединенный с выходами инвертирующих каскадов, подключен через инвертор к второму входу элемента ИЛИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2515225C1 |

| Ключевой элемент | 1986 |

|

SU1327283A1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Выходное устройство с тремя состояниями на КМДП-транзисторах | 1988 |

|

SU1539994A1 |

| Ключевой элемент | 1986 |

|

SU1322460A1 |

| Компаратор | 1989 |

|

SU1690184A1 |

| Ключевой элемент на МДП-транзисторах | 1988 |

|

SU1497738A1 |

| Логический элемент И | 1981 |

|

SU951707A1 |

| Устройство реверсирования тока | 1985 |

|

SU1246359A1 |

Изобретение относится к области электронной вычислительной техники. Цель изобретения - расширение функциональных возможностей устройства. Устройство содержит элемент ИЛИ-НЕ 1 и инвертор 2. Обеспечение электронного дискретного управления длительностью выходного сигнала достигается введением инвертирующего блока 3, состоящего из п-инвертирующих каскадов 4, и образованием новых функциональных связей. 4 ил.

16

18 гЗ

W

L-|I,

Фиг. 2.

17

ФигМ

| Хоровиц П., Хилл У | |||

| Искусство схе.мотехники | |||

| - М.: Мир, 1983, т | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Телефонная трансляция с катодными лампами | 1920 |

|

SU592A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Формирователь импульсов малой длительности | 1972 |

|

SU451184A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-07—Публикация

1986-01-13—Подача