Изобретение относится к импульсной технике и может быть использовано при построении аналоговых и аналого-цифровых схем на МПД-транзисторах.

Цель изобретения - повышение точности сравнения медленно меняющихся сигналов за счет обеспечения независимости ее от величины зоны нечувствительности.

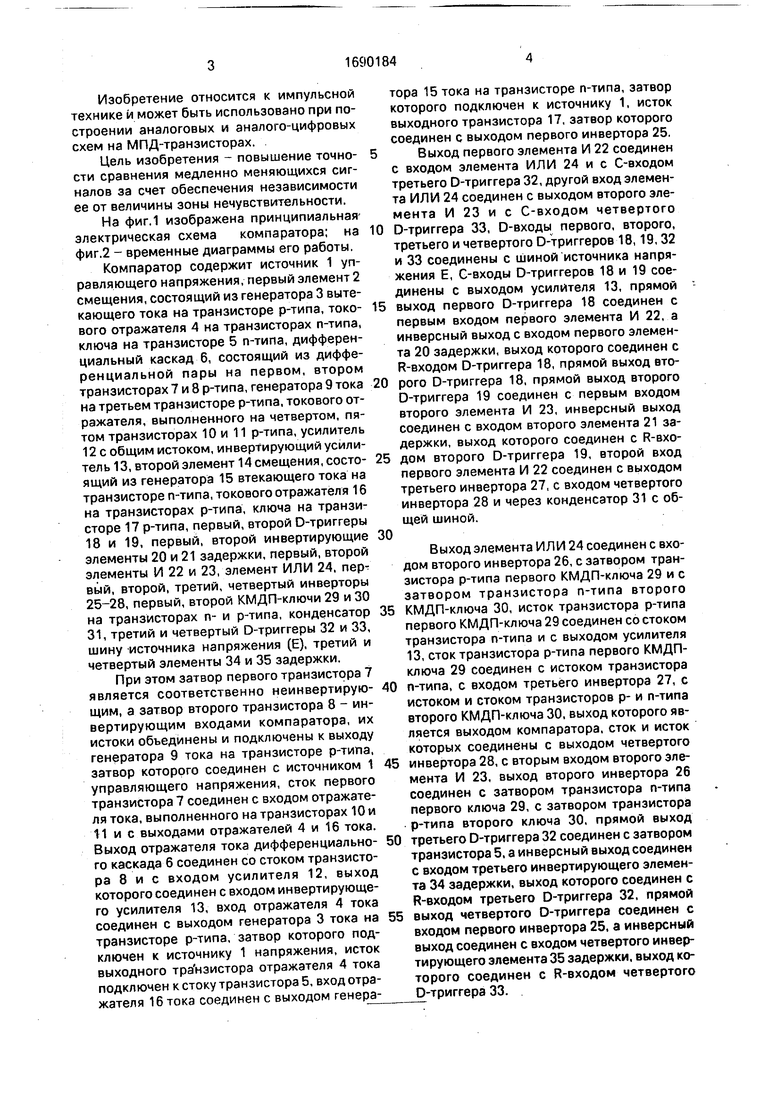

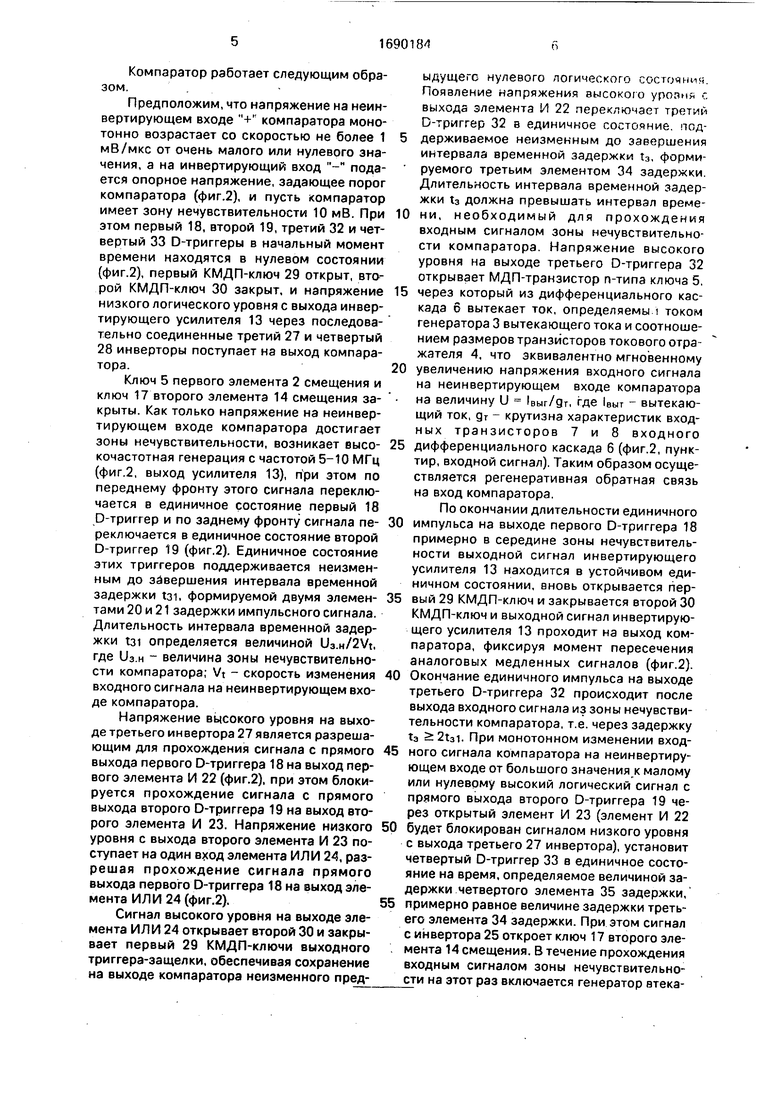

На фиг.1 изображена принципиальная электрическая схема компаратора; на фиг.2 - временные диаграммы его работы.

Компаратор содержит источник 1 управляющего напряжения, первый элемент 2 смещения, состоящий из генератора 3 вытекающего тока на транзисторе р-типа,токового отражателя 4 на транзисторах п-типа, ключа на транзисторе 5 n-типа, дифференциальный каскад 6, состоящий из дифференциальной пары на первом, втором транзисторах 7 и 8 р-типа, генератора 9 тока на третьем транзисторе р-типа, токового отражателя, выполненного на четвертом, пятом транзисторах 10 и 11 р-типа,усилитель 12с общим истоком, инвертирующий усили- тель 13, второй элемент 14 смещения, состо- ящий из генератора 15 втекающего тока на транзисторе n-типа, токового отражателя 16 на транзисторах р-типа, ключа на транзисторе 17 р-типа, первый, второй D-триггеры 18 и 19, первый, второй инвертирующие элементы 20 и 21 задержки, первый, второй элементы И 22 и 23, элемент ИЛИ 24, первый, второй, третий, четвертый инверторы 25-28, первый, второй КМДП-ключи 29 и 30 на транзисторах п- и р-типа, конденсатор 31, третий и четвертый D-триггеры 32 и 33, шину источника напряжения (Е), третий и четвертый элементы 34 и 35 задержки.

При этом затвор первого транзистора 7 является соответственно неинвертирующим, а затвор второго транзистора 8 - инвертирующим входами компаратора, их истоки объединены и подключены к выходу генератора 9 тока на транзисторе р-типа, затвор которого соединен с источником 1 управляющего напряжения, сток первого транзистора 7 соединен с входом отражателя тока, выполненного на транзисторах 10 и tine выходами отражателей 4 и 16 тока. Выход отражателя тока дифференциального каскада 6 соединен со стоком транзистора 8 и с входом усилителя 12, выход которого соединен с входом инвертирующего усилителя 13, вход отражателя 4 тока соединен с выходом генератора 3 тока на транзисторе р-типа, затвор которого подключен к источнику 1 напряжения, исток выходного тра нэистора отражателя 4 тока подключен к стоку транзистора 5, вход отражателя 16 тока соединен с выходом генератора 15 тока на транзисторе n-типа, затвор которого подключен к источнику 1, исток выходного транзистора 17, затвор которого соединен с выходом первого инвертора 25.

Выход первого элемента И 22 соединен

с входом элемента ИЛИ 24 и с С-входом третьего D-триггера 32, другой вход элемента ИЛИ 24 соединен с выходом второго элемента И 23 и с С-входом четвертого

0 D-триггера 33, D-входы первого, второго, третьего и четвертого D-триггеров 18,19,32 и 33 соединены с шиной источника напряжения Е, С-входы D-триггеров 18 и 19 соединены с выходом усилителя 13, прямой

5 выход первого D-триггера 18 соединен с первым входом первого элемента И 22, а инверсный выход с входом первого элемента 20 задержки, выход которого соединен с R-входом D-триггера 18, прямой выход ато0 рого D-триггера 18, прямой выход второго D-триггера 19 соединен с первым входом второго элемента И 23, инверсный выход соединен с входом второго элемента 21 задержки, выход которого соединен с R-вхо5 дом второго D-триггера 19, второй вход первого элемента И 22 соединен с выходом третьего инвертора 27, с входом четвертого инвертора 28 и через конденсатор 31 с общей шиной.

0

Выход элемента ИЛИ 24 соединен с входом второго инвертора 26, с затвором транзистора р-типа первого КМДП-ключа 29 и с затвором транзистора n-типа второго

5 КМДП-ключа 30, исток транзистора р-типа первого КМДП-ключа 29 соединен со стоком транзистора n-типа и с выходом усилителя 13, сток транзистора р-типа первого КМДП- ключа 29 соединен с истоком транзистора

0 n-типа, с входом третьего инвертора 27, с истоком и стоком транзисторов р- и п-типа второго КМДП-ключа 30, выход которого является выходом компаратора, сток и исток которых соединены с выходом четвертого

5 инвертора 28, с вторым входом второго элемента И 23, выход второго инвертора 26 соединен с затвором транзистора п-типа первого ключа 29, с затвором транзистора р-типа второго ключа 30, прямой выход

0 третьего D-триггера 32 соединен с затвором транзистора 5, а инверсный выход соединен с входом третьего инвертирующего элемента 34 задержки, выход которого соединен с R-входом третьего D-триггера 32, прямой

5 выход четвертого D-триггера соединен с входом первого инвертора 25, а инверсный выход соединен с входом четвертого инвертирующего элемента 35 задержки, выход которого соединен с R-входом четвертого D-триггера 33.

Компаратор работает следующим образом

Предположим, что напряжение на неинвертирующем входе + компаратора монотонно возрастает со скоростью не более 1 мВ/мкс от очень малого или нулевого значения, а на инвертирующий вход - подается опорное напряжение, задающее порог компаратора (фиг.2), и пусть компаратор имеет зону нечувствительности 10 мВ. При этом первый 18, второй 19, третий 32 и четвертый 33 D-триггеры в начальный момент времени находятся в нулевом состоянии (фиг.2), первый КМДП-ключ 29 открыт, вта- рой КМДП-ключ 30 закрыт, и напряжение низкого логического уровня с выхода инвертирующего усилителя 13 через последовательно соединенные третий 27 и четвертый 28 инверторы поступает на выход компаратора.

Ключ 5 первого элемента 2 смещения и ключ 17 второго элемента 14 смещения за- крыты. Как только напряжение на неинвертирующем входе компаратора достигает зоны нечувствительности, возникает высо- кочастотная генерация с частотой 5-10 МГц (фиг.2, выход усилителя 13), при этом по переднему фронту этого сигнала переключается в единичное состояние первый 18 D-триггер и по заднему фронту сигнала пе- реключается в единичное состояние второй D-триггер 19 (фиг.2). Единичное состояние этих триггеров поддерживается неизменным до завершения интервала временной задержки tai, формируемой двумя элемен- тами 20 и 21 задержки импульсного сигнала. Длительность интервала временной задержки tai определяется величиной U3.H/2Vt, где Кз и - величина зоны нечувствительности компаратора; Vt - скорость изменения входного сигнала на неинвертирующем входе компаратора.

Напряжение высокого уровня на выходе третьего инвертора 27 является разрешающим для прохождения сигнала с прямого выхода первого D-триггера 18 на выход первого элемента И 22 (фиг.2), при этом блокируется прохождение сигнала с прямого выхода второго D-триггера 19 на выход второго элемента И 23. Напряжение низкого уровня с выхода второго элемента И 23 поступает на один вход элемента ИЛИ 24, разрешая прохождение сигнала прямого выхода первого D-триггера 18 на выход элемента ИЛИ 24 (фиг.2).

Сигнал высокого уровня на выходе элемента ИЛИ 24 открывает второй 30 и закрывает первый 29 КМДП-ключи выходного триггера-защелки, обеспечивая сохранение на выходе компаратора неизменного предыдущего нулевого логического состоя нич Появление напряжения высокою урони - выхода элемента И 22 переключает третий D-триггер 32 в единичное состояние поддерживаемое неизменным до завершения интервала временной задержки t3, формируемого третьим элементом 34 задержки Длительность интервала временной задержки ta должна превышать интервал времени, необходимый для прохождения входным сигналом зоны нечувствительности компаратора Напряжение высокого уровня на выходе третьего D-триггера 32 открывает МДП-транзистор n-типа ключа 5. через который из дифференциального каскада б вытекает ток, определяемы 1 током генератора 3 вытекающего тока и соотношением размеров транзисторов токового отражателя 4, что эквивалентно мгновенному увеличению напряжения входного сигнала на неинвертирующем входе компаратора на величину U выг/дт, где 1выт - вытекающий ток, дт - крутизна характеристик вход- ных транзисторов 7 и 8 входного дифференциального каскада 6 (фиг.2, пунктир, входной сигнал). Таким образом осуществляется регенеративная обратная связь на вход компаратора.

По окончании длительности единичного импульса на выходе первого D-триггера 18 примерно в середине зоны нечувствительности выходной сигнал инвертирующего усилителя 13 находится в устойчивом единичном состоянии, вновь открывается первый 29 КМДП-ключ и закрывается второй 30 КМДП-ключ и выходной сигнал инвертирующего усилителя 13 проходит на выход компаратора, фиксируя момент пересечения аналоговых медленных сигналов (фиг.2). Окончание единичного импульса на выходе третьего D-триггера 32 происходит после выхода входного сигнала из зоны нечувствительности компаратора, т е. через задержку la Э: 2t3i. При монотонном изменении входного сигнала компаратора на неинвертирующем входе от большого значения к малому или нулевому высокий логический сигнал с прямого выхода второго D-триггера 19 через открытый элемент И 23 (элемент И 22 будет блокирован сигналом низкого уровня с выхода третьего 27 инвертора), установит четвертый D-триггер 33 в единичное состояние на время, определяемое величиной задержки четвертого элемента 35 задержки, примерно равное величине задержки третьего элемента 34 задержки. При этом сигнал с инвертора 25 откроет ключ 17 второго элемента 14 смещения. В течение прохождения входным сигналом зоны нечувствительности на этот раз включается генератор втекающего тока, что эквивалентно мгновенному уменьшению входного сигнала на неинвертирующем входе компаратора на величину U - 1вт/9т, где 1Вт - втекающий ток; дт - крутизна характеристик входных транзисторов 7 и 8 (фиг.2, входной сигнал), т.е. осуществляется регенеративная связь, ускоряющая выход компаратора из зоны нечувствительности.

При появлении сигнала высокого уровня на выходе второго элемента И 23 закрывается первый 29 КМДП-ключ и открывается второй 30 КМДП-ключ, при этом выходной триггер-защелка запоминает предыдущее состояние высокого логического уровня. По окончании длительности единичного импульса на прямом выходе второго D-тригге- ра 19, определяемой величиной U3H/2Vt, и, соответственно, на выходе элемента ИЛИ 24 сигнал низкого уровня с выхода инвертирующего усилителя 13 через третий 27 и четвертый 28 инверторы поступает на выход компаратора, тем самым фиксируя момент пересечения аналоговых сигналов. Окончание единичного импульса на выходе четвертого D-триггера 33 произойдет после прохождения входным сигналом зоны нечувствительности компаратора.

Таким образом, за счет временной селекции управления генераторами втекающего, вытекающего тока и выдачи информации с выходного триггера-защелки значительно повышается точность сравнения медленно меняющихся сигналов.

Технический эффект заключается в повышении точности сравнения медленно меняющихся сигналов, которая для описываемого компаратора не зависит от величины зоны нечувствительности.

Формула изобретения Компаратор, выполненный на полевых транзисторах, содержащий источник управляющего напряжения, первый элемент смещения, состоящий из генератора вытекающего тока, отражателя тока и ключа, последовательно соединенные дифференциальный каскад, усилитель с общим истоком и инвертирующий усилитель, шину источника напряжения, второй элемент смещения, содержащий генератор втекающего тока, отражатель тока и ключ, первый, второй D-триггеры, первый, второй i нвер- тирующие элементы задержки, первый, второй элементы И, элемент ИЛИ, первый, второй, третий, четвертый инверторы, первый, второй КМПД-ключи на транзисторах п- и р-типа, конденсатор, а дифференциальный каскад выполнен на первом и втором транзисторах р-типа, затвор первого транзистора является соответственно неинвертирующим, а затвор второго - инвертирующим входами компаратора, истоки первого и второго транзисторов объединены и подключены к выходу генератора тока дифференциального каскада на третьем транзисторе р-типа, затвор которого соединен с источником управляющего напряжения, сток первого транзистора соединен с

0 входом отражателя тока, выполненного на четвертом и пятом транзисторах n-типа, и с выходами отражателей тока первого и второго элементов смещения, выполненных соответственно на транзисторах п- и р-типа,

5 выход отражателя тока дифференциального каскада соединен со стоком второго транзистора, вход отражателя тока первого элемента смещения соединен с выходом генератора вытекающего тока на транзисто0 ре р-типа, затвор которого подключен к источнику управляющего напряжения, исток выходного транзистора отражателя тока первого элемента смещения подключен к стоку транзистора n-типа ключа, вход отра5 жателя тока второго элемента смещения соединен с выходом генератора втекающего тока на транзисторе n-типа, затвор которого подключен к выходу источника управляющего напряжения, исток выходного транзи0 стора отражателя тока второго элемента смещения подключен к стоку транзистора р-типа ключа, затвор которого соединен с выходом первого инвертора, выход первого элемента И соединен с входом элемента

5 ИЛИ, другой вход которого соединен с выходом второго элемента И, D-входы первого и второго D-триггеров соединены с шиной источника напряжения, а С-входы - с выходом инвертирующего усилителя, прямой вы0 ход первого D-триггера соединен с первым входом первого элемента И, а инверсный выход - с входом первого инвертирующего элемента задержки, выход которого соединен с R-входом первого D-триггера, прямой

5 выход второго D-триггера соединен с первым входом второго элемента И, инверсный выход соединен с входом второго инвертирующего элемента задержки, выход которого соединен с R-входом второго D-триггера,

0 второй вход первого элемента И соединен с выходом третьего инвертора, с входом четвертого инвертора и через конденсатор с общей шиной, выход элемента ИЛИ соединен с входом второго инвертора, с затвором

5 транзистора р-типа первого КМПД-ключа и с затвором транзистора n-типа второго КМПД-ключа, исток транзистора р-типа первого КМПД-ключа соединен со стоком транзистора n-типа и с выходом инвертирующего усилителя, сток транзистоpa p-типа первого КМПД-ключа соединен с истоком транзистора n-типа, с входом третьего инвертора, с истоком и стоком транзисторов р- и n-типа второго КМПД- ключа, сток и исток которых являются выходом компаратора и соединены с выходом четвертого инвертора, с вторым входом второго элемента И, выход второго инвертора соединен с затвором транзистора п-типа первого КМПД-ключа, с затвором транзистора р-типа второго КМПД-ключа, отличающийся тем, что, с целью повышения точности сравнения медленно меняющихся сигналов, в него введены третий, четвертый D-триггеры, третий, четвертый инвертирующие элементы задержки, при этом выходы

первого, второго элементов И соединены соответственно с С-входами третьего, четвертого D-триггеров, D-входы которых соединены с шиной источника напряжения, прямой выход третьего D-триггера соединен с затвором транзистора n-типа ключа первого элемента смещения, а инверсный выход соединен с входом третьего инвертирующего элемента задержки, выход которого соединен с R-входом третьего D-триггера, прямой выход четвертого D-триггера соединен с входом первого инвертора, а инверсный выход соединен с входом четвертого инвертирующего элемента задержки, выход которого соединен с R-входом четвертого D-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Ключевой элемент | 1986 |

|

SU1406768A1 |

| Многоканальный коммутатор | 1985 |

|

SU1246362A1 |

| Усилительное устройство | 1988 |

|

SU1571749A1 |

| D-триггер на КМДП-транзисторах | 1990 |

|

SU1728963A1 |

| Усилительное устройство | 1986 |

|

SU1350821A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Повторитель напряжения на КМДП-транзисторах | 1989 |

|

SU1656671A1 |

| Выходное устройство на МДП-транзисторах | 1988 |

|

SU1598159A1 |

| Многоканальный коммутатор | 1984 |

|

SU1220124A1 |

Изобретение относится к импульсной технике, может быть использовано при построении аналого-цифровых схем на МДП- транзисторах и обеспечивает повышение точности сравнения медленно меняющихся сигналов. Компаратор содержит собствен но компаратор, построенный на трех каскадах: дифференциальном 6, каскаде суммирования и перехода к двухпроводному выходу, выходном каскаде инвертирующего усилителя 13, а также содержит первый элемент 2 смещения с источником вытекающего тока, второй элемент 14 смещения с источником втекающего тока, четыре ждущих мультивибратора, построенных на D-триггерах 18, 19, 32 и 33 и элементах 20. 21, 34 и 35 задержки импульсного сигнала, комбинационную схему формирования сигналов управления схемами смещения на первом, втором элементах И 22 и 23, первом инверторе 25, выходной триггер-защелку, состоящий из КМДП-ключей 29 и 30, инверторов 26, 27 и 28, элемент ИЛИ 24. Сравниваемые сигналы: входной аналоговый и опорный подаются на два входа дифференциального каскада 6 собственно компаратора. В компараторе длительность интервала действия регенеративной обратной связи превышает время перехода входным сигналом, имеющим минимальную скорость изменения напряжения, всей зоны неопределенности, т.е. за счет временной селекции управления генераторами втекающего и вытекающего токов и выдачи информации с выходного триггера-защелки значительно повышается точность сравнения медленно меняющихся сигналов 2 ил.

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-11-07—Публикация

1989-05-22—Подача