(54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент с тремя состояниями | 1982 |

|

SU1051721A1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| Управляемый мажоритарный элемент | 1981 |

|

SU993479A1 |

| Логический элемент "исключающееНЕ-или" HA Мдп ТРАНзиСТОРАХ | 1979 |

|

SU797074A1 |

| @ -Триггер с предпочтительной установкой в @ -состояние | 1982 |

|

SU1075380A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Логический элемент на мдп-транзисторах | 1977 |

|

SU664297A1 |

| Формирователь парафазных импульсов | 1981 |

|

SU984013A1 |

| Логический элемент "исключающее или" на кмдп-транзисторах | 1979 |

|

SU790340A1 |

1

Изобретение относится к обпасти вычислительной техники и эпектроники и может быть использовано в качестве логического элемента универсальных и специализированных электронных цифровых вычислительных устройств.

Известен логический элемент И-НЕ, содержащий три последовательно включенных р -канальных МДП-транзистора, вход нагрузочного транзистора подкточен к шине питания, а выход - к выходной шине, затворы первого и второго.переключательных -транзисторов подключены, соответственно, к первой и второй входным шинам, вход второго переключательного jg транзистора подкшочен к обшей шнне.Дпя реализации функции И необходимо к выходу .элемента подключить дополнитепъный инвертор 1.

Недостатком известного погического элемента является большая потребляемая мощность, так как он выполнен на МДПтранзисторах одного типа.

Известен логический элемент И, содержащий два поспЁДоватепьно вкпюч енных инвертора, каждый на которых выполнен на комплементарной паре МДП-транзисторов, причем вхоД первого инвертора подключен к первой входной шине, исток его р-канального МДП-транаистора-подклю- . чей к шине питания, второй инвертор включен между шиной питания и общей ишной, а его выход подключен к выходной шине, и два МДП-транаистора, один из которых, р -канальный, включен между шиной питания Н выходом первого инвертора, а второй, VI -канальный, включен между ис током h-канального транзистора первого инвертора R обшей шиной, затворы этих обоих транзисторов подключены к второй входной шине 2,

Недостатком известного логического элемента И является избыточное количест20во транзисторов, что приводит к снижению надежности.

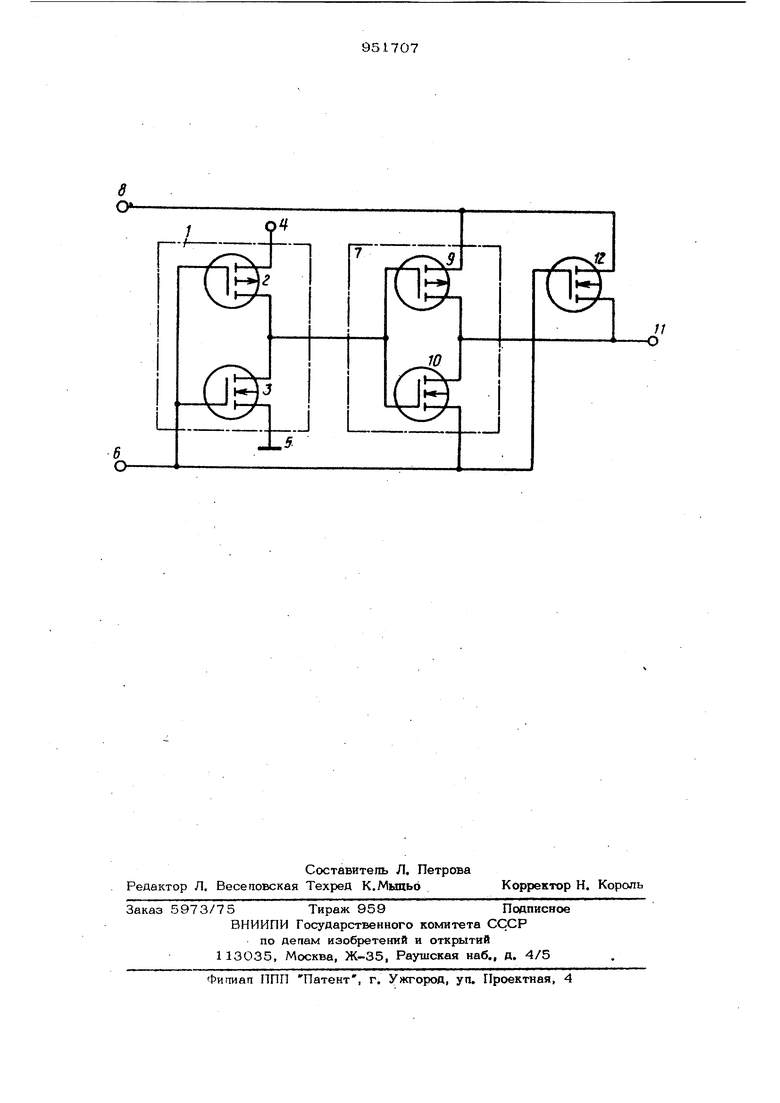

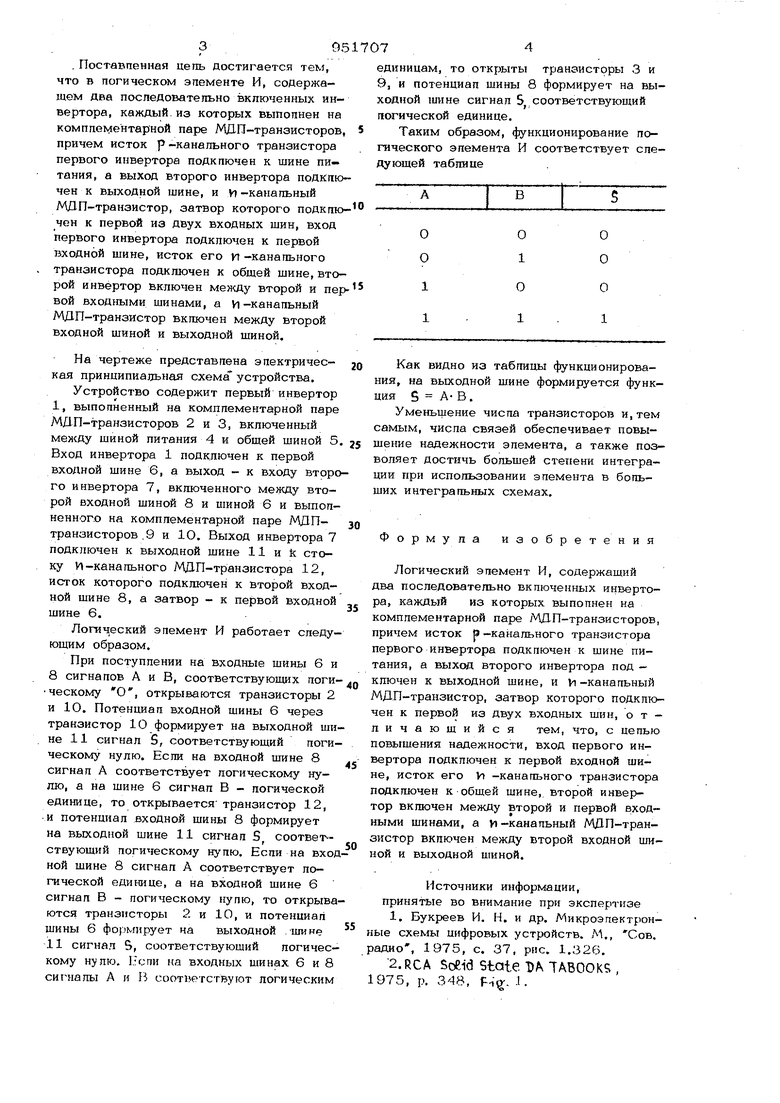

Цепь нзоббетения - повышение надежности. 39517 . Поставленная цепь достигается тем, что в логическом элементе И, содержащем два последовательно включенных инвертора, каждый, из которых выполнен на комплементарной паре МДП-транзисторов, 5 причем исток р-канального транзистора первого инвертора подключен к шине питания, а выход второго инвертора подключен к выходной шине, и и-канальный МДП-транзистор, затвор которого подклю- чен к первой из двух входных шин, вход первого инвертора подключен к первой входной щине, исток его и -канального транзистора подключен к общей шине, второй инвертор включен между второй и пер- вой входными шинами, а и-канальный МДП-транзистор включен между второй входной шиной и выходной щиной. На чертеже представлена электрическая принципиальная схема устройства. Устройство содержит первый инвертор 1, выполненный на комплементарной паре МДП-транзисторов 2 и 3, включенный мемсду шиной питания 4 и обшей шиной 5. Вход инвертора 1 подключен к первой входной шине 6, а выход - к входу второ го инвертора 7, включенного между второй входной шиной 8 и шиной 6 и выполненного на комплементарной паре МДПтранзисторов .9 и 10. Выход инвертора 7 подключен к выходной шине link стоку И-канального МДП-транзистора 12, исток которого подключен к второй входной шине 8, а затвор - к первой входной шине 6. Логический элемент И работает следующим образом. При поступлении на входные шины 6 и 8 сигналов А и В, соответствующих логическому О, открываются транзисторы 2 и 10. Потенциал входной шины 6 через транзистор 10 формирует на выходной шине 11 сигнал S, соответствующий логическому нулю. Если на входной шине 8 сигнал А соответствует логическому нулю, а на шине 6 сигнал В - логической единице, то открывается транзистор 12, и потенциал входной шины 8 формирует на выходной шине 11 сигнал S соответствующий логическому нулю. Если на вход ной шине 8 сигнал А соответствует логической единице, а на входной шине 6 сигнал В - логическому нулю, то открыва ются транзисторы 2 и 10, и потенциал шины 6 формирует на выходной . чип не 11 сигнал 5), соответствующий логическому нулю. 1:спи на входных шинах 6 и 8 сигналы А и Г соответствугот логическим 74 единицам, то открыты транзисторы 3 и 9, и потенциал шины 8 формирует на выходной шине сигнал S соответствующий логической единице. Таким образом, функционирование погического элемента И соответствует следующей табгшце Как видно из таблицы функционирования, на выходной шине формируется функция S А- В. Уменьшение числа транзисторов и, тем самым, числа связей обеспечивает повышение надежности элемента, а также позволяет достичь большей степени интеграции при использовании элемента в больших интегральных схемах. Формула изобретения Логический элемент И, содержащий два последовательно включенных инвертора, каждый из которых выполнен на комплементарной паре МДП-транзисторов, причем исток р -канального транзистора первого инвертора подключен к шине питания, а выход второго инвертора под - ключен к выходной шине, и Vi -канальный МДП-транзистор, затвор которого подключен к первой из двух входных шин, отличающийся тем, что, с цепью повышения надежности, вход первого инвертора подключен к первой входной шине, исток его Vi -канального транзистора подключен к общей шине, второй инвертор вкточен между второй и первой входными шинами, а и -канальный МДП-транзистор включен между второй входной шиной и выходной шиной. Источники информации, принятые во Внимание при экспертизе 1. Букрюев И. 14. и др. Микроэлектрюнные схемы цифровых устройств. М., Сов. радио , 1975, с. 37, рнс. 1.326. 2.RCA Scjeid State DA TABOOKS , 1975, p. 348, F.-,-. :l.

Авторы

Даты

1982-08-15—Публикация

1981-01-29—Подача