28

ел

со со со со

Ј

Изобретение относится к вычисли- . тельной технике и может быть исполь- зовано в интегральных микросхемах в качестве выходного буферного элемента с тремя состояниями при работе на общую шину.

Целью изобретения является повышение надежности работы.

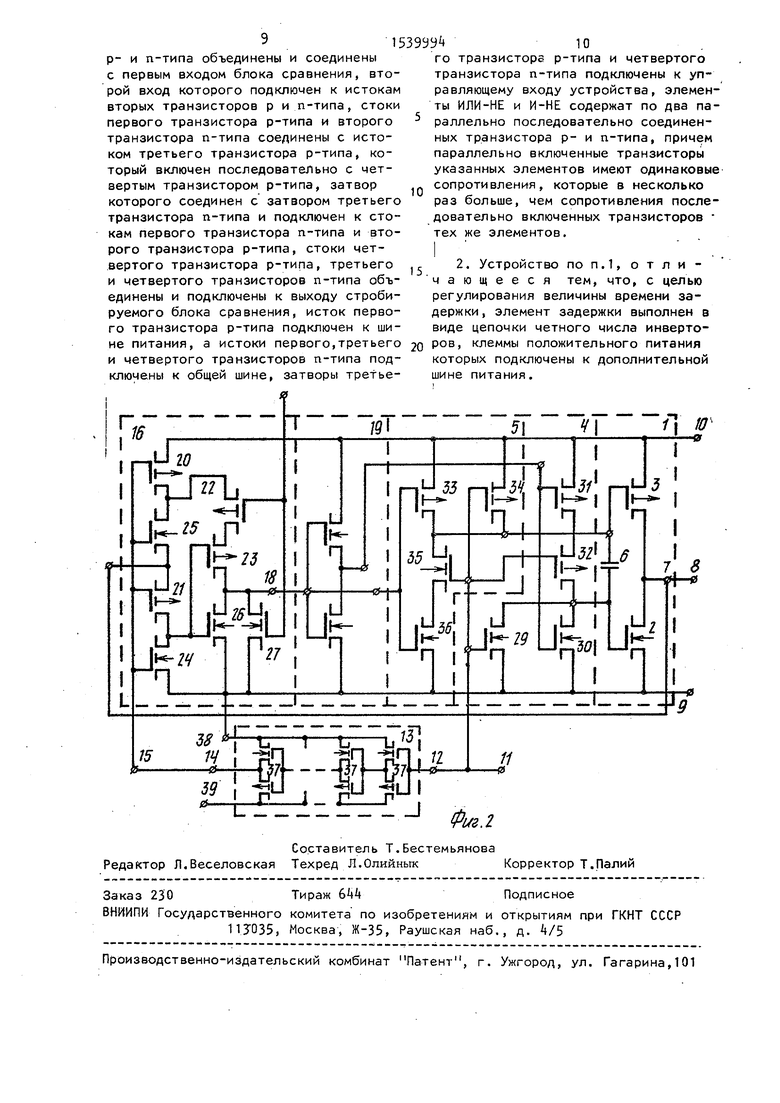

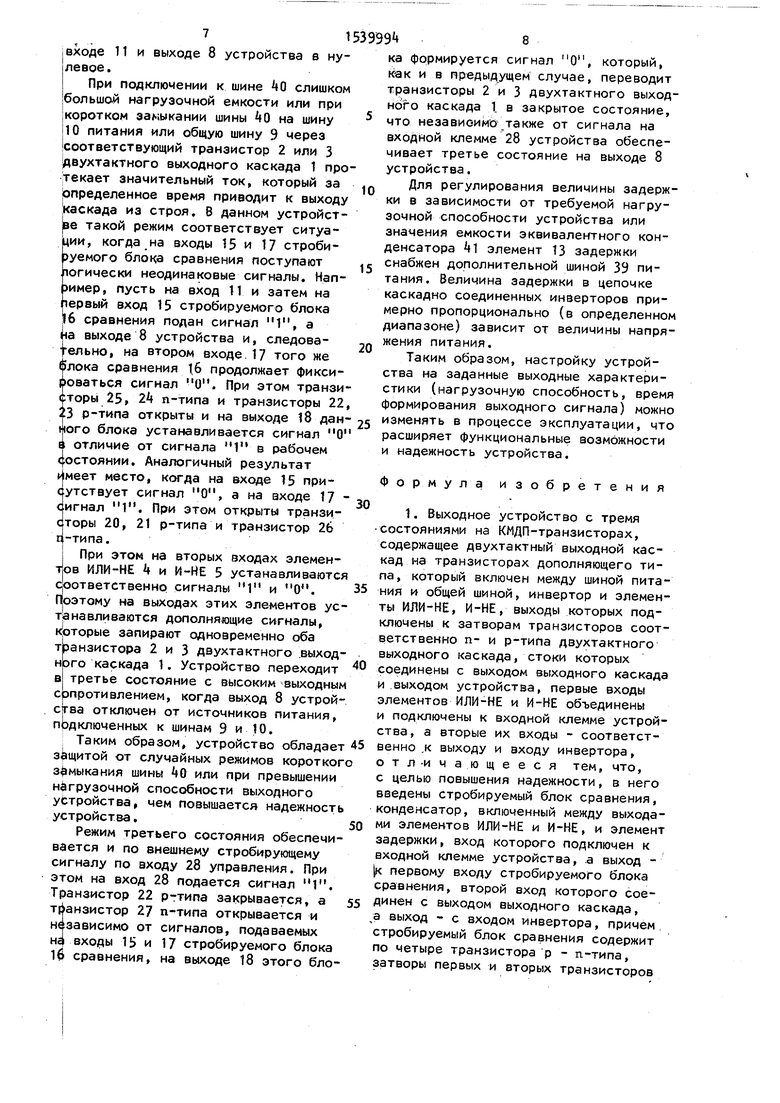

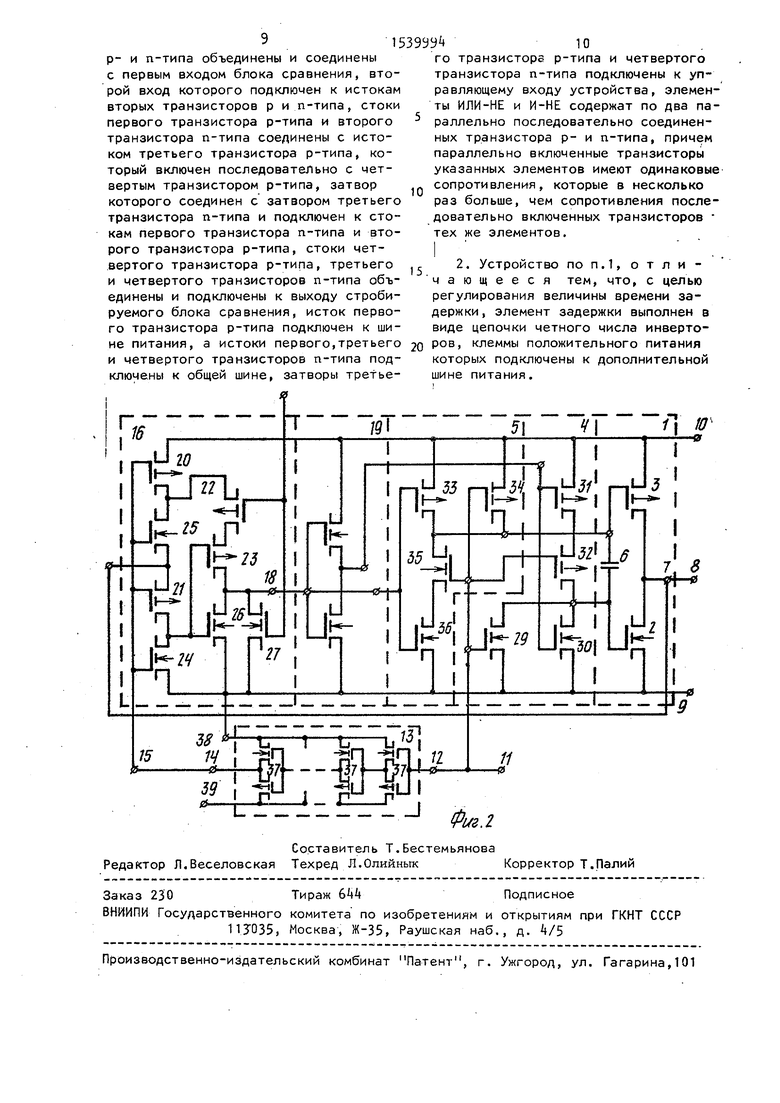

На фиг.1 приведена функциональная схема устройства; на фиг.2 - принципиальная схема выходного устройства с тремя состояниями на КМДП-транзисторах.

Устройство содержит двухтактный выходной каскад 1 на транзисторах 2 и 3 дополняющего типа, затворы которы подключены к выходам соответственно элементов ИЛИ-НЕ k и И-НЕ 5, между которыми также включен конденсатор 6. Стоки транзисторов 2 и 3 двухтактного выходного каскада 1 объединены и подключены к выходу 7 указанного каскада который в свою очередь соединен с выходом 8 устройства. Истоки транзисторов 2 и 3 того же каскада подключены соответственно к общей шине 9 и шине 10 питания. Вход И устройства соединен с первыми входами элементов ИЛИ-НЕ k и И- НЕ 5 и с входом 12 элемента 13 задерж ки 13, выход И которого подключен к первому входу 15 стробируемого блока 16 сравнения, второй вход 17 которого соединен с выходом 7 двухтактного выходного каскада 1. Выход 18 стробиру- емого блока 16 сравнения подключен непосредственно к второму входу элемента И-НЕ 5 и через инвертор 19 - к второму входу элемента ИЛИ-НЕ k.

Стробируемый блок 16 сравнения содержит четыре транзистора 20-23 р-ти- па и четыре транзистора 24-27 п-типа. Затворы первых 20 и 2k и вторых 21 и 25 транзисторов объединены и соединены с первым входом 15 данного блока. Истоки вторых транзисторов 21 и 25 соединены с вторым входом 17 того же блока 16. Стоки первого транзистора 20 р-типа и второго транзистора 25 n-типа соединены с истоком третьего транзистора 22 р-типа, который включе последовательно с четвертым транзистором 23 р-типа, затвор котого соедине с затвором третьего транзистора 26

n-типа, а также со стоками первого транзистора 24 n-типа и второго транзистора 21 р-типа.

Стоки четвертого транзистора 23 рттипа, третьего 26 и четвертого 27

5

0

5

0 35

транзисторов n-типа объединены и подключены к выходу 18 стробируемого блока 16 сравнения.

Исток первого транзистора 20 р-типа подключен к шине питания 10, а истоки первого 2k, третьего 26 и четвертого 27 транзисторов n-типа соединены с общей шиной 9. Затворы третьего транзистора 22 р-типа и четвертого транзистора 27 n-типа подключены к управляющему входу 28 устройства.

Элемент ИЛИ-НЕ 4 содержит два параллельно включенных транзистора 29 и 30 n-типа и два последовательно включенных 31 и 32 транзистора р-типа. Элемент И-НЕ 5 содержит два параллельно включенных транзистора 33 и 34 р-типа и два последовательно включенных транзистора 35 и 36 n-типа. В каждом из элементов 4 и 5 указанные пары транзисторов соединены последовательно и включены между шиной 10 питания и общей шиной 9.

Параллельно включенные транзисторы в обоих элементах 4 и 5 имеют одинаковое сопротивление, которое в несколько раз превышает сопротивление последовательно включенных транзисторов другого типа, которые также между собой равны.

Элемент 13 задержки выполнен на комплементарных инверторах 37, которые соединены последовательно с входа на выход. Причем первая клемма 38 пита ния инверторов 37 подключена к нулевой шине 9, а дополнительная клемма 39 питания может быть соединена с дополнительной шиной питания. Число инверторов 37 в элементе задержки 13- четное.

Выходная клемма 8 устройства подключается к шине 40, к которой могут быть подключены через ключи или другие устройства ввода-вывода различные приемники и передатчики информации. Шина 40 представляет собой емкостную нагрузку в виде эквивалентного конденсатора 41.

Конденсатор 6 выполнен в виде бут- стрепной МДП-структуры, одна из его 50 обкладок соединена с выходом элемента ИЛИ-НЕ 4, а другая изолированная обкладка соединена с выходом элемента И-НЕ 5.

Устройство работает следующим образом.

В рабочем состоянии устройства на управляющий вход 28 устройства подается сигнал О. При этом четвертый транзистор 27 n-типа закрыт, а третий

40

45

55

транзистор 22 р-типа открыт. Таким образом, в этом состоянии управляющий сигнал не влияет на сигнал, вырабатываемый стробируемым блоком 16 сравнения .

Предположим, что на входной клемме 11 также присутствует сигнал. Тогда на выходе элемента И-НЕ 5 будет сигнал 1, и транзистор 3 р-типа двухтактного выходного каскада 1 будет закрыт. Поэтому на выходной клемме 8 устройства при этом не может сформироваться единичный сигнал, а может установиться только сигнал О. Этому способствует также и конденсатор 6, благодаря которому часть напряжения питания с выхода элемента И-НЕ 5 передается на затвор транзистора 2 п- типа. Поэтому на обоих входах 15 и 17 стробируемого блока 16 сравнения в этом состоянии присутствуют сигналы О. При этом транзисторы 20, 21 и 23 р-типа открыты, a 2k t 25 и 26 п-типа закрыты. На выходе 18 стробируемого блока 16 сравнения формируется сигнал 1, который не изменяет состояния логического элемента И-НЕ 5 и благодаря инвертору 19 устанавливает на выходе элемента ИЛИ-НЕ k сигнал 1м, который подтверждает открытое состояние транзистора 2 n-типа двухтактного выходного каскада 1 и нулевой сигнал на выходе 8 устройства.

При переходе с нулевого состояния в единичное на входе 11 устройства прежде всего открывается транзистор 29 n-типа и на выходе элемента ИЛИ-НЕ k быстро формируется сигнал О.Транзистор 2 n-типа двухтактного выходного каскада 1 при этом быстро закрывается, тем самым предотвращая протекание сквозного тока в этом каскаде при отпирании транзистора 3 р-типа. Также под действием входного сигнала закрывается транзистор 3 р-типа и открывается транзистор 35 n-типа элемента И-НЕ 5.

8 результате за счет цепочки открытых транзисторов 35 и 36 n-типа на затворе транзистора 3 р-типа двухтактного выходного каскада 1 начинает формироваться с определенной постоянной времени сигнал О.Соответственно, через открывающийся транзистор 3 эквивалентный конденсатор 41 начинает заряжаться от шины 10 питания, и на выходе 8 устройства формируется сигнал Г1.

0

5

0

На первом этапе переключения благодаря наличию элемента 13 задержки сигналы на входах 15 и 17 стробируемого блока 16 сравнения не успевают измениться, что обеспечивает начало срабатывания логических элементов И-НЕ 5 и ИЛИ-НЕ k. Величина задержки элемента 13 задержки выбирается примерно равной времени формирования сигнала на выходе 8 устройства на заданном уровне напряжения, например на уровне порогового напряжения транзисторов. В дальнейшем сигналы на входах 15 и 17 стробируемого блока сравнения изменяются синфазно, что гарантирует завершение процесса переключения.

При наличии единичных сигналов на этих входах состояние стробируемого блока 16 сравнения не изменяется. При ,этом открыты транзисторы 2 и 25 п- типа и транзисторы 22 и 23 р-типа. Таким образом, стробируемый блок 16 сравнения реализует функцию равнозначности, когда на выходе 18 формируется сигнал 1 при одинаковых входных сигналах на входах 15 и 17 и при отсутствии сигнала на управляющем входе 28.

Благодаря тому, что сопротивление параллельно включенных транзисторов , 2у, 30 и 33, 3 значительно меньше, чем сопротивление последовательно

включенных транзисторов 31 32 и 35 36, процессы переключения транзисторов 3 и 2 двухтактного выходного каскада происходят последовательно, что гарантирует отсутствие сквозных токов

при переключении. При этом конденсатор 6 способствует также более полно- ,му запиранию соответствующего транзи- стора 2 или 3, поскольку через него передается запирающий один из этих

транзисторов перепад напряжения с выхода логического элемента 4 или 5, где процесс переключения идет также синфазно, но медленнее. Таким образом, несмотря на возможные искажения

уровней логических сигналов на выходах логических элементов ИЛИ-НЕ Ц и И-НЕ 5 по сравнению с напряжениями на шине 10 питания и общей шине 9 гарантируется полное закрытие непроводящего транзистора 2 или 3 двухтактного выходного каскада 1.

Аналогично происходит переключение устройства из единичного состояния на

11 и выходе 8 устройства в ну- ка формируется сигнал О

входе левое.

При подключении к шине 0 слишком большой нагрузочной емкости или при коротком замыкании шины 40 на шину ilO питания или общую шину 9 через соответствующий транзистор 2 или 3 двухтактного выходного каскада 1 протекает значительный ток, который за определенное время приводит к выходу каскада из строя. 8 данном устройст- е такой режим соответствует ситуации, когда на входы 15 и 17 строби- уемого блока сравнения поступают югически неодинаковые сигналы. Нап- имер, пусть на вход 11 и затем на тервый вход 15 стробируемого блока 6 сравнения подан сигнал 1, а на выходе 8 устройства и, следова- ельно, на втором входе 17 того же лока сравнения 6 продолжает фикси- оваться сигнал 0й. При этом транзи- торы 25, 24 n-типа и транзисторы 22,

10

15

20

23 р-типа открыты и на выходе 18 дан- 25 изменять в процессе эксплуатации, что

который,

как и в предыдущем случае, переводит транзисторы 2 и 3 двухтактного выходного каскада 1. в закрытое состояние, что независимо также от сигнала на входной клемме 28 устройства обеспечивает третье состояние на выходе 8 устройства.

Для регулирования величины задержки в зависимости от требуемой нагрузочной способности устройства или значения емкости эквивалентного конденсатора 41 элемент 13 задержки снабжен дополнительной шиной 39 питания. Величина задержки в цепочке каскадно соединенных инверторов примерно пропорционально (в определенном диапазоне) зависит от величины напряжения питания.

Таким образом, настройку устройства на заданные выходные характеристики (нагрузочную способность, время формирования выходного сигнала) можно

його блока устанавливается сигнал О1 Е; отличие от сигнала 1 в рабочем состоянии. Аналогичный результат место, когда на входе 15 присутствует сигнал О, а на входе 17 - сигнал 1. При этом открыты транзисторы 20, 21 р-типа и транзистор 26 п-типа.

При этом на вторых входах элемен- в ИЛИ-НЕ 4 и И-НЕ 5 устанавливаются Соответственно сигналы 1 и О. Поэтому на выходах этих элементов устанавливаются дополняющие сигналы, которые запирают одновременно оба транзистора 2 и 3 двухтактного выходного каскада 1. Устройство переходит в третье состояние с высоким выходным сопротивлением, когда выход 8 устройства отключен от источников питания, подключенных к шинам 9 и 10.

30

i

35

40

расширяет функциональные возможности и надежность устройства.

Формула изобретения

1. Выходное устройство с тремя состояниями на КМДП-транзисторах, содержащее двухтактный выходной каскад на транзисторах дополняющего типа, который включен между шиной питания и общей шиной, инвертор и элементы ИЛИ-НЕ, И-НЕ, выходы которых подключены к затворам транзисторов соответственно п- и р-типа двухтактного выходного каскада, стоки которых соединены с выходом выходного каскада и выходом устройства, первые входы элементов ИЛИ-НЕ и И-НЕ объединены и подключены к входной клемме устройства, а вторые их входы - соответстТаким образом, устройство обладает 45 венно ,к выходу и входу инвертора,

защитой от случайных режимов короткого замыкания шины 40 или при превышении нагрузочной способности выходного устройства, чем повышается надежность устройства.50

Режим третьего состояния обеспечивается и по внешнему стробирующему сигналу по входу 28 управления. При этом на вход 28 подается сигнал 1. Транзистор 22 р-типа закрывается, а 55 транзистор 27 n-типа открывается и независимо от сигналов, подаваемых н4 входы 15 и 17 стробируемого блока 16 сравнения, на выходе 18 этого блоотл-и чающееся тем, что, с целью повышения надежности, в него введены стробируемый блок сравнения, конденсатор, включенный между выходами элементов ИЛИ-НЕ и И-НЕ, и элемент задержки, вход которого подключен к входной клемме устройства, а выход - |к первому входу стробируемого блока сравнения, второй вход которого соединен с выходом выходного каскада, а выход - с входом инвертора, причем стробируемый блок сравнения содержит по четыре транзистора р - п.-типа, затворы первых и вторых транзисторов

ка формируется сигнал О

0

который,

как и в предыдущем случае, переводит транзисторы 2 и 3 двухтактного выходного каскада 1. в закрытое состояние, что независимо также от сигнала на входной клемме 28 устройства обеспечивает третье состояние на выходе 8 устройства.

Для регулирования величины задержки в зависимости от требуемой нагрузочной способности устройства или значения емкости эквивалентного конденсатора 41 элемент 13 задержки снабжен дополнительной шиной 39 питания. Величина задержки в цепочке каскадно соединенных инверторов примерно пропорционально (в определенном диапазоне) зависит от величины напряжения питания.

Таким образом, настройку устройства на заданные выходные характеристики (нагрузочную способность, время формирования выходного сигнала) можно

изменять в процессе эксплуатации, что

расширяет функциональные возможности и надежность устройства.

Формула изобретения

1. Выходное устройство с тремя состояниями на КМДП-транзисторах, содержащее двухтактный выходной каскад на транзисторах дополняющего типа, который включен между шиной питания и общей шиной, инвертор и элементы ИЛИ-НЕ, И-НЕ, выходы которых подключены к затворам транзисторов соответственно п- и р-типа двухтактного выходного каскада, стоки которых соединены с выходом выходного каскада и выходом устройства, первые входы элементов ИЛИ-НЕ и И-НЕ объединены и подключены к входной клемме устройства, а вторые их входы - соответстотл-и чающееся тем, что, с целью повышения надежности, в него введены стробируемый блок сравнения, конденсатор, включенный между выходами элементов ИЛИ-НЕ и И-НЕ, и элемент задержки, вход которого подключен к входной клемме устройства, а выход - |к первому входу стробируемого блока сравнения, второй вход которого соединен с выходом выходного каскада, а выход - с входом инвертора, причем стробируемый блок сравнения содержит по четыре транзистора р - п.-типа, затворы первых и вторых транзисторов

р- и n-типа объединены и соединены с первым входом блока сравнения, второй вход которого подключен к истокам вторых транзисторов р и n-типа, стоки первого транзистора р-типа и второго транзистора n-типа соединены с истоком третьего транзистора р-типа, который включен последовательно с четвертым транзистором р-типа, затвор которого соединен с затвором третьего транзистора n-типа и подключен к стокам первого транзистора n-типа и второго транзистора р-типа, стоки четвертого транзистора р-типа, третьего и четвертого транзисторов n-типа объединены и подключены к выходу строби- руемого блока сравнения, исток первого транзистора р-типа подключен к ши399У1 10

го транзистора р-типа и четвертого транзистора n-типа подключены к управляющему входу устройства, элементы ИЛИ-НЕ и И-НЕ содержат по два параллельно последовательно соединенных транзистора р- и n-типа, причем параллельно включенные транзисторы указанных элементов имеют одинаковые сопротивления, которые в несколько раз больше, чем сопротивления последовательно включенных транзисторов тех же элементов.

10

2. Устройство по п.1, о т л и - чающееся тем, что, с целью регулирования величины времени задержки , элемент задержки выполнен в виде цепочки четного числа инверто

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1980 |

|

SU919062A1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| Формирователь импульсов на МДП-транзисторах | 1988 |

|

SU1539995A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| Элемент с тремя состояниями | 1981 |

|

SU1003349A1 |

| УСТРОЙСТВО СРАВНЕНИЯ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2236696C1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| Усилитель | 1991 |

|

SU1818678A1 |

| Компаратор | 1989 |

|

SU1690184A1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

Изобретение относится к вычислительной технике и может быть использовано в интегральных микросхемах в качестве выходного буферного элемента с тремя состояниями при работе на "оющую" шину. Целью изобретения является повышение надежности работы, за счет снижения токопотребления в выходном каскаде как в процессе переключения, так и при работе на шину с большой емкостной нагрузкой. Устройство содержит выходной каскад 1, элементы ИЛИ-НЕ 4, И-НЕ 5, инвертор 19, входную шину 11, шину питания 10, общую шину 9. Для достижения поставленной цели в устройство введены стробируемый блок сравнения 16, элемент задержки 13, конденсатор 41 и новые функциональные связи. 1 з.п. ф-лы, 2 ил.

не питания, а истоки первого,третьего эд Р°в клеммы положительного питания и четвертого транзисторов n-типа под- которых подключены к дополнительной ключены к общей шине, затворы третье- шине питания.

J

i

Составитель Т.Бестемьянова

Редактор Л.Веселовская Техред Л.Олийнык

Заказ 230Тираж 6kkПодписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 11J035, Москва, Ж-35, Раушская наб,, д. 4/5

Корректор Т.Палий

| Магистральный формирователь импульсов | 1986 |

|

SU1385277A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Формирователь выходных сигналов для запоминающего устройства на кмдп-транзисторах | 1978 |

|

SU767835A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-01-30—Публикация

1988-06-20—Подача