113

Изобретение относится к автоматике и вычислительной технике и может быть использовано в преобразователях перемещения в код.

Целью изобретения является повышение точности преобразователя путем исключения формирователей опорного напряжения.

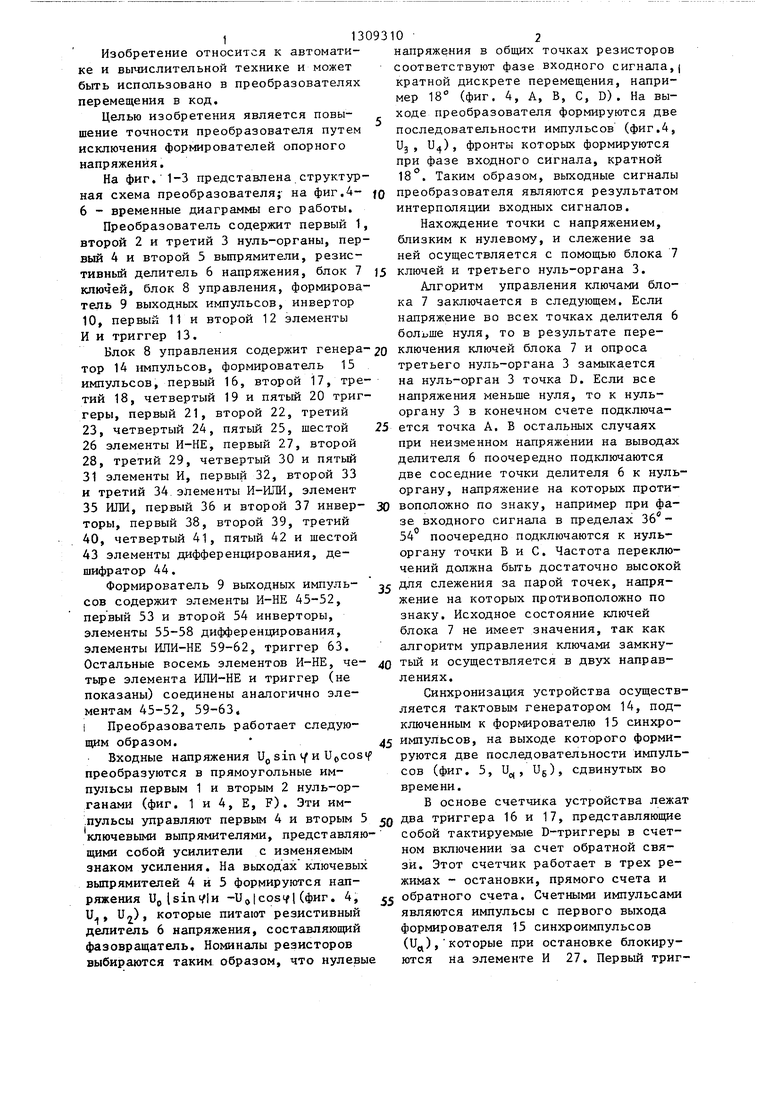

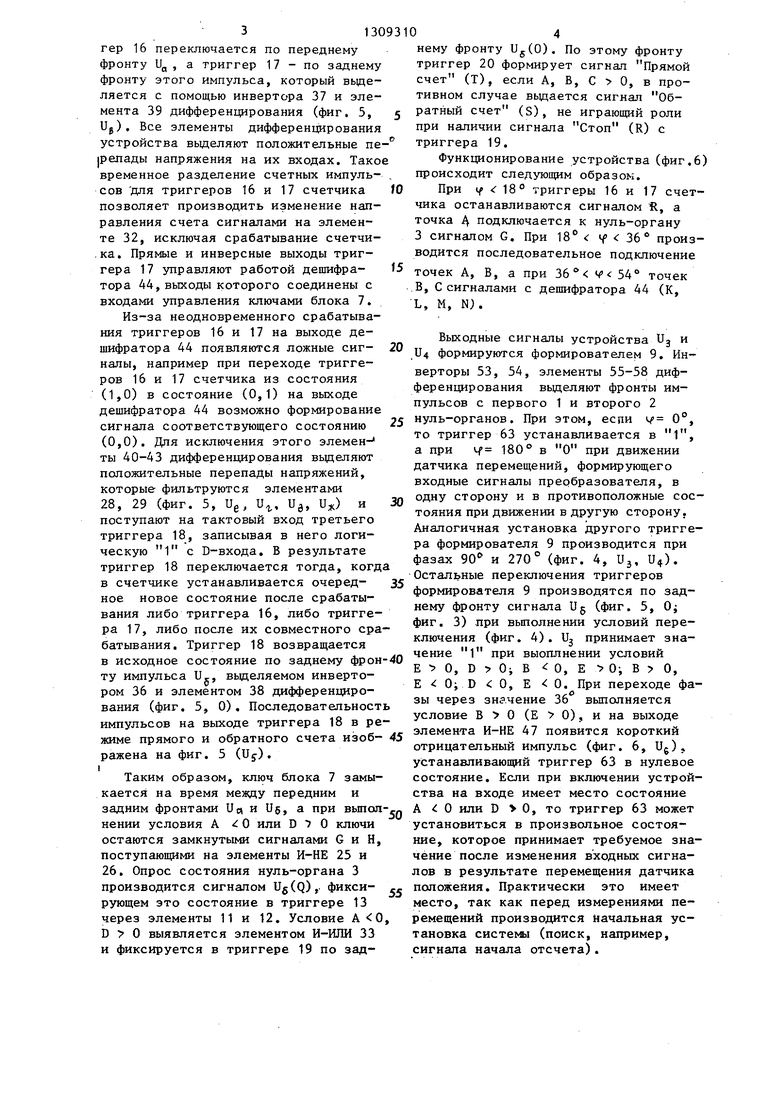

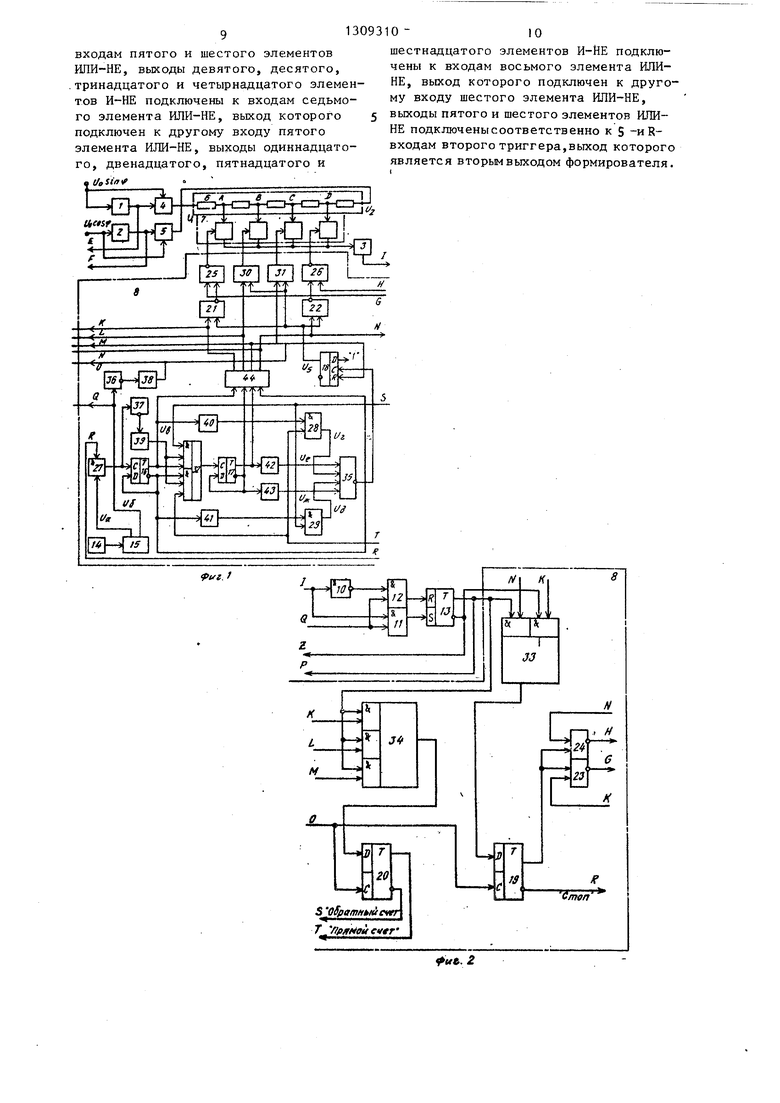

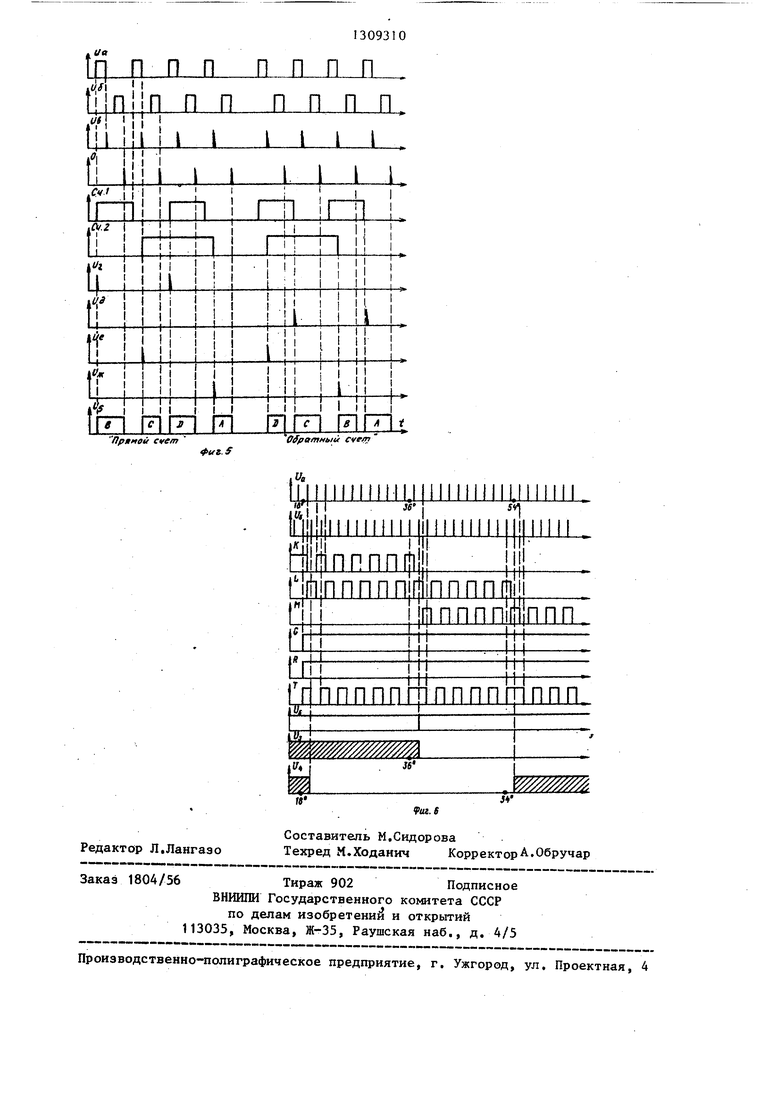

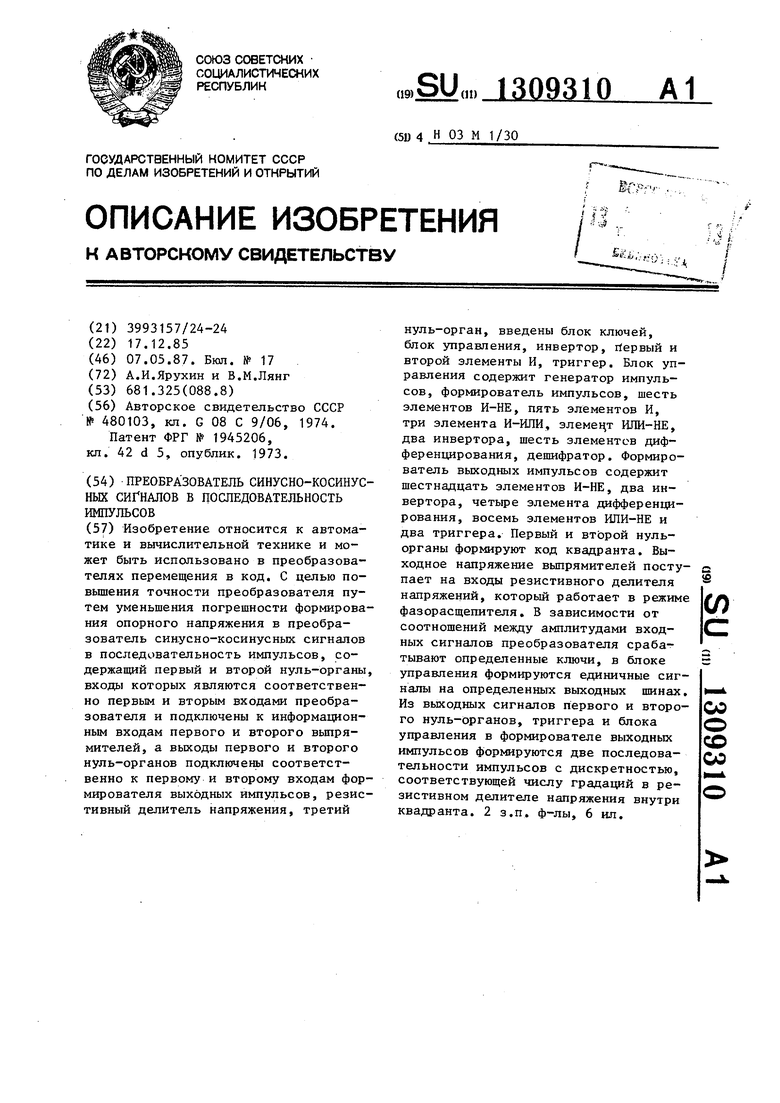

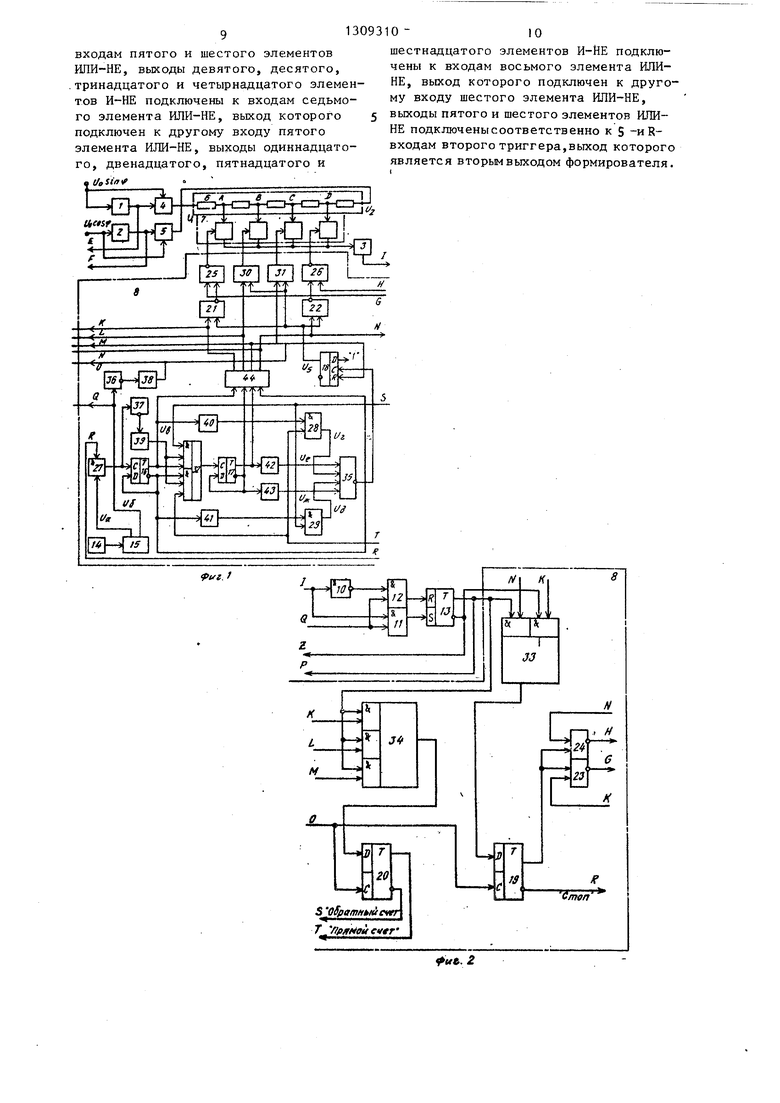

На фиг. 1-3 представлена структурная схема преобразователя; на фиг.А- 6 - временные диаграммы его работы.

Преобразователь содержит первый 1, второй 2 и третий 3 нуль-органы, первый 4 и второй 5 выпрямители, резис- тивный делитель 6 напряжения, блок 7 кпючей, блок 8 управления, формирователь 9 выходных импульсов, инвертор 10, первый 11 и второй 12 элементы И и триггер 13.

Блок 8 управления содержит генератор 14 импульсов, формирователь 15 импульсов, первый 16, второй 17, третий 18, четвертый 19 и пятый 20 триггеры, первый 21, второй 22, третий 23, четвертый 24, пятый 25, шестой 26 элементы И-НЕ, первый 27, второй 28, третий 29, четвертый 30 и пятый 31 элементы И, первый 32, второй 33 и третий 34 элементы И-ИЛИ, элемент 35 ИЛИ, первый 36 и второй 37 инвер- торы, первый 38, второй 39, третий 40, четвертый 41, пятый 42 и шестой 43 элементы дифференцирования, дешифратор 44.

Формирователь 9 выходных импуль- сов содержит элементы И-НЕ 45-52, первый 53 и второй 54 инверторы, элементы 55-58 дифференцирования, элементы ИЛИ-НЕ 59-62, триггер 63. Остальные восемь элементов И-НЕ, че- тыре элемента ШШ-НЕ и триггер (не показаны) соединены аналогично элементам 45-52, 59-63, I Преобразователь работает следующим образом.

Входные напряжения U sin t/и U cosif преобразуются в прямоугольные импульсы первым 1 и вторым 2 нуль-органами (фиг. 1 и 4, Е, F). Эти им- .пульсы управляют первым 4 и вторым 5 ключевыми выпрямителями, представляющими собой усилители с изменяемым знаком усиления. На выходах ключевых выпрямителей 4 и 5 формируются напряжения Uplsint/ H -и о COS 1/1 (фиг. 4, и., U;j), которые питают резистивный делитель 6 напряжения, составляющий фазовращатель. Номиналы резисторов выбираются таким образом, что нулевые

102

напряжения в общих точках резисторов соответствуют фазе входного сигнала, кратной дискрете перемещения, например 18° (фиг. 4, А, В, С, D). На выходе преобразователя формируются две последовательности импульсов (фиг.4, УЗ , , фронты которых формируются при фазе входного сигнала, кратной 18 . Таким образом, выходные сигналы преобразователя являются результатом интерполяции входных сигналов.

Нахождение точки с напряжением, близким к нулевому, и слежение за ней осуществляется с помощью блока 7 ключей и третьего нуль-органа 3.

Алгоритм управления ключами блока 7 заключается в следующем. Если напряжение во всех точках делителя 6 больше нуля, то в результате переключения ключей блока 7 и опроса третьего нуль-органа 3 замыкается на нуль-орган 3 точка D. Если все напряжения меньше нуля, то к нуль- органу 3 в конечном счете подключается точка А. В остальных случаях при неизменном напряжении на выводах делителя 6 поочередно подключаются две соседние точки делителя 6 к нуль органу, напряжение на которых противоположно по знаку, например при фазе входного сигнала в пределах /о

5ч поочередно подключаются к нуль- органу точки В и С. Частота переключений должна быть достаточно высокой для слежения за парой точек, напряжение на которых противоположно по знаку. Исходное состояние ключей блока 7 не имеет значения, так как алгоритм управления ключами занкну- тьш и осуществляется в двух направлениях.

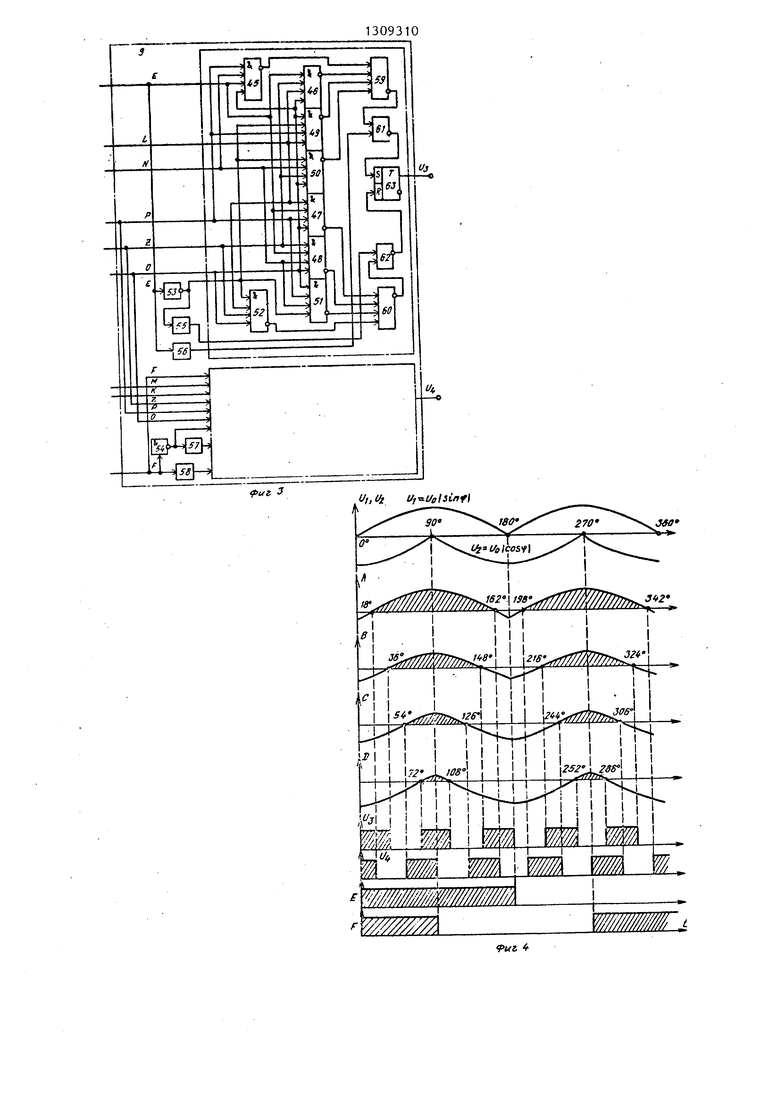

Синхронизация устройства осуществляется тактовым генератором 14, подключенным к формирователю 15 синхроимпульсов, на выходе которого формируются две последовательности импульсов (фиг. 5, Uj , Ug), сдвинутых во времени.

В основе счетчика устройства лежа два триггера 16 и 17, представляющие собой тактируемые D-триггеры в счетном включении за счет обратной связи. Этот счетчик работает в трех режимах - остановки, прямого счета и обратного счета. Счетными импульсами являются импульсы с первого выхода формирователя 15 синхроимпульсов (Ид), которые при остановке блокируются на элементе И 27. Первый тригrep 16 переключается по переднему фронту Ug, а триггер 17 - по заднему фронту этого импульса, который вьще- ляется с помощью инвертора 37 и элемента 39 дифференцирования (фиг. 5, Ug), Все элементы дифференцирования устройства вьщеляют положительные пе |релады напряжения на их входах. Тако временное разделение счетных импуль- сов для триггеров 16 и 17 счетчика позволяет производить изменение направления счета сигналами на элементе 32, исключая срабатывание счетчи- .ка. Прямые и инверсные выходы триггера 17 управляют работой дешифра- тора 44, выходы которого соединены с входами управления ключами блока 7.

Из-за неодновременного срабатывания триггеров 16 и 17 на выходе дешифратора 44 появляются ложные сиг- налы, например при переходе триггеров 16 и 17 счетчика из состояния (1,0) в состояние (0,1) на выходе дешифратора 44 возможно формирование сигнала соответствующего состоянию (0,0). Дпя исключения этого элемен- ты 40-43 дифференцирования вьщеляют положительные перепады напряжений, которые фильтруются элементами 28, 29 (фиг. 5, Ug, и, Ug, ) и поступают на тактовый вход третьего триггера 18, записывая в него логическую 1 с D-входа, В результате триггер 18 переключается тогда, когд в счетчике устанавливается очеред- ное новое состояние после срабатывания либо триггера 16, либо триггера 17, либо после их совместного срабатывания. Триггер 18 возвращается в исходное состояние по заднему фрон ту импульса и, вьщеляемом инвертором 36 и элементом 38 дифференцирования (фиг. 5, 0). Последовательност импульсов на выходе триггера 18 в режиме прямого и обратного счета изоб- ражена на фиг. 5 (Uy).

Таким образом, ключ блока 7 замыкается на время между передним и задним фронтами Ua и Us, а при вьшол нении условия А 0 или D 7 О ключи остаются замкнутыми сигналами G и Н, поступающими на элементы И-НЕ 25 и 26. Опрос состояния нуль-органа 3 производится сигналом Ug(Q), фикси- рующем это состояние в триггере 13 через элементы 11 и 12. Условие D О выявляется элементом И-ИЛИ 33 и фиксируется в триггере 19 по заднему фронту Vg(0), По этому фронту триггер 20 формирует сигнал Прямой счет (Т), если А, В, С О, в противном случае вьздается сигнал Обратный счет (S), не играющий роли при наличии сигнала Стоп (R) с триггера 19.

Функционирование устройства (фиг.6 происходит следующим образом.

При if -( 8° триггеры 16 и 17 счетчика останавливаются сигналом R, а точка Д подключается к нуль-органу 3 сигналом G. При 18 if 36 производится последовательное подключение

точек А, В, а при З6 54° точек .В, С сигналами с дешифратора 44 (К, L, М, N).

Выходные сигналы устройства Uj и ,U4 формируются формирователем 9. Инверторы 53, 54, элементы 55-58 дифференцирования вьщеляют фронты импульсов с первого 1 и второго 2 нуль-органов. При этом, еспи w 0°, то триггер 63 устанавливается в 1, а при 4 180° в О при движении датчика перемещений, формирующего входные сигналы преобразователя, в одну сторону и в противоположные состояния при движении в другую сторону. Аналогичная установка другого триггера формирователя 9 производится при фазах 90 и 270° (фиг. 4, Uj, U). Остальные переключения триггеров формирователя 9 производятся по заднему фронту сигнала Ug (фиг, 5, 0; фиг. 3) при выполнении условий переключения (фиг. 4). Uj принимает значение 1 при выоплнении условий Е О, D Oj В - О, Е 0; В О, Е 0; D О, Е 0. При переходе фазы через значение 36 выполняется услови-е В О (Е 0), и на выходе элемента И-НЕ 47 появится короткий отрицательный импульс (фиг. 6, Ug), устанавливающий триггер 63 в нулевое состояние. Если при включении устройства на входе имеет место состояние А О или D О, то триггер 63 может установиться в произвольное состояние, которое принимает требуемое значение после изменения входных сигналов в результате перемещения датчика положения. Практически это имеет место, так как перед измерениями перемещений производится Начальная установка системл (поиск, например, сигнала начала отсчета).

513

Формула изобретения

1.Преобразователь синусно-коси- нусных сигналов в последовательность импульсов, содержащий первый и второ нуль-органы, входы которых являются соответственно первым и вторым входами преобразователя и подютючены к информационным входам соответственно первого и второго вьшрямителей, а вы ходы первого и второго нуль-органов подключены соответственно k первому

и второму входам формирователя выходных импульсов, резистивный делитель напряжения, третий нуль-орган, отличающийся тем, что, с целью повышения точности преобразователя, в него введены блок ключей блок управления, инвертор, первый и второй элементы И, триггер, выходы первого и второго нуль-органов подключены к управляющим входам первого и второго выпрямителей соответственно, выходы которых подключены к входам резистивного делителя напряжения выходы резистивного делителя напряжения подключены к соответствующим входам блока ключей, выходы блока ключей соединены между собой и подключены к входу третьего нуль-органа выход которого подключен к одному входу первого элемента И и через инвертор - к одному входу второго элемента И, выходы первого и второго элементов И подключены соответствен- но к S- и R-входам триггера, выходы триггера подключены соответственно к третьему и четвертому входам формирователя выходных импульсов и к первому и второму входам блока уп- равления, группа выходов которого подключена к управляющим входам ключей, первый выход блока управления подключен к другим входам первого и второго элементов И, А второй, тре- тий, четвертый, пятый и шестой выходы блока управления подключены соответственно к пятому, шестому, седьмому, восьмому и девятому входам формирователя выходных импульсов.

2,Преобразователь по п. 1, отличающийся тем, что блок управления содержит генератор импульсов, формирователь импульсов, пять триггеров, шесть элементов И-НЕ, пять элементов И, три элемента И-ИЛИ элемент ИЛИ, первый и второй инверторы, шесть элементов дифференцирования, дешифратор, выход генератора

О6импульсов подключен к входу формирователя импульсов, первьш выход которого подключен к одному входу первог элемента И, а второй выход является первым выходом блока управления и через первый инвертор подключен к входу первого элемента дифференцирования, выход первого элемента И подключен к С-входу первого триггера и через второй инвертор - к входу второго элемента дифференцирования, прямой выход первого триггера подключен к первому входу дешифратора и через третий элемент дифференцирования - к одному входу второго элемента И, инверсный выход, первого триггера подключен к его D-входу, второму входу дешифратора и через четвертый элемент дифференцирования - к одному входу третьего элемента И, выход первого элемента И-ИЛИ подключен к С-входу второго триггера, прямой выход которого подключен к третьему входу дешифратора и к входу пятого элемента дифференгц рования, а инверсный выход - к D-входу второго триггера, к четвертому входу дешифратора и к входу шестого элемента дифференцирования, выходы второго, третьего элементов И, пятого, шестого элементов дифференцирования подключены к соответствующим входам элемента РШИ, выход которого подключен к С-входу третьего триггера, D-вход которого соединен с шиной единичного потенциала, а выход подключен к одним входам первого и второго элементов И-НЕ и к одним входам четвертого и пятого элементов И, первый, второй, третий, четвертый выходы дешифратора подключены к другим входам соответственно первого, второго элементов И-НЕ, четвертого и пятого элементов И и являются соответственно вторым, третьим, четвертым и пятым выходами блока управления, выход первого элемента дифференцирования является шестым выходом блока управления и подключен к R-входу третьего триггера и к С- входам четвертого и пятого триггеров первые входы первой и второй пар входов второго элемента И-ИПИ являются соответственно первым и вторым входами блока управления, вторые входы первой и второй пар входов второго элемента И-ИЛИ соединены соответственно с вторым и дервыми выходами дешифратора, а выход второго элемента И-ИЛИ подключен к D-входу

четвертого триггера, прямой выход которого подключен к одним входам третьего и четвертого элементов И-НЕ другие входы которых соединены соответственно с первым и вторым выходами дешифратора, а выходы подключены к одним входам соответственно пятого и шестого элементов И-НЕ, другие входы пятого и шестого элементов И-Н соединены с выходами соответственно первого и второго элементов И-НЕ, первые входы первой, второй и третье пар входов третьего элемента И-ИЛИ соединены с первым входом первой пары входов второго элемента И-ИЛИ, а вторые входы соединены соответственно с первым, третьим и четвертым выходами дешифратора, выход.третьего элемента И-ИЛИ подключен к D-входу пятого триггера, прямой и инверсный выходы которого подключены к другим входам второго и третьего элементов И соответственно, инверсный выход четвертого триггера подключен к другому входу первого элемента И, входы первой группы входов первого элемента И-ИЛИ соединены с прямым выходом первого триггера, инверсным выходом пятого триггера и выходом второго элемента дифференцирования, входы второй группы входов первого элемента И-ИЛИ соединены с инверсным выходом первого триггера, прямым выходом пятого триггера и выходом второго элемента дифференцирования, а выходы пятого и шестого элементов И-НЕ и четвертого и пятого лементов И являются группой выходов блока управления.

3. Преобразователь по п. 1, отличающийся тем, что формирователь выходных импульсов содержит шестнадцать элементов И-НЕ, первый и второй инверторы, четыре элемента дифференцирования, восемь элементов ИЛИ-НЕ, первый и второй триггеры, входы первого и второго инверторов являются соответственно первым и вторым входами формирователя выходных импульсов, вход первого инвертора подключен к первым входам перврго, второго, третьего и четвертого элементов И-НЕ., выход первого инвертора подключен к первым входам пятого,

шестого, седьмого и восьмого элементов И-НЕ, вход второго инвертора подключен к первым входам девятого, десятого, одиннадцатого и двенадцато

, Е55

, 09310 -8

го элементов И-НЕ, выход второго инвертора подключен к первым входам тринадцатого, четырнадцатого, пятнадцатого и шестнадцатого элементов И-НЕ,

с второй вход первого элемента И-НЕ соединен с вторыми входами третьего,пятого, седьмого, десятого, двенадцатого, четырнадцатого и шестнадцатого элементов И-НЕ и является третьим входом фор-

fO мирователя,второй вход второго элемента И-НЕ соединен с вторыми входами четвертого, шестого, восьмого, девятого, одиннадцатого, тринадцатого и пятнадцатого элементов И-НЕ и яв15 ляется четвертым входом формирователя, третий вход девятого элемента И-НЕ соединен с третьими входами двенадцатого, четырнадцатого и пятнадцатого элементов И-НЕ и является пя- 20 тым входом формирователя, третий вход первого элемента И-НЕ соединен с третьими входами четвертого, шестого и седьмого элементов И-НЕ и является шестым входом формирователя,

25 третий вход второго элемента И-НЕ

соединен с третьими входами третьего, пятого и восьмого элементов И-НЕ и является седьмым входом формирователя, третий вход десятого элемента

30 И-НЕ соединен с третьими входами одиннадцатого, тринадцатого и шестнадцатого элементов И-НЕ и является восьмым входом формирователя, четвертый вход первого элемента И-НЕ сое35 динен с четвертыми входами элементов И-НЕ с второго по шестнадцатый и является девятым входом формирователя, вход и выход первого Инвертора через первый и второй элементы дифференци40 рования соответственно подключены к одним входам первого и второго элементов ИЛИ-НЕ, выходы первого, второго, пятого и шестого элементов И-НЕ подключены к входам третьего элемен45 та ИЛИ-НЕ, выход которого подключен к другому входу первого элемента ИЛИ-НЕ, выходы третьего, четвертого, седьмого и восьмого элементов И-НЕ подключены к входам четвертого эле-

50 мента ИЛИ-НЕ. выход которого подключен к другому входу второго элемента ИЛИ-НЕ, выходы первого и второго элементов ИЛИ-НЕ подключены соответственно к S- и R-входам первого триггера, выход которого является первым выходом формирователя, вход и выход второго инвертора через третий и четвертый элементыдифференцирования соовтетственно подключены к одним

входам пятого и шестого элементов ИЛИ-НЕ, выходы девятого, десятого, .тринадцатого и четырнадцатого элементов подключены к входам седьмого элемента ИЛИ-НЕ, выход которого подключен к другому входу пятого элемента ИЛИ-НЕ, выходы одиннадцатого, двенадцатого, пятнадцатого и

I t/oiia f

н1309310-10

шестнадцатого элементов И-ЙЕ подключены к входам восьмого элемента ИЛИ- НЕ, выход которого подключен к другому входу шестого элемента ИЛИ-НЕ, 5 выходы пятого и шестого элементов ИЛИ- НЕ подключенысоответственно к 5 -иК- входам второго триггера,выход которого является вторым выходом формирователя.

Пряной cttem

.S

Обратный сует

V,

ImiiiiinMi.i « I «

1Гш|||||||||||||||||||||||| ||||||||

/г |l|I jifIII

Illltl.11l.ll

111 |i|I ч

llftinnnnrtll

Ml

I yhttt

ПППП|ф|ПППП |11.1

II

1{ ПППП|ф|ППП

/TjJL

||||

II

.ll

tt

II

|ПППП |11.1

1{ ПППП|ф|ППП

-I-HWinnnnmnnnn

It

ППП

w

Редактор Л.Лангаэо

Составитель М.Сидорова

Техред М.Ходанич Корректор А.Обручар

1804/56

Тираж 902 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1986 |

|

SU1381705A1 |

| Преобразователь синусоидальных сигналов перемещения в код | 1984 |

|

SU1234968A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1989 |

|

SU1644382A1 |

| Устройство для измерения коэффициента прямоугольности амплитудно-частотной характеристики радиоприемников | 1990 |

|

SU1755383A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1984 |

|

SU1233283A1 |

| Цифровой электромагнитный толщиномер | 1988 |

|

SU1839228A1 |

| Позиционный электропривод с инди-КАциЕй пЕРЕМЕщЕНия МЕХАНизМА | 1979 |

|

SU809051A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в преобразователях перемещения в код. С целью по- вьшения точности преобразователя путем уменьшения погрешности формирования опорного напряжения в преобразователь синусно-косинусных сигналов в последовательность импульсов, со- держаший первый и второй нуль-органы, входы которых являются соответственно первым и вторым входами преобразователя и подключены к информационным входам первого и второго выпрямителей, а выходы первого и второго нуль-органов подключень соответственно к первому и второму входам формирователя выходных импульсов, резис- тивный делитель напряжения, третий нуль-орган, введены блок ключей, блок управления, инвертор, йервый и второй элементы И, триггер. Блок управления содержит генератор импульсов, формирователь импульсов, шесть элементов И-НЕ, пять элементов И, три элемента H-PfflH, элемент ИЖ-НЕ, два инвертора, шесть элементов дифференцирования, дешифратор. Формирователь выходных импульсов содержит шестнадцать элементов И-НЕ, два инвертора, четыре элемента дифференцирования, восемь элементов ИЛИ-НЕ и два триггера. Первый и второй нуль- органы формируют код квадранта. Выходное напряжение выпрямителей поступает на входы резистивного делителя напряжений, который работает в режиме фазорасщепителя. В зависимости от соотношений между амплитудами входных сигналов преобразователя срабатывают определенные ключи, в блоке управления формируются единичные сигналы на определенных выходных шинах. Из вькодных сигналов первого и второго нуль-органов, триггера и блока управления в формирователе выходных импульсов формируются две последовательности импульсов с дискретностью, соответствующей числу градаций в ре- зистивном делителе напряжения внутри квадранта. 2 з.п. ф-лы, 6 ил. i (Л оо о со 00

| Устройство для измерения угловых и линейных перемещений | 1974 |

|

SU480103A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Патент ФРГ № 1945206, кп | |||

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-17—Подача