мещения на одном из двух входов в зависимости от направления перемещения. Для определения работоспособности преобразователя в него введены делитель 7 частоты, триггер 8, элемент 9 И и регистр 6 управления который определяет работу преобразователя в режиме контроля или в режиме измерения. В режиме контроля с промежуточного выхода делителя 7 на информациИзобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством.

Целью изобретения является повьше- ние достоверности преобразователя.

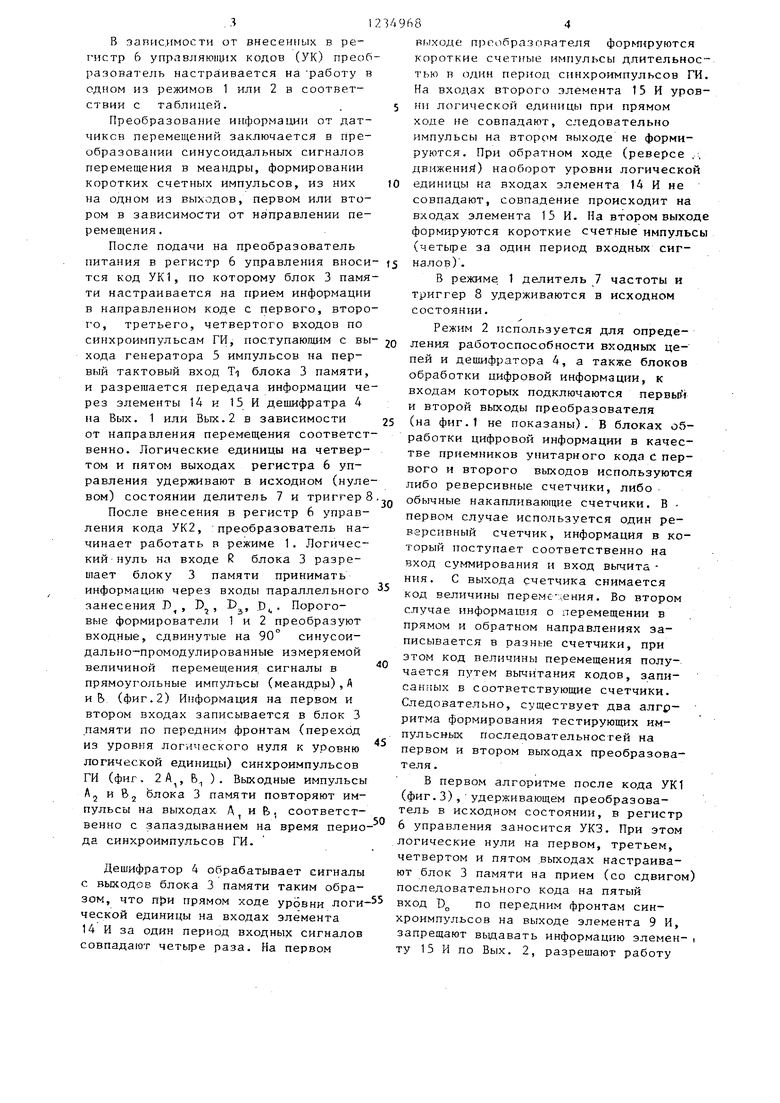

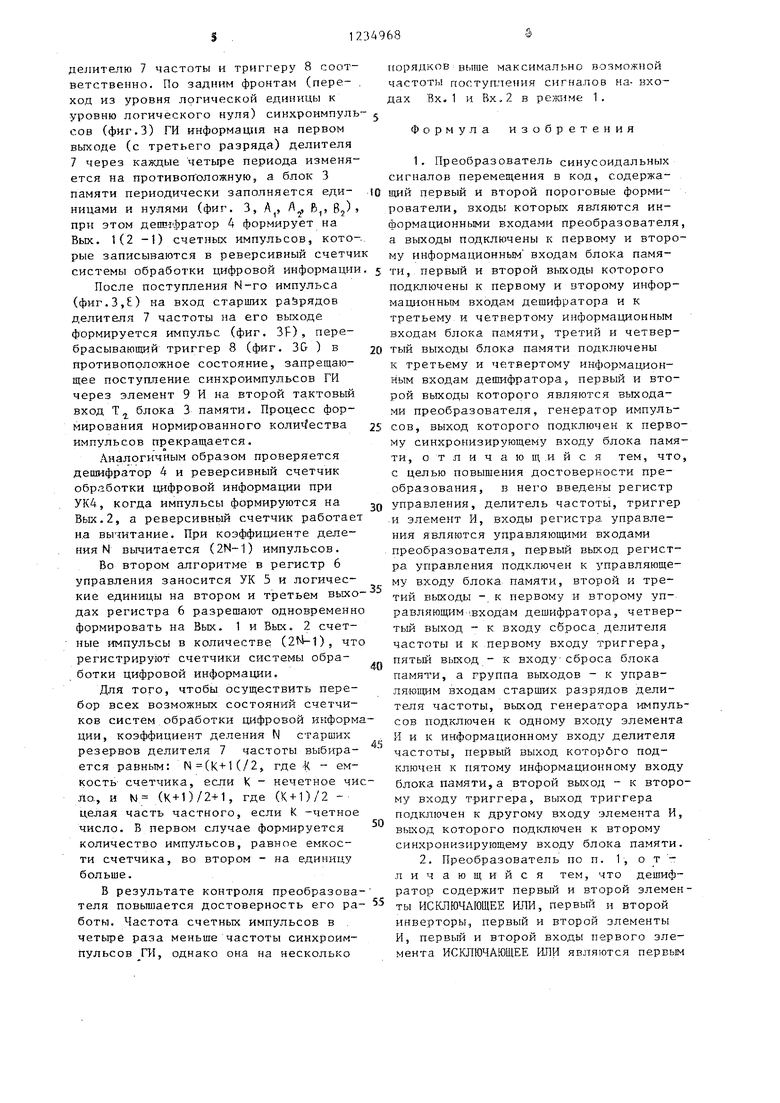

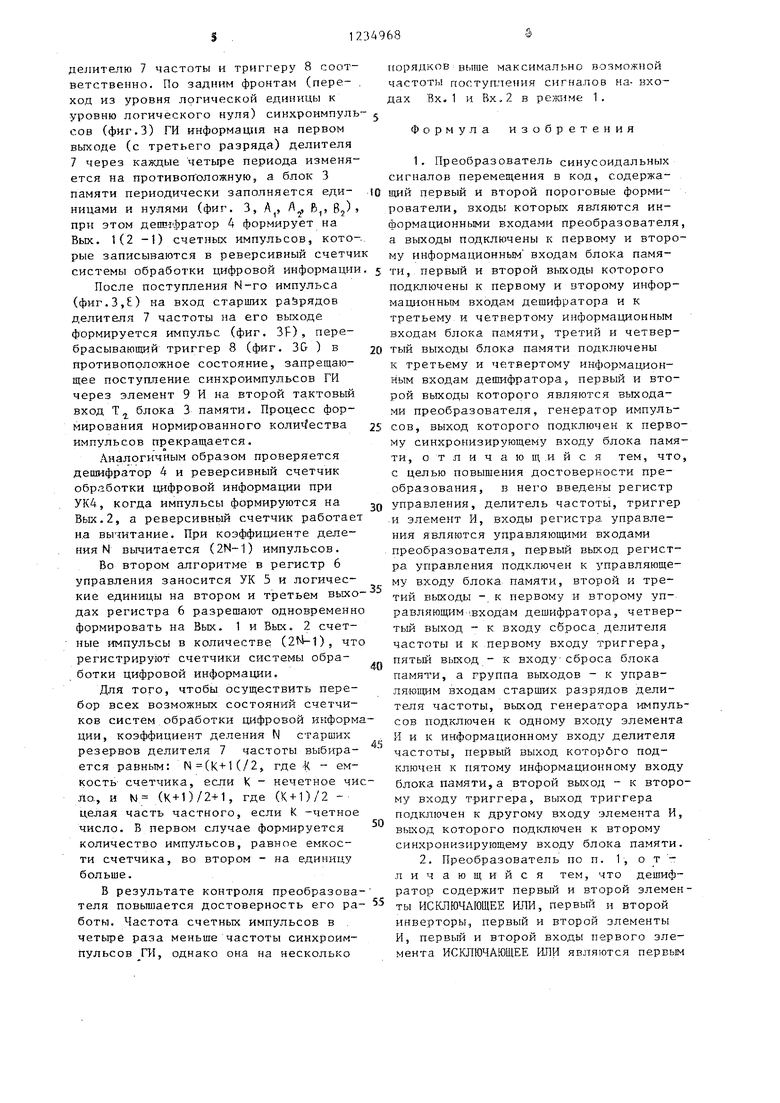

На фиг.1 представлена структурная схема преобразователя; на фиг. 2 - временная диаграмма работы преобразователя с датчиком перемещения, режим 1; на фиг. 3 - временная диаграм- м а контроля преобразователя, режим 2.

Преобразователь содержит первый I и второй 2 пороговые формирователи, входы которых Вх.1 и &Х.7 явля ются информационными входами преобразователя, а выходы Л и Б подключены к первому и второму информационным входам блока 3 памяти, первьй А, и второй В, выходы которого подключены к первому и второму информационным входам дешифратора 4 и к третьему и четвертому информационным входам блока 3, третий А , и четвертый В выходы блока 3 подключены к третьему и четвертому информационным входам дешифратора 4, первый Вых.1 и второй Вых. 2 выходы которого являются выходами преобразователя, генератор 5 импульсов, выход которого подключен к первому синхронизирующему входу блока 3, входы регистра 6 управления являются управляющими входами преобразователя, первый вькод регистра 6 подключён к управляющему входу блока 3, второй и третий выходы - к первому и второму управляющим входам дешифратора 4, четвертый вы- х.од - к входу сброса делителя 7 часонный вход блока 3 поступают импульсы, имитируюдае приращение перемещения, а через элемент 9 И поступают синхронизирующие импульсы. По окончании цикла проверки на вькод преобразователя должно поступить определенное количество импульсов, которое сравнивается с расчетным ипо результату сравнения определяют работоспособность преобразователя.1з.п.ф-лы,Зил,,1табл.

тоты, к первому входу триггера 8, пятый выход - к входу сброса блока 3, группа выходов - к.управляющим входам старших разрядов делителя 7, выход генератора 5 импульсов подключен- к одному входу элеента 9 И и к информационному входу елителя 7 частоты, первый выход которого подключен к пятому информационному входу блока 3, а второй выход- к второму входу триггера 8, выход триггера 8 подключен к другому входу элемента 9 И, выход которого подключен к другому синхронизирующему входу

блока 3 памяти.

Дешифратор 4 содержит первый 10 и второй 11 элементы ИСКЛЮЧА1ЩЕЕ ИЛИ, первый 12 и зторой 13 инверторы, первый 14 и второй 15 .элементы И, первый

и второй входы элемента 10 являются первьм и четвертым информационными входами депшфратора 4, первый и второй входы элемента 11 являются вторым и третьим информационными входами- дешифратора 4, выход элемента 10 и выход элемента 11 через первый 12 и второй 13 инверторы подключены к первым входам с и D, первого 14 и 15 элементов И, вторые входы которых

соединены с выходами элементом 11 и 10 соответственно, третьи входы яв- паются первым и вторым управляющими входами депмфратора 4, а вькоды эле- ментов 14 и 15 являются первым и

вторым, выходами дешифратора. 4. Первый и второй вькоды делителя 7 частоты обозначены F и Г- , выход триггера 8 -G, четвертый вькод регистра 6 - Н.

Преобразователь работает следующим образом.

. 31

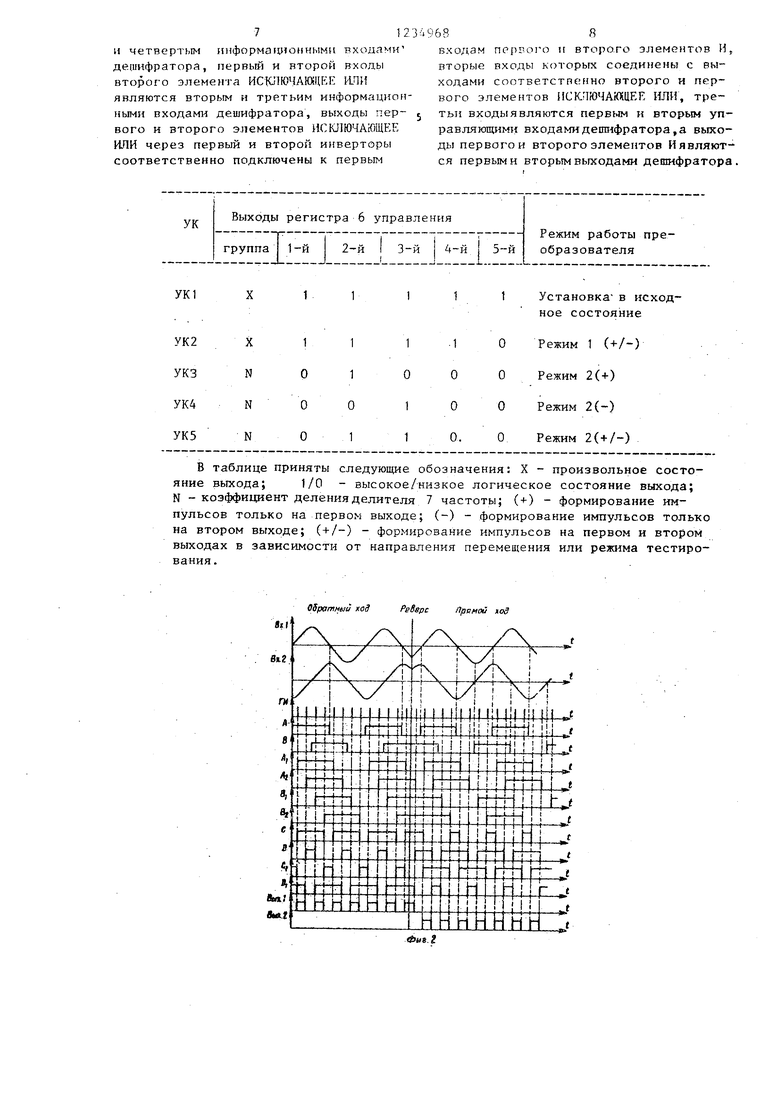

в запис.имостн от внесенных в регистр 6 управляющих кодов (УК) преоб разователь настраивается на работу в одном из режимов 1 или 2 в соответствии с таблицей.

Преобразование информации от датчиков перемещений заключается в преобразовании синусоидальных сигналов перемещения в меандры, формировании коротких счетных импульсов, из них на одном из выходов, первом или втором в зависимости от направлении перемещения.

После подачи на преобразователь питания в регистр 6 управления вноси тся код УК1, по которому блок 3 памя ти настраивается на прием информации в направленном коде с первого, второ го, третьего, четвертого входов по синхроимпульсам ГИ, поступающим с вы хода генератора 5 импульсов на пер- вый тактовый вход Ti блока 3 памяти, и разрешается передача информации че рез элементы 14 и 15 И дешифратра 4 на Вых. 1 или Вьгх.2 в зависимости от направления перемещения соответст венно. Логические единицы на четвертом и пятом выходах регистра 6 управления удерживают в исходном (нуле вом) состоянии делитель 7 и триггере

После внесения в регистр 6 управления кода УК2, :преобразователь начинает работать в режиме 1. Логический нуль на входе R блока 3 разрешает блоку 3 памяти принимать информац1-1ю через входы параллельного занесения D, , D , D, .D . Пороговые формирователи 1 и 2 преобразуют входные, сдвинутые на 90° синусои- дально-промодулированные измеряемой величиной перемещения сигналы в прямоугольные импулъсы (меандры),А и 5 (фиг.2) Информация на первом и втором входах записывается в блок 3 .памяти по передним фронтам (переход из уровня Логического нуля к уровню логической единицы) синхроимпульсов ГИ (фиг, 2А, В ). Выходные импульсы А2 и БЗ Ьлока 3 памяти повторяют импульсы на выходах Д и В. соответственно с запаздыванием на время периода синхроимпульсов ГИ.

Дешифратор 4 обрабатывает сигналы с выходов блока 3 памяти таким образом, что при прямом ходе уровни логической единицы на входах эле мента 14 И за один период входных сигналов совпадают четыре раза. На первом

149684

вр,.|ходе прробразорателя фор№{руются короткие счетные импульсы длительностью в один период синхроимпульсов ГИ. На входах второго элемента 15 И уров- 5 mi логической единицы при прямом ходе не совпадают, следовательно импульсы на втором выходе не формируются. При обратном ходе (реверсе ,:, движений) наоборот уровни логической 10 единицы на входах элемента 14 И не совпадают, совпадение происходит на входах элемента 15 И. На втором выходе формируются короткие счетные импульсы (четьфе за один период входных сигt5 налов).

В режиме 1 делитель 7 частоты и триггер 8 удерживаются в исходном состоянии.

Режим 2 используется для опреде- 20 ления работоспособности входных цепей и дешифратора 4, а также блоков обработки цифровой информации, к входам которых подключаются первьй и второй вьгходы преобразователя 25 (на фиг.1 не показаны). В блоках обработки цифровой информации в качестве приемников унитарного кода С первого и второго выходов используются либо реверсивные счетчики, либо Зд обычные накапливающие счетчики. В - первом случае используется один реверсивный счетчик, информация в который пост пает соответственно на вход суммирования и вход вычита НИН. С выхода счетчика снимается код величины переме дения. Во втором случае информашш о перемещении в прямом и обратном направлениях записывается в разные счетчики, при

этом код величины перемещения полу- 40

чается путем вычитания кодов, записанных в соответствующие счетчики. Следовательно, существует два алгр- ритма формирования тестирующих импульсных последовательностей на первом и втором выходах преобразователя.

В первом алгоритме после кода УК1 (фиг.3), удерживающем преобразователь в исходном состоянии, в регистр 6 управления заносится УКЗ. При этом логические нули на первом, третьем, четвертом и пятом выходах настраивают блок 3 памяти на прием (со сдвигом) последовательного кода на пятый 5 вход Вд по передним фронтам синхроимпульсов на выходе элемента 9 И, запрещают вьщавать информацию элемен- i ту 15 И по Вых. 2, разрешают работу

35

5

делителю 7 частоты и триггеру 8 соответственно. По задним фронтам (пере- ход из уровня логической единицы к уровню логического нуля) синхроимпуль сов (фиг.З) ГИ информация на первом выходе (с третьего разряда) делителя 7 через каждые четьфе периода изменяется на противоположную, а блок 3 памяти периодически заполняется еди- ницами и нулями (фиг. 3, А, А R, В,) при этом дешифратор 4 формирует на Вых. 1(2 -1) счетньЕХ импульсов, которые записываются в реверсивный счетчи системы обработки цифровой информации

После поступления N-ro импульса (фиг.ЗД) на вход старших разрядов делителя 7 частоты на его выходе формируется импульс (фиг. 3F), перебрасывающий триггер 8 (фиг. 3& ) в противоположное состояние, запрещающее постуапение синхроимпульсов ГИ через элемент 9 И на второй та.ктовый вход Т блока 3 памяти. Процесс формирования нормированного коли ества импульсов прекращается..

Аналогичным образом проверяется дешифратор 4 и реверсивный счетчик обработки цифровой информации при УК4, когда импульсы формируются на Вых.2, а реверсивньш счетчик работае н.а вычитание. При коэффип енте деления N вычитается () импульсов. Во втором алгоритме в регистр 6 управления заносится УК 5 и логические единицы на втором и третьем выхо дах регистра 6 разрешают одновременн формировать на Вых. 1 и Вых. 2 счетные импульсы в количестве (), чт регистрируют счетчики системы обработки цифровой информации.

Для того, чтобы осуществить перебор всех возможных состояний счетчиков систем . обра.ботки цифровой информции, коэффициент деления N старших резервов делителя 7 частоты выбира- ется равным: N(K+t(/2, где -К - емкость счетчика, если К - нечетное чило,, и М (К + 1)/2+1, где (К + 1)/2 - целая часть частного, если К четное число. В первом случае формируется количество импульсов, равное емкости счетчика, во втором - на единицу больше.

В результате контроля преобразова теля повьпиается достоверность его ра- боты. Частота счетных импульсов в четьфе раза меньше частоты синхроимпульсов ГИ, однако она на несколько

.

, - J Q .. к . 5

20 25

„

5

35

4«

г орядков выше максимально возможной частоты поступления сигна.пов на- входах Вх,1 и Вх,2 в режиме 1.

Формула изобретения

1.Преобразователь синусоидальных сигналов перемещения в код, содержащий первый и второй пороговые формирователи, входы которых являются информационными входами преобразователя, а выходы подключены к первому и второму информационным входам блока памяти, первый и второй выходы которого подключены к первому и второму информационным входам дешифратора и к третьему и четвертому информационным входам блока памяти, третий и четвертый выходы блока памяти подключены

к третьему и четвертому информационным входам дешифратора, первый и второй выходы которого являются выходами преобразователя, генератор импульсов, выход которого подключен к первому синхронизирующему входу блока памяти, о т л и ч а ш щ .и и с я тем, что, с целью повышения достоверности преобразования, в него введены регистр управления, делитель частоты, триггер и элемент И, входы регистра управления являются управляющими входами преобразователя, первый выход регистра управления подключен к управляющему входу блока памяти, второй и третий выходы - к первому и второму управляющим .входам дешифратора, четвертый выход - к входу сброса делителя частоты и к первому входу триггера, пятьш выход - к входу сброса блока памяти, а группа выходов - к управляющим входам старших разрядов делителя частоты, выход генератора импульсов подключен к одному входу элемента И и к информационному входу делителя частоты, первый выход которбго подключен к пятому информационному входу блока памяти, а второй выход - к второму входу триггера, выход триггера подключен к другому входу элемента И, выход которого подключен к второму синхронизирующему входу блока памяти.

2.Преобразователь по п. Г, о т - л и ч а ю щ и и с я тем, что дешифратор содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первьй н второй инверторы, первый и второй элементы

И, первый и второй входы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются первым

712

и четвертым информафюнными входами дешифратора, первый и второй входы второго элемента ИСКПЮЧАНХЦЕЕ аПИ являются вторым и третьим информацнон нымн входами дешифратора, выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ И.ПИ через первый и второй инверторы соответственно подключены к первым

УК1

В таблице приняты следующие обозначения: X - произвольное состояние выхода; 1/0 - высокое/низкое логическое состояние выхода; N - коэффициент деления делителя 7 частоты; () - формирование импульсов только на первом выходе; (-) - формирование импульсов только на втором выходе; (+/-) - формирование импульсов на первом и втором выходах в зависимости от направления перемещения или режима тестирования .

OSpamHi/tf xOf

3.9688

входам первого и второго элементов И, вторые входы которых соединены с выходами соответственно второго и первого элементов 11СКПЮЧАЩЕЕ ИЛИ, тре- 5 тьи входы являются первым и вторым управляющими входами дешифратора, а выходы первогои второго элементов Иявляют- ся первыми вторьтмвыходами дешифратора.

Установка- в исходное состояние

feSspc n/isMOU ход

e«v

81 i

Дe

-Sr

e

s- t, в,

SmJ OMt

/Л

.V-v

IrCиfs

Л/1

I1rn1 TT T- T 1 .

ai M rri±mijjit

H

.З

Редактор К.Волощук

Составитель А.Смирнов

Техред О.Гортвай Корректор М.Демчик

2990/58

Тираж 816 Подписное ВНИИПИ Государственного комитета -СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

| Устройство для определения области работоспособности радиоэлектронных схем | 1986 |

|

SU1386947A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1418911A1 |

| Устройство для регистрации информации | 1988 |

|

SU1589315A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством, С целью повышения достоверности преобразователя путем контроля его работоспособности перед началом работы синусньш и косинусный сигналы с датчика перемещения через пороговые формирователи 1 и 2, соответственно, поступают на входы блока 3 памяти, выполненного в виде сдвигающего регистра, синхронизирующий вход которого соединен с генератором 5 импульсов. На выходе блока 3 формируются четыре последовательности прямоугольных сигналов, относительное расположение которых определяется направлением перемещения, т.е. последовательностью изменения входных сигналов пороговых формирователей 1 и 2. Дешифратор 4 в первом ремлме работы преобразователя формирует из выходных сигналов блока 3 последовательности liмпyльcoв приращения перес S л tsD СО 4ik 0 С5 оо

Авторы

Даты

1986-05-30—Публикация

1984-11-19—Подача