09 00

о ел

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровы вычислительным устройством.

Целью изобретения ярпяется повышение достоверности преобразователя путем формирования сигнала начала отсчета, что позволяет создать квазиабсолютную систему отсчета.

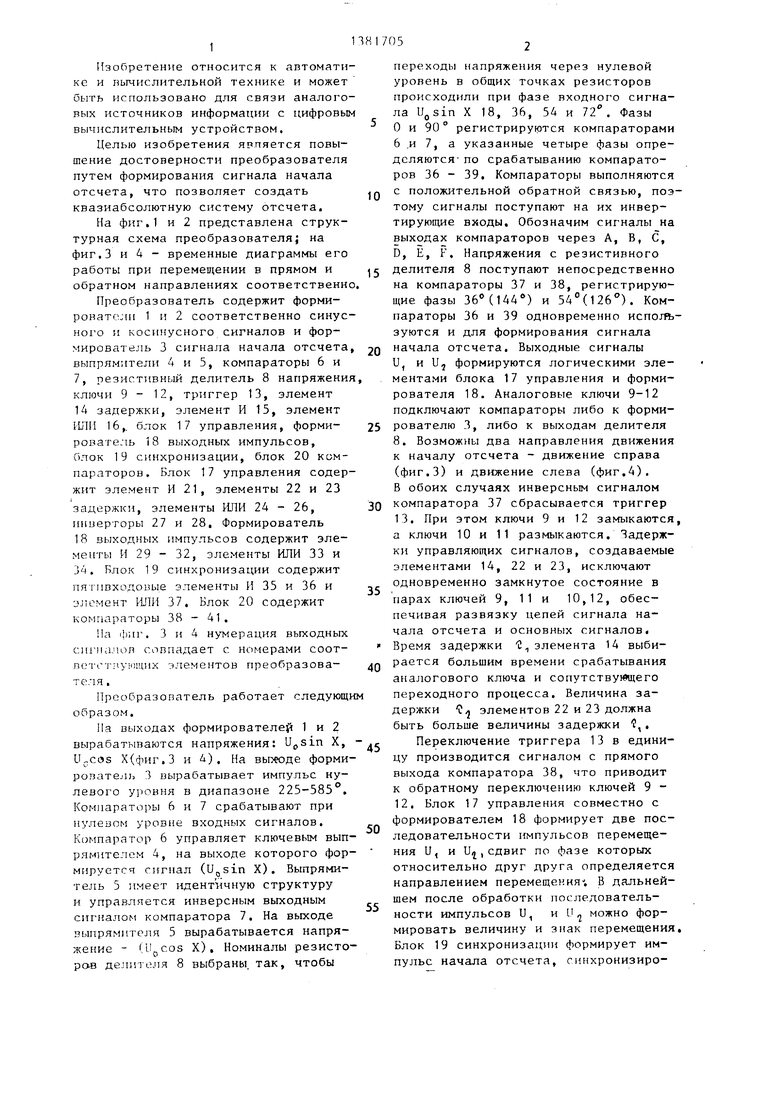

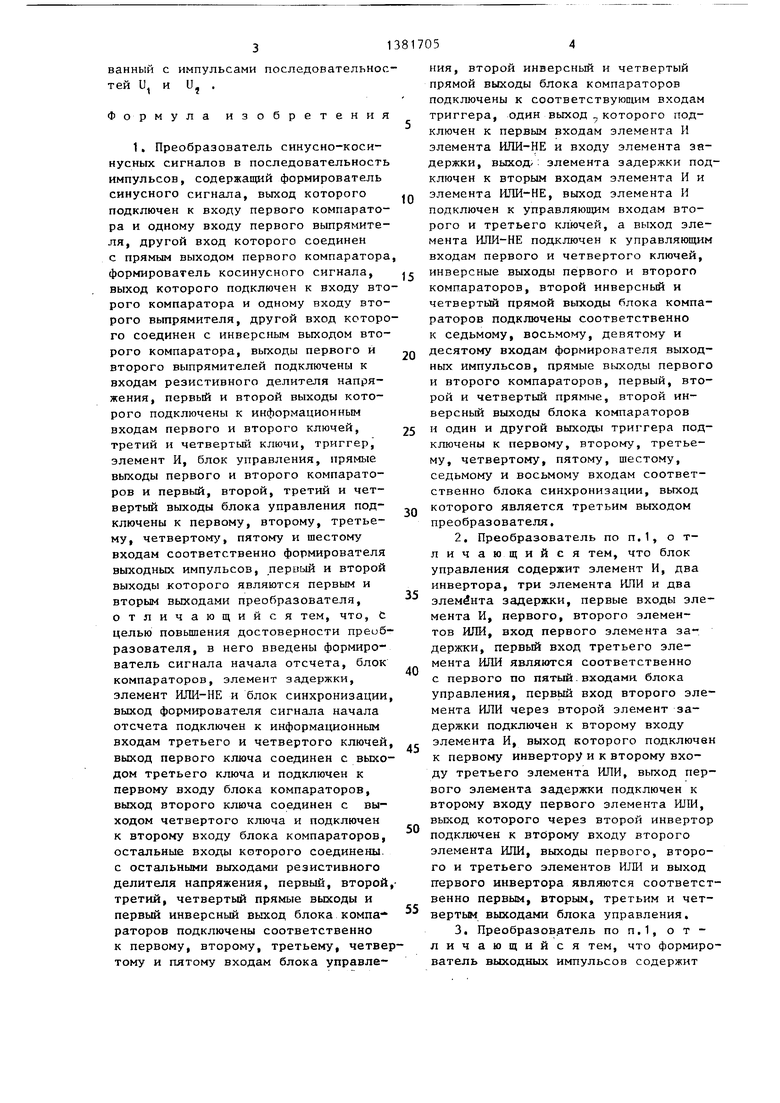

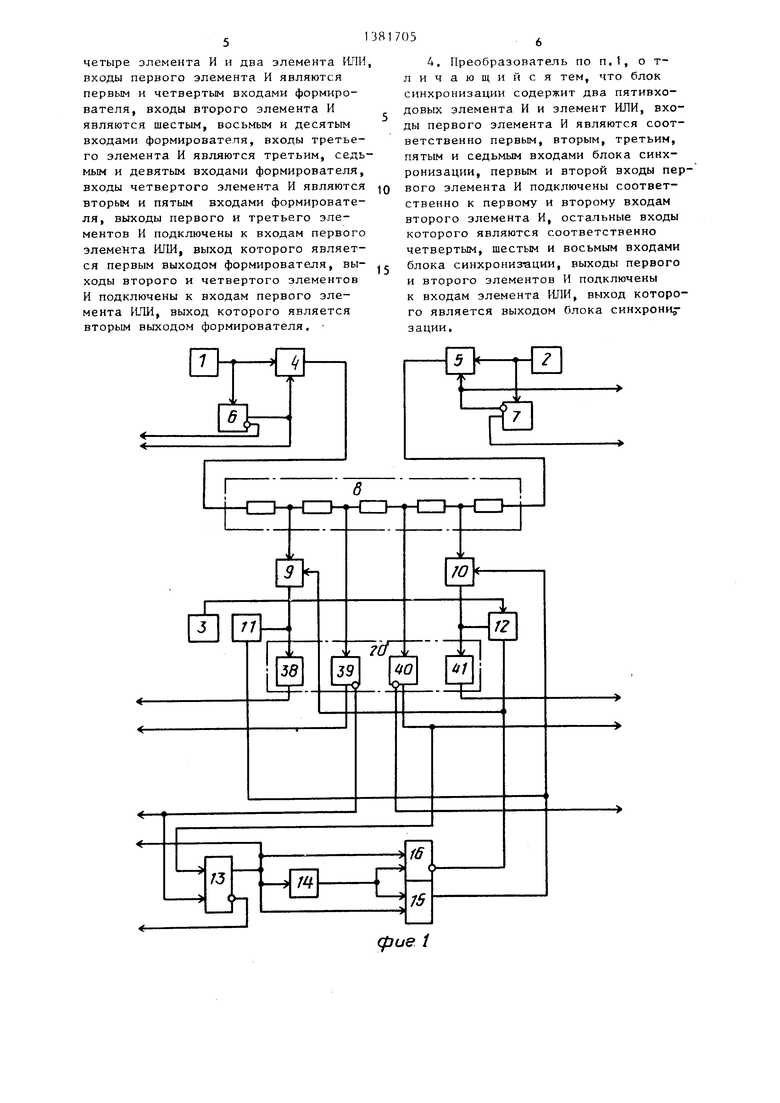

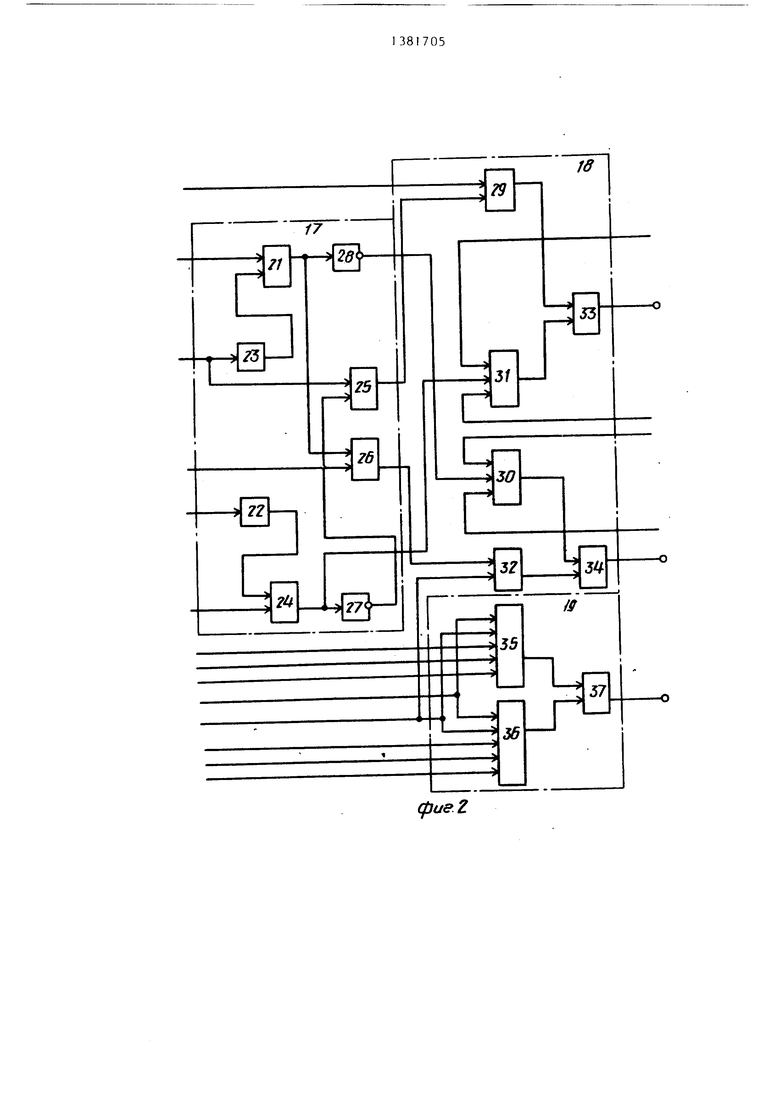

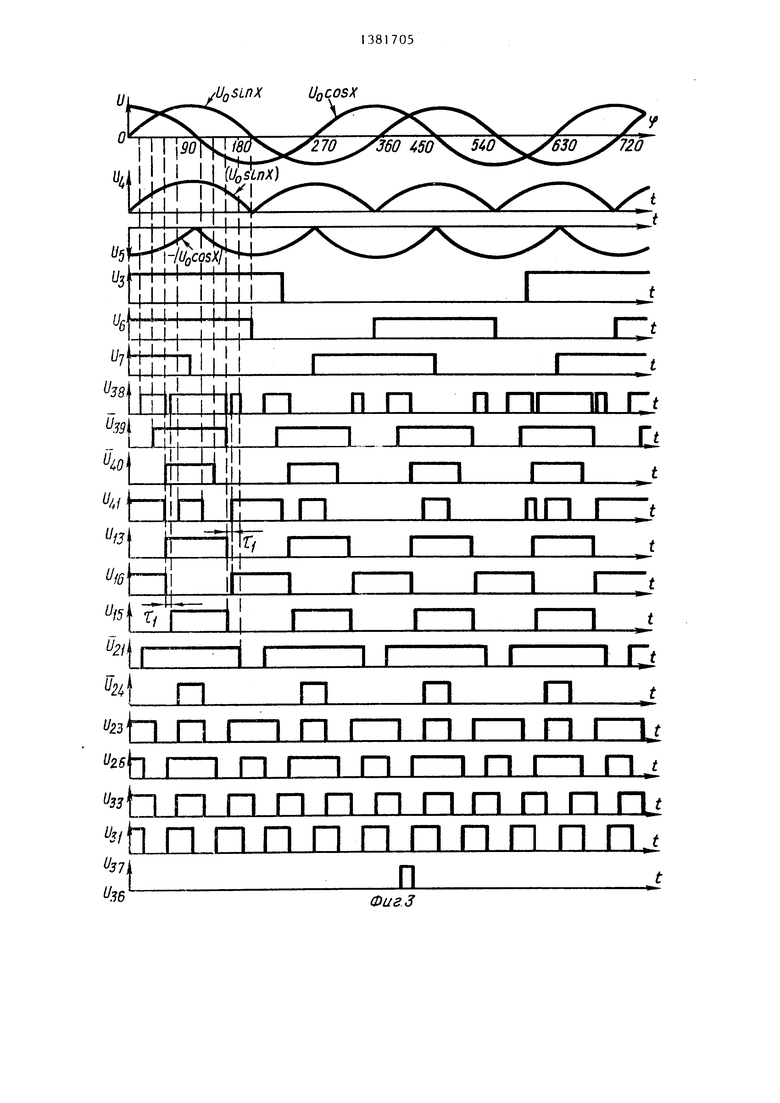

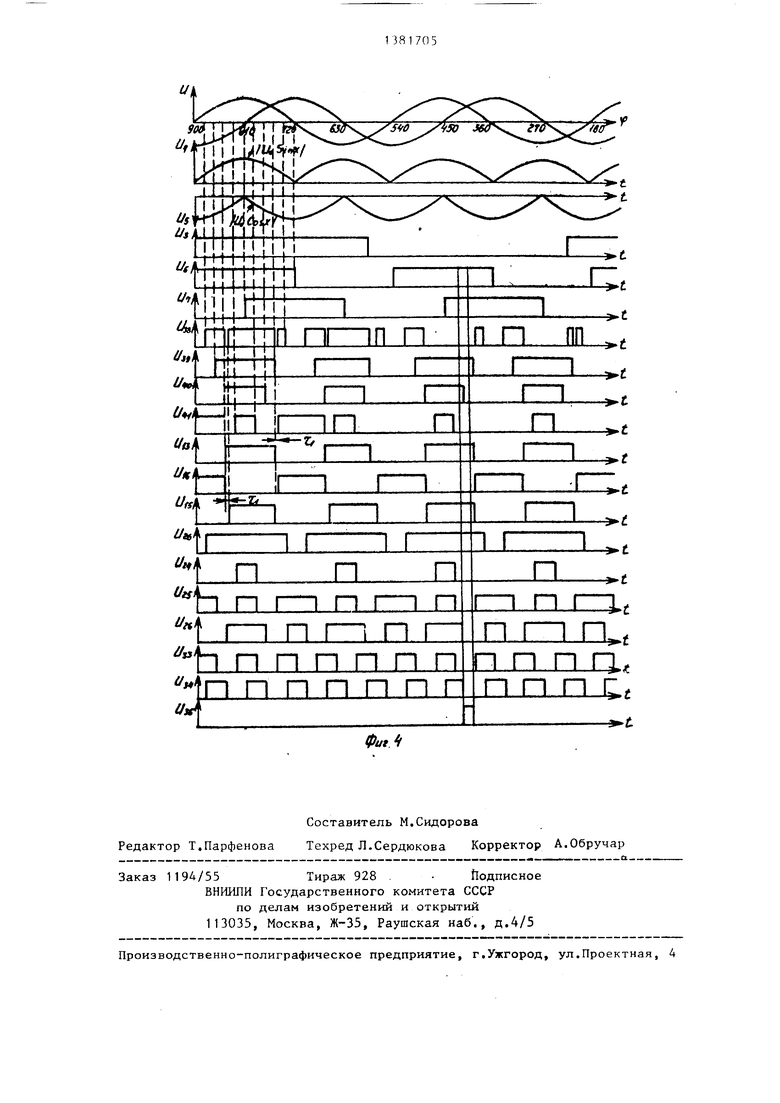

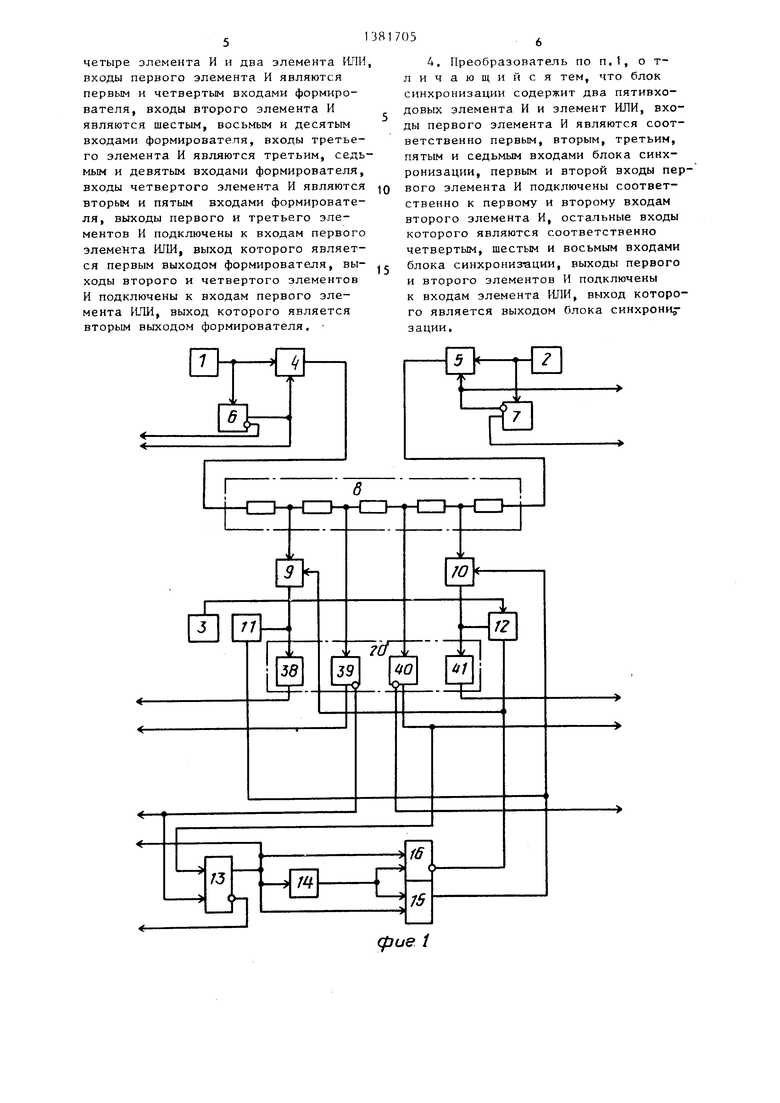

На фиг,1 и 2 представлена структурная схема преобразователя} на фиг.З и 4 - временные диаграммы его работы при перемещении в прямом и обратном направлениях соответственн

Преобразователь содержит форми- ронатс:п1 1 и 2 соответственно синусного и косинусного сигналов и формирователь 3 сигнала начала отсчета выпрямители ч и 5, компараторы 6 и 7, резистивный делитель 8 напряжени ключи 9 - 12, триггер 13, элемент 14 задержки, элемент И 15, элемент 1ШП 16,. блок 17 управления, форми- ровате.чь 18 выходных импульсов, блок 19 синхронизации, блок 20 компараторов. Блок 17 управления содержит элемент И 21, элементы 22 и 23

задержки, элементы ИЛИ 24 - 26, инверторы 27 и 28. Формирователь 18 выходных импульсов содержит элементы И 29 - 32, элементы ИЛИ 33 и 3, Влок 19 синхронизации содержит пя 1 1шходовые элементы И 35 и 36 и элемент ИЛИ 37. Блок 20 содержит комгияраторы 38 - 41.

Па фиг, 3 и 4 нумерация выходных сигиалоп совпадает с номерами соот- ветст;1ун)цих элементов преобразова- те. 1я.

Преобразователь работает следующ образом.

Па выходах формирователей 1 и 2 вырабатываются напряжения: X, UpCos Х(фиг.З и 4) . На форми ponaTejib 3 вырабатывает импульс нулевого у 1оння в диапазоне 225-585 . Компараторы 6 и 7 срабатывают при нулевом уровне входных сигналов. Компаратор 6 управляет ключевым выпрямителем 4, на выходе которого формируется сигнал ( X). Выпрямитель 5 имеет идентичную структуру и управляется инверсным выходным сигналом компаратора 7. На выходе выпрямителя 5 вырабатывается напряжение - (UpCos X), Номиналы резисто рав делителя 8 выбраны, так, чтобы

д

20 25

30

О

5

0

переходы напряжения через нулевой уровень в общих точках резисторов происходили при фазе входного сигнала Ugsin X 18, 36, 54 и 72. Фазы О и 90 ° регистрируются компараторами 6 ,и 7, а указанные четыре фазы определяются- по срабатыванию компараторов 36 - 39. Компараторы выполняются с положительной обратной связью, поэтому сигналы поступают на их инвертирующие входы. Обозначим сигналы на выходах компараторов через А, В, С, D, Е, Г . Нааряжения с резистивного делителя 8 поступают непосредственно на компараторы 37 и 38, регистрирующие фазы 36(144) и 54°(126°). Компараторы 36 и 39 одновременно испо/ть- зуются и для формирования сигнала начала отсчета. Выходные сигналы и, и Uj формируются логическими элементами блока 17 управления и формирователя 18. Аналоговые ключи 9-12 подключают компараторы либо к формирователю 3, либо к выходам делителя 8. Возможны два направления движения к началу отсчета - движение справа (фиг.З) и движение слева (фиг,4), В обоих случаях инверсным сигналом компаратора 37 сбрасывается триггер 13. При этом ключи 9 и 12 замыкаются, а ключи 10 и 11 размыкаются. Задержки управляющих сигналов, создаваемые элементами 14, 22 и 23, исключают одновременно замкнутое состояние в парах ключей 9, 11 и 10,12, обеспечивая развязку цепей сигнала начала отсчета и основных сигналов. Время задержки 2, элемента 14 выбирается большим времени срабатывания аналогового ключа и сопутству1 щего переходного процесса. Величина задержки С элементов 22 и 23 должна быть больше величины задержки ,,

Переключение триггера 13 в единицу производится сигналом с прямого выхода компаратора 38, что приводит к обратному переключению ключей 9 - 12. Блок 17 управления совместно с формирователем 18 формирует две последовательности импульсов перемещения и, и и,сдвиг по фазе которых относительно друг друга определяется направлением перемещения . В дальнейшем после обработки последовательности импульсов и, и и можно формировать величину и знак перемещения. Блок 19 синхронизации формирует импульс начала отсчета, синхронизироанныйей и.

импульсами

и. .

31381705

последовательноснипр по тр кл эл де кл эл по ро ме вх ин ко че ра к де ны и ро ве и кл му се ст ко пр

Формула изобретения

1. Преобразователь синусно-коси- нусных сигналов в последовательность импульсов, содержащий формирователь синусного сигнала, выход которого подключен к входу первого компаратора и одному входу первого выпрямителя, другой вход которого соединен с прямым выходом первого компаратора формирователь косинусного сигнала, выход которого подключен к входу второго компаратора и одному входу второго вьтрямителя, другой вход которого соединен с инверсным выходом второго компаратора, выходы первого и второго выпрямителей подключены к входам резистивного делителя напряжения, первый и второй выходы которого подключены к информационным входам первого и второго ключей, третий и четвертый ключи, триггер, элемент И, блок управления, прямые выходы первого и второго компараторов и первьй, второй, третий и четвертый выходы блока управления подключены к первому, второму, третьему, четвертом , пятому и шестому входам соответственно формирователя выходных импульсов, первый и второй выходы которого являются первым и вторым выходами преобразователя, отличающийся тем, что, t целью повышения достоверности преобразователя, в него введены формирователь сигнала начала отсчета, блок компараторов, элемент задержки, элемент ИЛИ-НЕ и блок синхронизации выход формирователя сигнала начала отсчета подключен к информадионнЕз1М входам третьего и четвертого ключей выход первого ключа соединен с выходом третьего ключа и подключен к первому входу блока компараторов, выход второго ключа соединен с выходом четвертого ключа и подключен к второму входу блока компараторов, остальные входы которого соединены, с остальными выходами резистивного делителя напряжения, первый, второй третий, четвертый прямые выходы и первый инверсный выход блока компа- раторов подключены соответственно к первому, второму, третьему, четветому и пятому входам блока управле

0

г n 5

5

0

5

0

5

ния, второй инверсный и четвертый прямой выходы блока компараторов подключены к соответствуюпщм входам триггера, один выход ., которого подключен к первьом входам элемента И элемента ИЛИ-НЕ и входу элемента задержки, выход-; элемента задержки подключен к вторым входам элемента И и элемента ИЛИ-НЕ, выход элемента И подключен к управляющим входам второго и третьего ключей, а выход элемента ИЛИ-НЕ подключен к управляющим входам первого и четвертого ключей, инверсные выходы первого и второго компараторов, второй инверсный и четвертый прямой выходы блока компараторов подключены соответственно к седьмому, восьмому, девятому и десятому входам формирователя выходных импульсов, прямые выходы первого и второго компараторов, первый, второй и четвертый прямые, второй инверсный выходы блока компараторов и один и другой выходы триггера подключены к первому, второму, третьему, четвертому, пятому, шестому, седьмому и восьмому входам соответственно блока синхронизации, выход которого является третьим выходом преобразователя,

2,Преобразователь по п.1, о т- л ич ающий с я тем, что блок управления содержит элемент И, два инвертора, три элемента ИЛИ и два элемента задержки, первые входы элемента И, первого, второго элементов ИЛИ, вход первого элемента задержки, первый вход третьего элемента ИЛИ являются соответственно

с первого по пятый -входамн блока управления, первый вход второго элемента ИЛИ через второй элемент задержки подключен к второму входу элемента И, выход которого подключен к первому инвертору и к второму входу третьего элемента ИЛИ, выход первого элемента задержки подключен к второму входу первого элемента ИЛИ, выход которого через второй инвертор подключен к второму входу второго элемента ИЛИ, выходы первого, второго и третьего элементов ИЛИ и выход первого инвертора являются соответственно первым, вторым, третьим и четвертым выходами блока управления,

3.Преобразователь по п.1, о т - личающийся тем, что формирователь выходных импульсов содержит

четыре элемента И н два элемента ИЛИ входы первого элемента И являются первым и четвертым входами формирователя, входы второго элемента И являются шестым, восьмью и десятым входами формирователя, входы третьего элемента И являются третьим, седьмым и девятым входами формирователя, входы четвертого элемента И являются вторым и пятым входами формирователя, выходы первого и третьего элементов И подключены к входам первого элемента ИЛИ, выход которого является первым выходом формирователя, вы- ходы второго и четвертого элементов И подключены к входам первого элемента ИЛИ, выход которого является вторым выходом формирователя.

.

0

4. Преобразователь по п.1, о т личающинся тем, что блок синхронизации содержит два пятивхо- довых элемента И и элемент ИЛИ, входы первого элемента И являются соответственно первым, вторым, третьим, пятым и седьмым входами блока синхронизации, первьм и второй входы первого элемента И подключены соответственно к первому и второму входам второго элемента И, остальные входы которого являются соответственно четвертым, шестым и восьмым входами блока синхронизации, выходы первого и второго элементов И подключены к входам элемента ИЛИ, выход которого является выходом блока синхрони зации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1985 |

|

SU1309310A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1989 |

|

SU1644382A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1115080A1 |

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1988 |

|

SU1737731A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1797161A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1128277A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU942095A1 |

| Преобразователь перемещений в код | 1983 |

|

SU1111188A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с циф- ровьм вычислительным устройством. С целью повышения достоверности путем формирования сигнала начала отсчета в преобразователь синусно-косинусныж сигналов в последовательность импульсов, содержащий формирователи синусного и косинусного сигналов, выпрямителя, компараторы, резистивный делитель напряжения, ключи, триггер, элемент И, блок управления, формирователь выходных импульсов, введены формирователь сигнала начала отсчета, элемент .задержки, элемент ИЛИ, блок синхронизации и блок компараторов. 3 з.п. ф-лы, 4 ил. сл

(рие i

(pueZ

UoSLnXUQCOSX

0

720

| Дж.Вульвет | |||

| Датчики в цифровых системах | |||

| М.: Энергоиздат, 1981, с.95-96, рис | |||

| Приспособление для плетения проволочного каркаса для железобетонных пустотелых камней | 1920 |

|

SU44A1 |

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1985 |

|

SU1309310A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-15—Публикация

1986-03-27—Подача