(54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1986 |

|

SU1316047A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Логическое запоминающее устройство | 1987 |

|

SU1566411A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

| Логическое запоминающее устройство | 1974 |

|

SU492934A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1088073A2 |

| Логическое запоминающее устройство | 1979 |

|

SU801101A2 |

1

Изобретение относится к запомина1ощим устройствам и .может быть использовано в системах сложной логической обработки данных.

Известно логическое запоминающее устройство, в которых логические операции реализуются за счет одновременного считывания из двух ячеек, содержащих операнды, и из третьей ячейки, содержащей константу, которой определяется вып-. )о полняемая логическая функция l.

Недостаток данного устройства - низкое быстродействие при выполнении сложных логических операций.

Наиболее близким к предлагаемому я&-|5 ляется логическое запоминающее устройство, содержащее накопитель с числовыми линейками на тороидальных ферритовых сердечниках с ППК, прошитых разрядными шинами записи и чтения и линейными ши- 20 нами записи и считывания, причем накопитель подключен к выходам разрядных формтфователей записи и к входам усилителей считывания, выходы которых подключены к триггерам регистра регенерации, выходы которых подключены к первой и второй грутшам элементов И, регистр ( слова, входы которого подключены к входам элементам ИЛИ, а выходы через разрядные элементы И и ИЛИ - к разрядным формирователям записи, адресные элементы И, одни входы которых подключены к выходам дешифратора, .другие - к выходам элементов ИЛИ управления, а выходы - к адресным форм11роватеп51м записи и сч тывания, элемент ИЛИ, входы которого подключены к соответствующим шинам управления, а выкощл - к раар$щным элементам И и к входам одного вз элементов ИЛИ управления Г 2.

Недостатком известного устройства является низкое быстродействие при выполнении операций нахождения совпадак щих элементов в массивах информации.

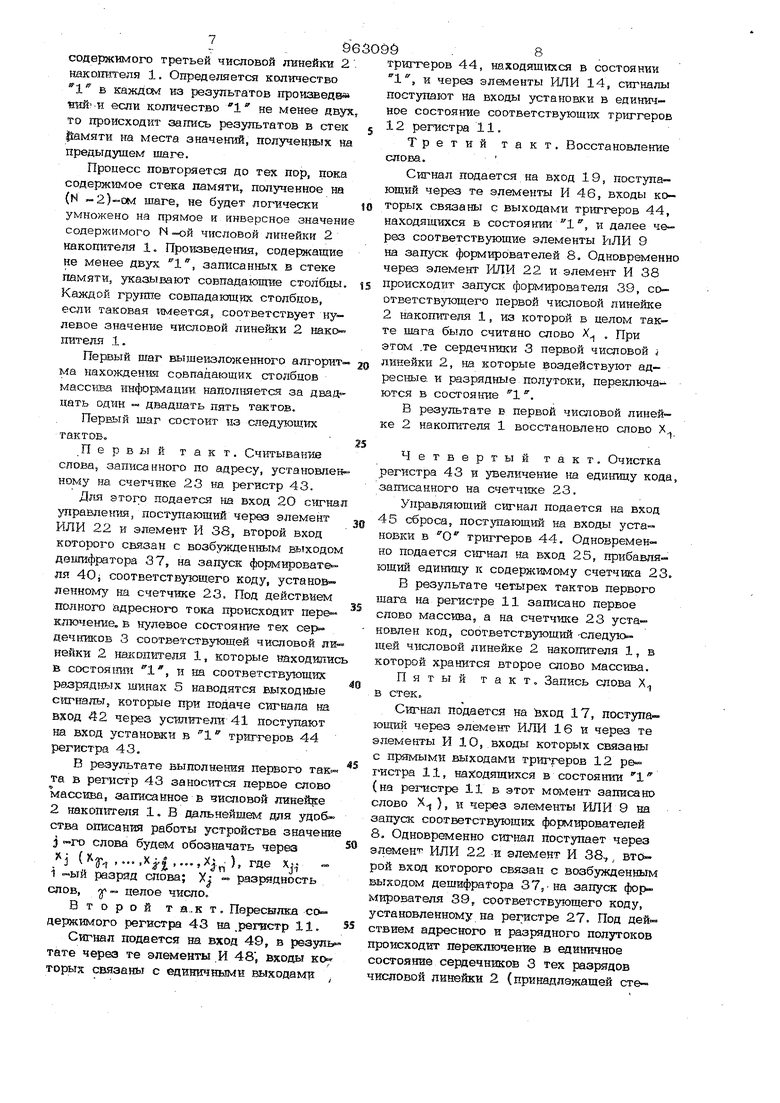

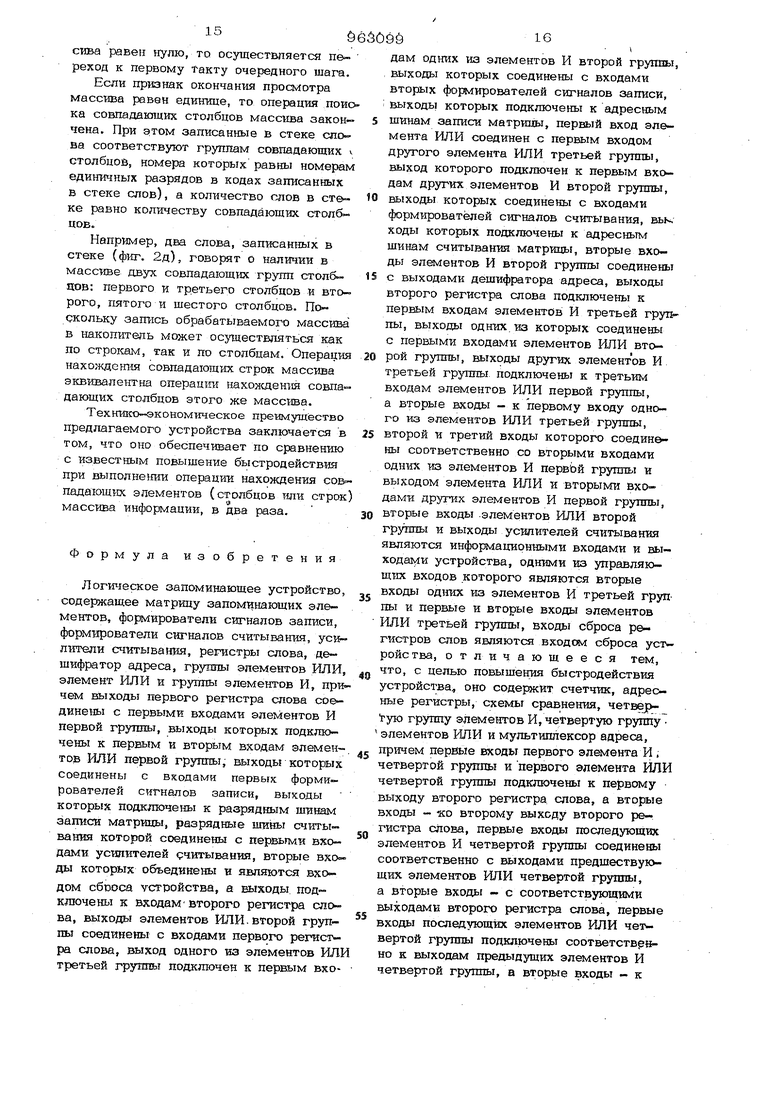

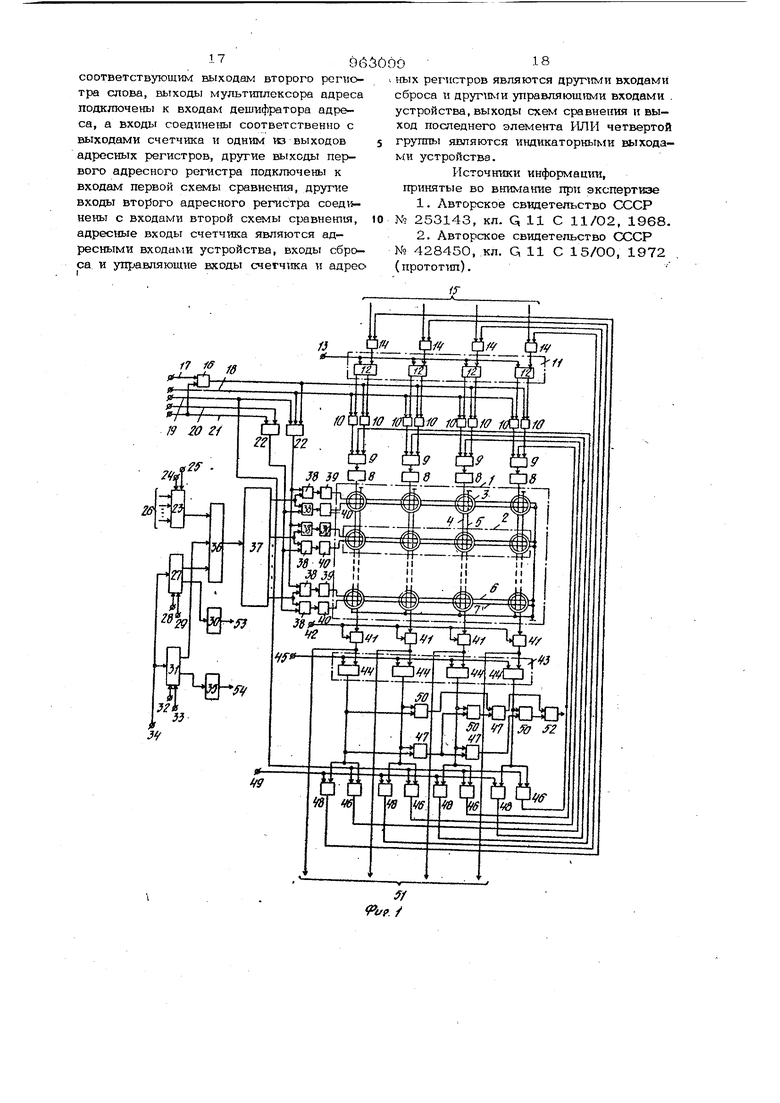

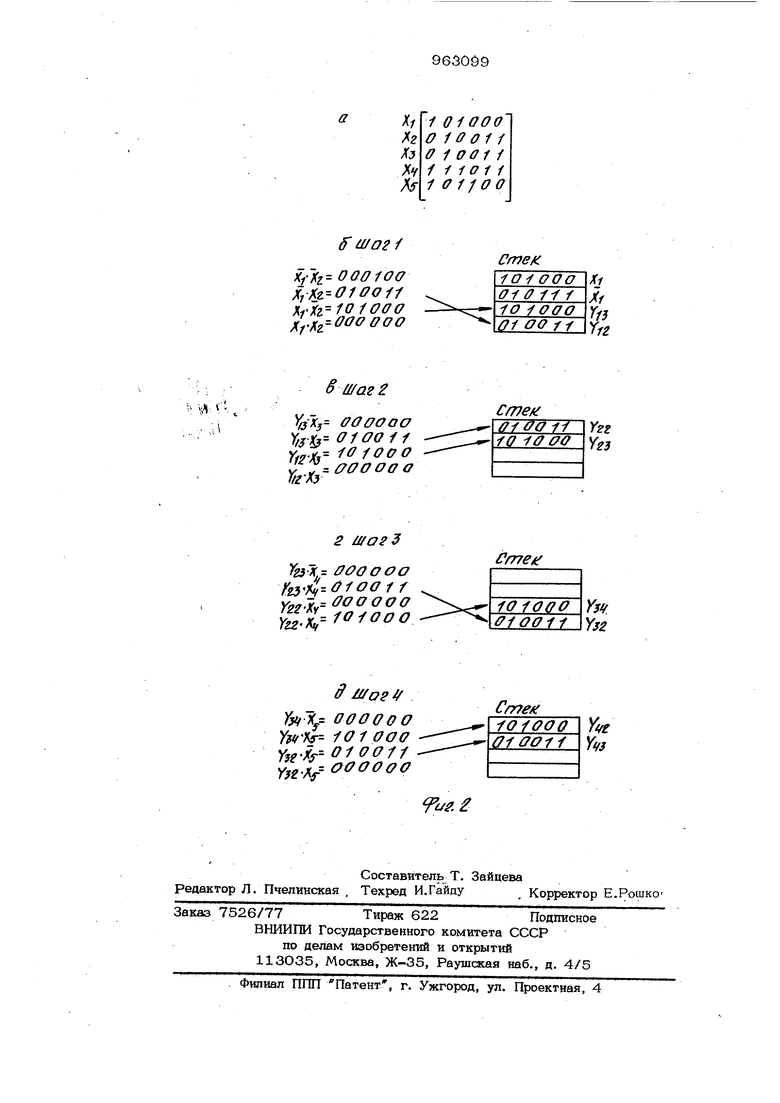

Цель изобретения - повышение быстродействия логического запоминающего устройства. Псх тавленная цель достигается тем, , что Б логическое запоминающее устройство, содержащее матрицу, запоминающих элементов, формирователи сигналов записи формирователи сигналов считывания, уси- лители считывания, регистры слова, дешифратор адреса, грутаты элементов ИЛИ, элемент ИЛИ и группы элементов И, причем выходы первого регистра слова сое динены с первыми входами элементов И первой группы, выходы которых подключены ,к первым и, вторым входам элементов ИЛИ первой группы, выходы которых соединены с входами первых формиро вателей сигналов записи, выходы которых подключены к разрядным иганам записи матрицы, разрядные шины считывания которой соединены с первыми входами усилителей считывания, вторые входы которых объединень и являются входом сброса устройства, а выходы подключены к входам второго регистра слова, выходы элементов ИЛИ второй группы соединены с входами первого регистра слова, выход ош-юго из элементов ИЛИ третьей группы подключен к первым входам одних из эле ментов И второй группы, выходы которых соединены с входами вторых формировате лей сигналов записи, выходы которых под ключены к адресным шинам записи матрицы, первый вход элемента ИЛИ соединен с первым входом другого элемента ИЛИ третьей группы, выход которого подключе к первым входам других элементов И второй группы, выходы которых соединены с входами формирователей сигналов считы- вания,вы5срдь1 которых подключены к адрес.ным шинам считывания матрицы, вторые входы элементов И второй группы соедин&ны с выходами дешифратора адреса, выходы второго регистра слова подключены к первым входам элементов И третьей груп пы, выходы одних из которых соединены с первыми входами элементов ИЛИ второй группы, выходы других элементов И треть ей группы подключены к третьим входам элементов ИЛИ первой группы, а вторые входы - к первому входу одного из эле ментов ИЛИ третьей грутгы, второйи третий входы которого соединены соответственно со вторыми входами одних из элементов И первой группы и выходом элемента ИЛИ и вторыми входами других элементов И первой, группы, вторые входы элементов ИЛИ второй грушш и выходы устшителей считывания явля ются информашюнными входами и выходами устройства, од игами йз ynpadfennroraHx входов которого являются вторые входы одних из элементов И третьей группы и первые и вторые входы элементов ИЛИ третьей группы, входы сброса- регистров слов являются входом сброса, устройства, введены счетчик, адресные регистры, схемы сравнения, четвертая, группа элементов И, четвертая группа элементов ИЛИ и мультиплексор адреса, причем первые входы первого элемента И четвертой группы и первого элемента ИЛИ четвертой группы подключены к первому выходу второго регистра-, слова, а вторые входы - к второму выходу второго регистра слова, первые входы последующих элементов И четвертой грухшы соединены соответственно с выходами предшествующих элементов ИЛИ четвертой грухшы, а вторые входы - с соответствующими выходами второго регистра слова, первые входы последующих элементов ИЛИ четвертой грухшы подключены соответственно к выходам предыдущих элементов И четвертой группы, а вторые входы - к соответствующим выходам второго регистра слова, выходы мультиплексора адреса подключены к входам дешифратора адреса, а входы соединены соответстве но с выходами счетчика и одним из выходов адресных регистров, другие выходы первого адресного регистра подключены к входам первой схемы рравнения, входы второго адресного регистра соединены с входами второй схемы сравнения, адресные входы счетчика являются адресными входами устройства, входы сброса и управляющие входы счетчика и адресных регистров являются другими входами сброса и другими управляющими входами устройства, выходы схем сравнения и выход последнего элемента ИЛИ четвертой группы являются индикаторными выходами устройства. На фиг. 1 приведена функциональная схема предложенного устройства; на фиг, 2 - пример пошагового нахождения совпадающих столбцов массива информации, поясняющий работу устройства. Предлагаемое устройство содержит (фиг. 1) накгаггатель 1 с числовыми линейками 2 на тороидальных сердечниках 3 с прямоугольной петлей гестерезиса, пронизанных разрядными шинами 4 , разрядными швдамн 5 .считывания, адрес иими б записи и адресными шинами 7 считывания, первые формироваятели 8 сигналов записи, первую группу элементов ИЛИ 9, первую группу элементов И 10, первый регистр 11 слова на триггерах 12, вход 13 сброса, вторую группу элементовили 14 с информационными входами 15 устройства, ИЛИ 16, входы 17-21 управления третью группу элементов ИЛИ 22 счетчик 23 с входами сброса 24 и управления 25 и адресными входами 26, первый адресный регистр .27 с входами 28 и 29 управления, предназначенный для хране( ния прямого кода адреса,первую схему ЗО сравнения, второй адресный регистр 31, предназначенный для хранения инверсного кода адреса, с входами 32 и -33 управления и входом 34 сброса, втогг. рую схему 35 сравнения, мультиплексор 36 адреса, дешифратор 37 адреса, вторую группу элементов И 38, вторые ()юрмирователи 39 сигналов записи, формирователи 40 сигналов считывания, усилители 41 счщъ вания с входом 42 стробирования, второй регистр 43 слова на триггерах 44, предназначенный для регенерации информации в устройстве, с входом 45 сброса, одни из элементов И 46 третьей группы, третью группу элементов ИЛИ 47 и другие элементы 48 треть ей группы с управляющими входами 49 и четвертую группу элементов И 50. На фиг. 1 обозначены информационные 51 и ивдикаторные 52 - 54 выходы устройства. На фиг. 2 приведет пример пошагового нахождения совпадающих столбцов массива информации, имеющего шесть столбцов и записанного в первых пяти числовых линейках накопителя 1. Четыре последующие числовые линейки накопителя 1 являются стеком. На фиг. 2 показан пример совпадения первого и третьего столбов массива информации, а также совпадения второго, пятого и шестого столбцов; на фиг. 2а исходный массив информации, на фиг. 2 б д - последовательные шаги поиска совпадающих столбцов. Емкость накопителя 1 равна N + 3/4 п (где п - число разрядов, N - количеств числовых линеек, необходимых для хранения обрабатываа юго массива информации В процессе функционирования устройства N числовых линеек 2 накопителя 1 используются для хранения результатов обработки массива. В дальнейшем эти числовые линейки называются стеком. Устройство работает след5тощим образом. В предлагаемом устройстве вьтолнени элементарных логических операций (дизъюнкции, коиьюшшии, запрета и других) производится так. же, как и в известном. При этом операндами являются: некоторсю Об

числовых линеек стека памяти, получевн ное на предыдущем шаге, логически умножается на прямое и инверсное значение Э ,... Хп ), записанное слово X ( X на регистре 11 и слово (У ,... i i... а n ) I хранящееся в избранной числовой линейке 2 накопителя 1, причем х- - это i -ый разряд слова X , записанный в 1 -ом триггере регистра 11 слова, у - это i -ый разряд слова Y , хранящийся в i -ом сердечнике избранной числовой линейки 2 накопителя 1. На счетчике 23 устанавливается код адреса, соответствующего числовой линейке 2 накощ теля 1, из которой должна быть выбрана информация, относящаяся к исходному массиву и подвергающаяся сравнению, а на регистрах 27 и 31, являющихся пряг мым и инверсным указателями стека, устанавливаются соответственно коды адреса числовых линеек-2 накопителя 1, в которых должны быть выполнены всш могательные операции по поиску совпадающих столбцов массива информации, т.е в регистре 27 устанавливается адрес первой свободной числовой лине|1ки 2, а в регистре 31 - адрес последней числовой линейки 2. Операция нахождения совпадающих столбцов массива выполняется по шагам, причем на каждом шаге рассматривается массив, представляющий собой только часть исходного массива, в которой уже найдены совпадающие столбцы. К этой части массива присоединяется очередная строка и производится проверка равенства в ней значений разрядов, относящихся к этим совпадающим столбцам массива. На первом шаге {4иг. 26) определяют ся совпадающие столбцы в первой и второй строках массива, хранимых соответственно в первой и второй числовых линейках 2 накопителя 1. Для этого выполняются четыре операции логического умно жения содержимого указанных выше чиоловых линеек накопителя 1. После каждой операции логического умножения определяется количество в произведениях, и если количество 1 не менее двух, то происходит запись результата произведений в свободные числовые линейки стека памяти, поскольку количество 1 в каждом из произведений равно количеству совпадающих столбцов, причем 1 стоят в разрядах, соответствующих этим столбцам. На втором шаге (фиг. 2в) определяют ся совпадающие столбцы в первых трех строках массива. Для этрго содержимое содержимого третьей числовой линейки 2 накошггеля 1. Определяется количество 1 в каждом из результатов произведва йий-и если количество 1 не менее двух то происходит запись результатов в стек мяти на места значений, полученных на предыдущем шаге. Процесс повторяется до тех пор, пока содержимое стека памяти, полученное на (N «2)-ом шаге, не будет логически умножено на прямое и инверсное значени содержимого N -ой числовой линейки 2 накопителя 1. Произведения, содержащие не менее двух i, записанных в стеке памяти, указывают совпадакшгае столбцы. Каждой группе совпадающих столбцов, если таковая имеется; соответствует нулевое зкачение числовой линейки 2 нако пителя 1. Первый шаг вышеизлозкенного алгорнтма нахождения совпадающих столбцов информации наполняется за двадцать один двадпать пять тактов. Первый шаг состоит из следующих тактов,, Первь й такт. Считывание слова; записанного по адресу, установлен ному на счетчике 23 на регистр 43. Дх1я этого подается на вход 20 сигнал управле1тя, поступающий через элемент ИЛИ 22 и элемент И 38, второй вход которого связан с возбулоденным выходом даишфратора 37, на запуск формировате ля 40i соответствующего коду, установленному на счетчике 23, Под действием полного адресного тока происходит ключешю, в нулевое состоя troe тех сердечников 3 соответствующей числовой линейки 2 ншсодетеля 1, которые находияис в состоянии i, и на соответствующих разряднь Х шинах 5 наводятся выходные ст-сгналы, которые при подаче сигнала на вход 42 через усилители 41 поступают на вход установки в I. триггеров 44 регистра 43., В результате выполнения первого так та в регистр 43 заносится первое слово массива, записанное в зисповой линейке 2 накошггеля 1. В дальнейшем для удо5« ства описания работы устройства значени j гч слова будем обозначать через . ( ый разряд спова; Х - разрядность слов, у - целое чиспОо Второй та..кт, Пвресшлка со. держимого регистра 43 на .регистр 11. Сигнал подается на вход 49, в резуль тате черва те элементы И 48, входы ко торых связаны с единичными выходами триггеров 44, находящихся в состоянии 1, и через элету енты ИЛИ 14, сигналы поступают на входы установки в единич.ное состояние соответствующих триггеров 12 регистра 11„ Третий такт. Восстановление слова. Сигнал подается на вход 19, поступающий через те элементы И 46, входы которых связаны с выходами триггеров 44, находящихся в состоянии 1, и далее че™ рез соответствующие элементы ИЛИ 9 на запуск формирователей 8, Одновременно через элемент ИЛИ 22 и элемент И 38 происходит запуск формирователя 39, соответствующего первой числовой линейгсе 2 накопителя 1, из которой в целом такте шага было считано слово Х . При этом .те сердечники 3 первой числовой i линейки 2, на которые воздействуют адресные, и разрядные полутоки, пере1шючаются в состояние 1. В результате в первой числовой линейке 2 накопителя 1 восстановлено слово Х Четвертый такт. Очистка регистра 43 и увеличение на еди1-шцу кода, записанного на счетчтпсе 23. Управляющий сигнал подается на вход 45 сброса, пocтJпaющнй на входы установки в О триггеров 44. Одновременно подается ст1гнал нл вход 25, прибавляющий единицу к содернсимому счетчика 23, В результате четырех тактов первого шага на регистре 11 записано первое слово массива, а на счетчике 23 установлен код, соответствующий -следующей числовой линейке 2 накопителя 1, в которой хранится второе слово массива. Пятый такт. Запись слова Х в стек. Сигнал подается на Ьход 17, поступа- ющий через элемент ИЛИ 16 и через те элементы И 1О, .входы которых связаны с прямыми выходами триггеров 12 ре- гистра 11, находящихся в состоянии 1 (на регистре 11 в этот момент записано слово Х. ), к через элементы ИЛИ 9 на запуск соответствующих фopv{иpoвaтeлeй 8, Одновременно статная поступает через элемен ИЛИ 22 -и элемент И 38.,.. вто рой вход которого связан с возбужденным выходом дешифратора 37,-на запуск формирователя 39, соответствующего коду, установленному ва регистре 27. Под дай- ствием адресного и разрядного полутоков происходит переключение в единичное состо5 ние сердечников 3 тех разрядов числовой линейки 2 (принадлежащей стеку памяти), триггеры 12 которых находятся в состоянии 1. Шестой такт. Увеличение на единицу кода, записанного на регистре 2 Сигнал подается на вход 28, приба&ляющкй единицу к содержимому регистра 27. Седьмой такт. Запись слова Х в стек. Сигнал подается на вход 18, поступаю щих через те элементы И 10, входы которых связаны с инверсными выходами триггеров 12, находящихся в состоянии О (на регистре 11 в этот момент за, писано слово Х ) и через элементы ИЛИ 9 на запуск соответствующих формирователей 9. Одновременно сигнал проходит через элемент ИЛИ 22 и элемент И 38, второй вход которого связан с воэ бужденным выходом дешифратора 37, на запуск формирователя 39, соответствующего коду, установленному на регистре 27. Происходит переключение в единичное состояние сердечников 3 тех разрядов числовой линейки 2, триггеры 12 которых находятся в состоянии 1. В о с ь МО и т а к т. Очистка регистра 11. Управляющий сигнал подается на вход 13 сброса, поступающий на входы установки в О триггеров 12 регистра 11. Таким образом, в результате выполнения восьми тактов первого шага, в перо вых двух числовых линейках 2 накопитеЛЯ 1 записываются .слова Х. и X соответственно. Девятый такт. Считывание слова .2Сигнал подается на вход 2О, в резуль тате чего на регистре 43 записывается слово Х7 (аналогично первому такту пер вого шага). Д.есятый такт. Пересылка слова Х- из регистра 43 на регистр 11 Сигнал подается на вход 49, в резулв тате чего из регистра 43 на регистр 11 передается слово Xg (аналогично второму такту). Одиннадцатый такт. Восстановление слова XT. (аналогично третьему такту). Сигнал подается на вход 19, в резуль тате чего во второй числовой линейке 2 накопителя 1 восстанавливается слово К Двенадцатый такт. Очио тка регистра 43 и увеличение на единицу кода, записанного на счетчике 23 (аналогично четвертому такту шаг«). Таким образом, в результате выпол нения двенадцати тактов на регистре 12 записано второе слово массива Х а на счетчике 23 установлен код, соответствующий следующей числовой линейке 2 накопителя 1, в которой хранится третье слово массива. Тринадцатый такт. Выполнение поразрядной логической операции. Сигнал подается на вход 21, в результате чего на шинах 5 считывания тех разрядов числовой линейки 2, код адреса которой установлен на регистре 27, появляются выходные сигналы, которые при подаче сигнала на вход 42 через ил тели 41 поступают на единичные входы соответствующих триггеров 44, а сердечники 3 числовой лийейки 2 накопителя 1 оказываются в состоянии - li В результате выполнения этого такта в регистре 43 записано слово числовой линейке 2 накопителя 1, код адреса которой установлен на регистре 27, записано слово . t 2 Четырнадцатый такт. Анализ слова Y..,. Для этого производится анализ сигнала на выходе 52. Единичный сигнал на вы- , ходе 52 появляется только при наличии в коде слова Y, установленного на региотре 43, более одного единичного разряда. Дальнейшее выполнение первого шага зависит от результата, полученного в такте. В этом случае, если на выходе 52 появляется единичный сигнал, выполняется запись слова V-, в стек, для чего сигнал подается на вход 17, в результате в числовой линейке 2, код адреса которой установлен на регистре 31, записывается слово Y/i , затем очистка регистра уменьшение на единицу кода, записанного на регистре 31, для чего подается управляющий сигнал на вход 45, поступающий на входы установки в . О триггеров 44 регистра 43. Одновр менно подается сигнал на вход 33, вычитающий единицу из содержтмого регистра 41. В результате в последней числовой инейке 2 стека записано слово , а а регистре 31 установлен код, соответ-л: твующий последней свободной числовой инейке 2 стека. Если на выходе 52 нет диничного сигнала, выполняется пятнадатый такт. Пятнадца т ы и такт. Счиывание слова Y-n Сигнал подается на вход 20, в реаупьта- те на рзегистре 43 записывается слово X-JT tpe 43 записывается слово Шест-надцатый такт. Анализ слова V и уменьшение на единипу кода, записанногоВ регистре 27. Для этого производится анализ сигнала на выходе 52. Единичный сигнал на выходе 52 появляется только при наличии в коде слова, установленного на р.е- гистре 43, более одного единичного разр да. Одновременно подается сигнал на вход 29, вычитающий единицу из содержимого регистра 27. В результате на регистре -.. 43 записано слово котором определено количество единиц (более одной ил .или нет), а на регистре 27 установлен код, соответству ощий первой числовой линейке 2 стека. Дальнейшее выполнение первого шага зависит от результата, полученного в данном такте. В том случае, если на выходе 52 появляется единичный сигнал, выполняется запись слова в стек, очистка регист ра 43 и измерение на минус единицу код адреса в регистре 31 (аналогично четырнадцатому такту). . В результате в последней числовой ли нейке 2 стека записано слово .X а на регистре 31 установлен адрес последней числовой линейки 2 стека. Если на выходе 50 .присутствует нуле вой сигнал, то выполняется семнадцатый такт: выполнение поразрядной логической операции . Для этого подается сигнал на вход 21 в результате чего на разрядных шинах 5 тех. разрядов числовой линейки 2 , код адреса которой установлен на регистре 27, появляются выходные сигналы, которые при подаче сигнала на вход 42 через усилители 41 поступают на единичные входы соответствующих триггеров 44 В результате на регистре 43 записано слово Восемнадцатый такт. Анализ слова Х-,з, Единичный сигнал на выходе 52 появляется только при наличии в коде слова более одного единичного разряда. Дальнейшее выполнение первого шага зависит от результата, полученного в дан ном такте. В том случае, если на выходе 52 появляется единичный сигнал, выполняется запись слова Y-t в стек и очистка реги стра 43 (аналогично четырнадцатому такту). В результате в последней свободной числовой линейке 2 записывается слово (фиг. 26), а на регистре 31 устанавливается адрес последней свободной числовой линейки 2 стека. Если на выходе 52 есть нулевой сипнал, то выполняется девятнадцатый такт: считывание слова регистр 43 (аналогично первому такту). Двадцатый такт. Анализ считанного слова Y выполняется аналогично четырнадцатому такту. В результате на регистре 43 записано слово, в котором определено количество единиц. Дальнейшее выполнение первого шага зависит от результата анализа: если на выходе 52 имеется единичный сигнал, то вь1полняются запись слова Y в последнюю свободную линейку 2 стека и очистка регистра 43(аналогично четырнадцати му такту). Если на выходе 52 нулевой сигнал, то выполняется такт двадцать первый: анализ кода, записанного на регистре 31. Для этого производится анализ сигнала на выходе 54 схемы 35 сравнения, где появляется единичный сигнал только в том случае, если код, установленный на регистре 31 в исходном состоянии, остался без изменений (для этого на схему 35 сравнения поступает значение этого кода). Состояние стека накопителя 1, получающ&еся в результате выполнения первого шага при обработке исходного массива изображено на фиг. 26. В том случае, если на выходе 54 по окончании первого шага находится нулевой сигнал, свидетельствующий об отсутствии записи информации в стек, операция поиска совпадающих столбцов массива заканчивается, так как таких столбцов нет. Второй и последующие шазги алгоритма функционирования устройства состоят из следующих десяти тактов (причем на J ом шаге обрабатывается ( j +1)-ое слово исходного массива. Увеличение на единицу кода, записанного на счетчике 23, для чего подается сигнал на вход 25. Считывание слова X (j +1), записанного по адресу, установленниму на счетчике 23, на регистр 43, для чего подается сигнал .на вход 20., пересылка слова X ( j +1) из регистра 43 регистр 11 для чего подается сигнал на вход 49. Восстановление слова X ( j+1) в числовой линейке 2 накопителя 1, для этого подается сигнал на вход 19 управления. Очистка регистра 43 выполняется аналогично описанному выше. В резуль татё выполнения этих четырех тактов на регистре 11 .записано ( j +1 )-ое слово массива. Выполнение поразрядной логической операции ,jmj-Х ( (где TTIJ .. номер шага). Для этого подается сигнал на вход 21,. в результате чего на регистре 43 записано слово 4.) , а в стеке 4j-ir JlJ t) е 2 наполнителя 1, в той числовой линейке код адреса которой установлен на регистре 31 для шага с четным, номером или на регистре 27 для шага с нечетным т мером, записано слово j(mj-n)(fi)mj(j+i Анализ слова Для этого производится анализ сигнала на выходе 52. Единичный сигнал на ходе 52 появляется только при наличии в коде слова У-ггп- , установленного на регистре 43 более одного единичного разряда. Дальнейшее выполнение шага зависит от результата анализа. В том случае, если на выходе 52 появляется единичный сигнал, выполняется запись слова в стёк и очистка регистра 43, Одновременно подается сигнал на вход 28, прибавляющий единицу к содержимому регистра 27 или подается сигнал на вход 33, вычитаюшкй единицу из содержи мого регистра 31 в зависимости от выпо няемого шага. Если на выходе 52 нет единичного сигнала, то выполняется считы ван:ие слова YJ Ш: Для этого подается сигнал на вход 20 : в результате чего на регистр 42 записан слово, код адреса которого установлен на регистре 31 (или на регистре 27). Подсчет количества единиц в слове j (Tij+IJ и увеличение на единицу кода, записанного в регистре 31 (инверсном указателе стека), или уменьшение на ед ницу кода, записанного в прямом указател стека - регистре 27. Для этого производится анализ сигнала на выходе 52, единичный сигнал на котором появляется только при наличии в коде слова, установленного на регистре 43, более одного единичного разряда. Одновременно подается сигнал на вход 32, прибавляющий единицу к содержимому регистра 31, или подается на вход 29, уменьшающий на единицу содержимое регистра 27. Дальнейшее выполнейие шага зависит от результата, полученного в данном такте. Если на выходе 52 появляется единичный сигнал, выполняется запись слова в стек и очистка регистра 43. Одновременно подается сигнал на вход 28, прибавляющий единицу к содержимому регистра 27, или подается сигнал на вход 33, вычитаюпгий единицу из содержимого регистра 31. Если на выходе 5-2 находится нулевой сигнал, то анализ OKOHV чания п -го шага. Для этого анализируется сигнал на выходе 54 (или на выходе 53), который является единичным только в том случае, если код адреса в регистре 31 (или в регистре 27) совпадает с кодом, на единицу большим (или меньшим) адреса, установленного в исходном состоятга. При этом на схему 35 сравнения (или схему ЗО сравнения) поступают соответственно коды адреса верхвей (нижней) границы стека. Если на ылходе 54 (или на выходе 53) находится нулевой сигнал, то выполняется логическая операция умш жения слов как описано выше. Одно ремвн но содержимое регистра 27 увеличивается на единицу (или код в регистре 31 уменьшается на единицу). Если на выходе 54 (или на выходе 53) появляется единичный сигнал, то содериси-ч мое регистра 31 (или регистра 27) воэврашается к исходному значению и выполняется анализ на наличие совпадающих столбцов в массиве. Для этого производится выходного сигнала схемы сравнения ЗО (или анализ выходного сигнала схемы сравниния 35). Единичный сигнал появляется на выходе 53 и 54 только в том случае, если код, установленный на регистре 27 (или на регистре 31) совпадает с кодом, который был установлен на нем в исходном состоянии. Если на выходе 53 (или на выходе 54) появляется нулевой сигнал, свидетельсч вующий об отсутствии записи информации в стеке,операция поиска совпадающих столбцов массива заканчивается так как таких столбцов нет. Если на выходе 53 или 54 есть единичный сигнал, то выполняется аналта оковчашга просмотра массива. . Для этого анализируется признак окончания просмотра всего массива, вырабатываемый в блоке управления уст ройством (не показанном). Признак окончания просмотра всего массива становш ся равным единице в том случае, когда код, установленный на счетчике 23, равен адресу воследнего слова массива. Если прюнак окончания просмотра мао- , 15ёб сива равен нулю, то осуществляется пе реход к первому такту очередного шага. Если признак окончания просмотра массива равен едишше, то операция поиока совпадающих столбцов массива закончена. При этом записанные в стеке сло ва соответствуют группам совпадающих v столбцов, номера которых равны номерам единичных разрядов в кодах записанных в стеке слов), а количество слов в ст&ке равно количеству совпадающих столб Например, д слова, записанных в стеке (фиг. 2д), говорят о наличии в массиве двух совпадающих групп столбцов: первого и третьего столбцов и вто- рого, пятого и шестого столбцов. Поскольку зашюь обрабатываемого массива в накопитель может осуществляться как по строхсам, так и по столбцам. Операция нахогкдетет совпадающта строк массива эквивалентна операшш нахояшенш совпадающих столбцов этого же масстюа. Техншсо-экономическое преимущество предлагаемого устройства заключается в том, что оно обеспечивает по сравнению с известным повышение быстродействия при выполнении операции нахождения сов падающих элементов (столбцов или строк) массива информации, в два раза. Формула изобретения Логическое запоминающее устройство, содержащее матрицу запоминающих элементов, формирователи сигналов записи, формирователи сигналов считывания, усилители считывания, регистры слова, де шифратор адреса, грушы элементов ИЛИ, элемент ИЛИ и группы элементов И, причем выходы первого регистра слова соединены с первыми входами элементов И первой группы, выходы которых подключены к первым и вторым входам элемен тов ИЛИ первой группы, выходы которых соединены с входами первых формирователей сигналов записи, выходы которых подключены к разрядюым шинам записи матрицы, разрядные шкны считывания которой соединены с первь ми входами устшителей «рчитывання, вторые вхо ды которых объединены и являются входом сбооса устройства, а выходы подключены к входамВторого регистра слова, выходы элементов ИЛИ. второй группы соединены с входами первого регис1 ра слова, выход одного нз элементов ИЛ третьей группы подключен к первым вхоёiG. , дам одних из элементов И второй группы, выходы которых соединены с входами вторых формирователей сигналов записи, выходы которых подключены к адресным шинам записи матрицы, первый вход элемента ИЛИ соединен с первым входом другого элемента ИЛИ третьей группы, выход которого подключен к первым входам других элементов И второй группы. выходы которых соединены с входами формирователей сигналов считывания, вьь, ходы которых подключены к адресным шинам считывания матрицы, вторые входы элементов И второй группы соединены с выходами дешифратора адреса, выходы второго регистра слова подключены к первым входам элементов И третьей группы, выходы одних, из которых соединены с первыми входами элементов ИЛИ второй группы, выходы других элементов И. третьей группы, подключены к третьим входам элементов ИЛИ первой группы, а вторые входы - к первому входу одного из элементов ИЛИ третьей группы, второй и третий входы которого соединены соответственно со вторыми входами одних из элементов И первЬй группы и выходом элемента ИЛИ и вторыми входами других элементов И первой группы, вторые входы .элементов ИЛИ второй группы и выходы усилителей считывания являются информационными входами и выходами устройства, одними иэ управляюипк входов которого являются вторые входы одних из элементов И третьей группы и первые и вторые входы элементов ИЛИ третьей группы, входы сброса регкстров слов являются входсж сброса устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит счетчик, адрес ные регистры, схемы сравнения, четвер тую группу элементов И, четвертую группу элементов ИЛИ и мультиплексор адреса, причем первые входы первого элемента И. четвертой группы и первого элемента ИЛИ четвертой группы подключены к первому выходу второго регистра слова, а вторые входы - -ко второму выходу второго регистра слова, первые входы последующих элементов И четвертой группы соединены соответственно с выходами предшествующих элементов ИЛИ четвертой группы, а вторые входы - с соответствующими выходами второго регистра слова, первые входы последующих элементов ИЛИ четвертой группы подключены соответстврнно к выходам предыдущих элементов И четвертой группы, а вторые входы - к

соответствующим выходам второго регистра слова, выходы мультиплексора адреса подключены к входам дешифратора адреса, а входы соединены соответственно с выходами счетчика и одним из выходов адресных регистров, другие выходы первого адресного регистра подключены к входам первой схемы сравнения, другие входы второго адресного регистра соединены с входами второй схемы сравнения, адресные входы счетчика являются адресными входами устройства, входы сброса и управляющие входы счегчика и адрес, ных регистров являются другими входами сброса и другими управляющими входами . устройства, выходы схем сравнения и выход последнего элемента ИЛИ четвертой группы являются индикаторными выходами устройства.

Источники информации, принятые во внимание прт1 экспертизе

№ 253143, кл. Q 11 С 11/02, 1968.

а

KI Лг

/01ООО

о 1 о О1f /Tj Лу

ff i 001 f i i 1 о 1 i

6 шог

;./2- OOO-fOO }(,}(z--0100i-f }(..l(i fOfffffff OOOffOO

в Шаг 2

YffXj ffffoooo ,s-Ky--о 100 ii

J;. iOfOOO y.C7ffOOOO

ГкХз

2 OfO

b ff }oooo

yy,j(L f}iOO 1 f

Y,-,-ffooooo

o ioo о

fzZ

ff

oooooo iOi ooo oi oai

Стек

Авторы

Даты

1982-09-30—Публикация

1981-02-03—Подача