11

Изобретение относится к технике электрической связи и может использоваться в системах передачи дискретной информации и телеграфии по частотно-ограниченным каналам связи.

Цель изобретения - повышение помехоустойчивости путем повьшейия точности адаптации к амплитудно-частотной характеристике канала связи и текущему спектру помех.

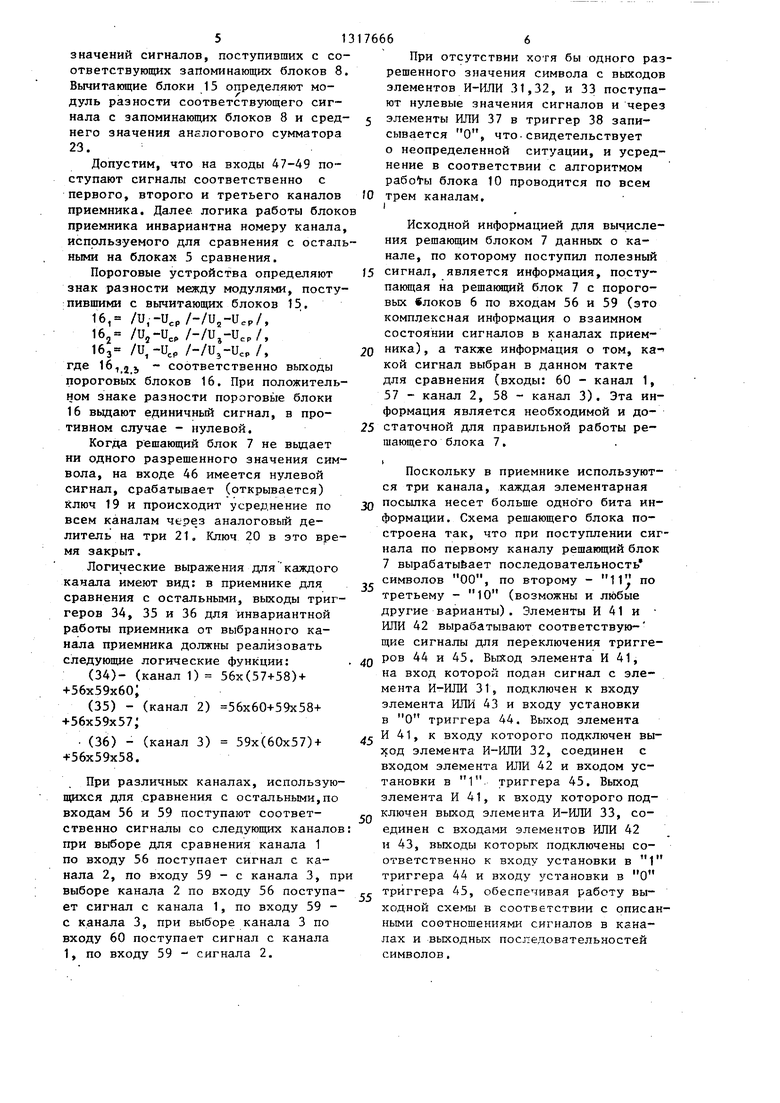

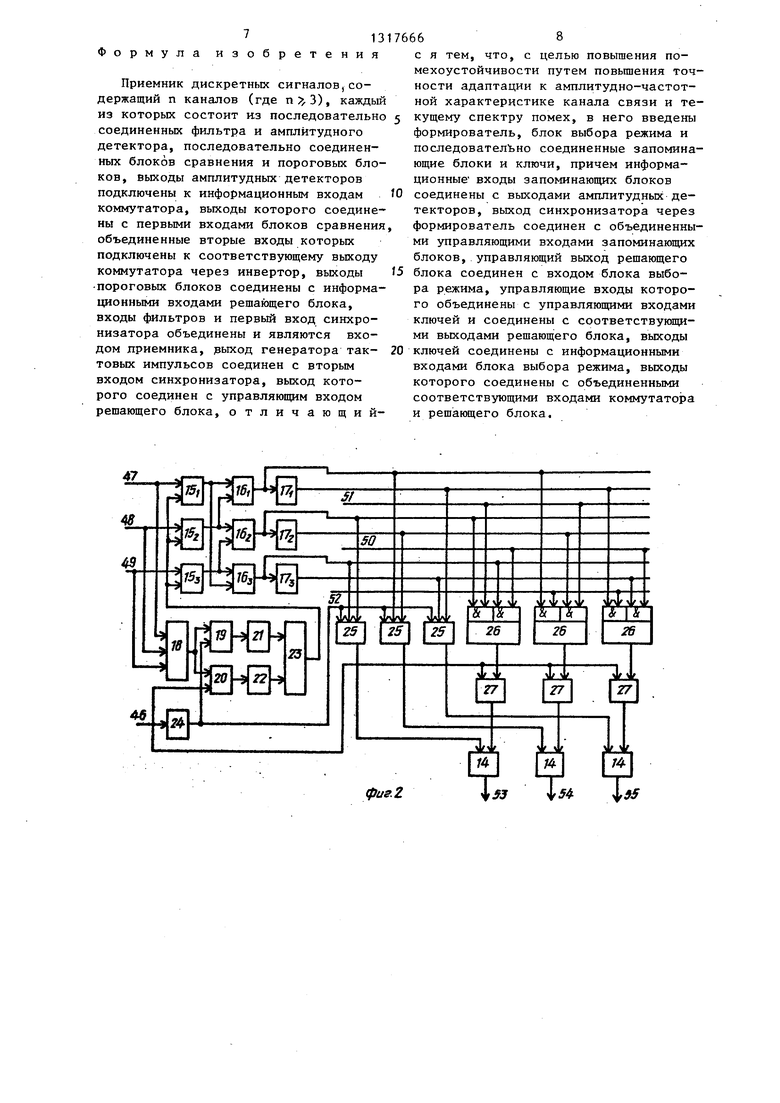

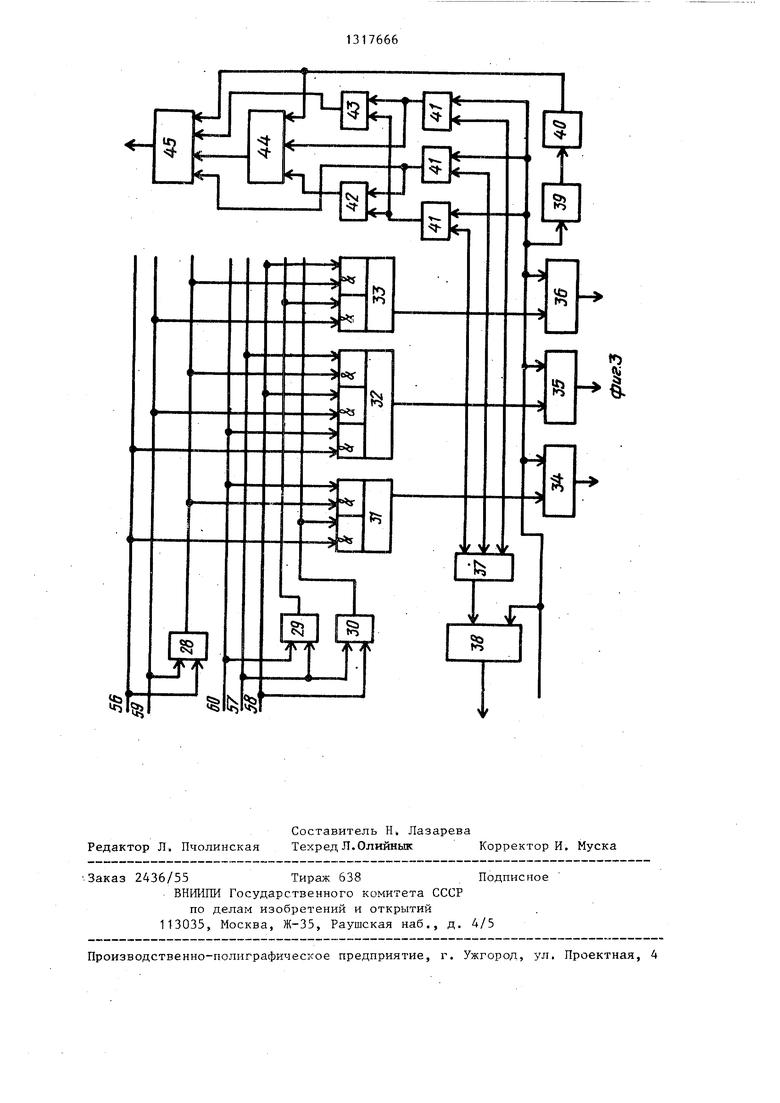

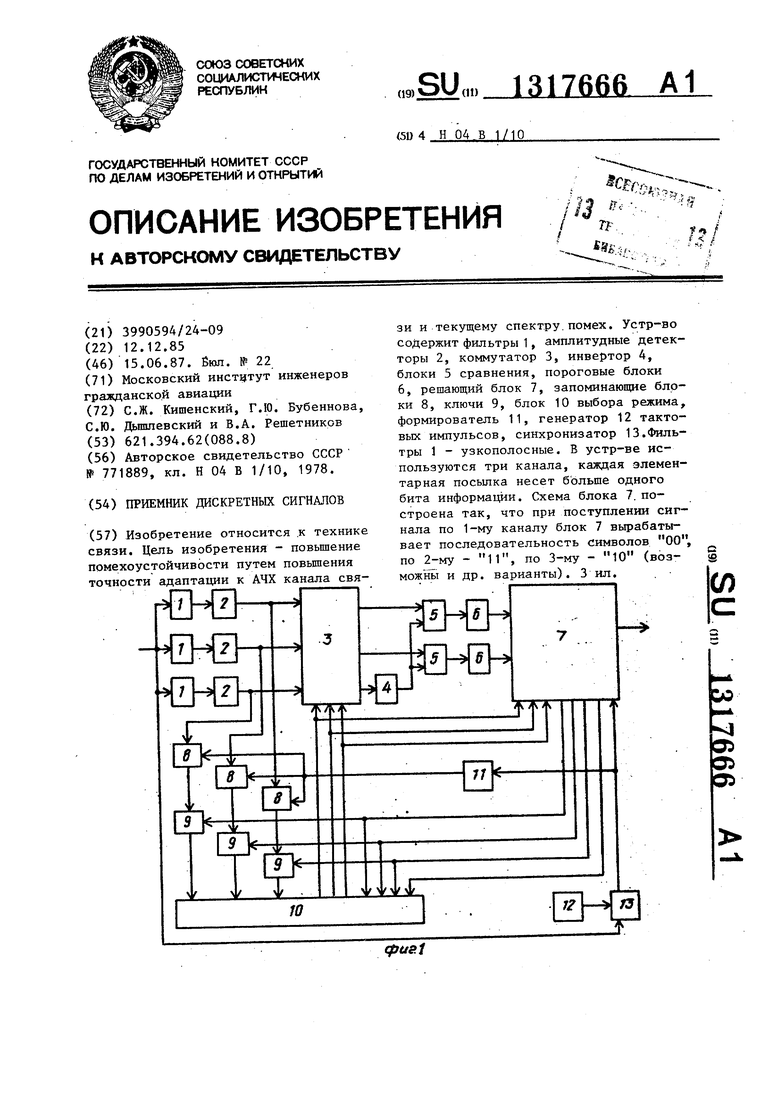

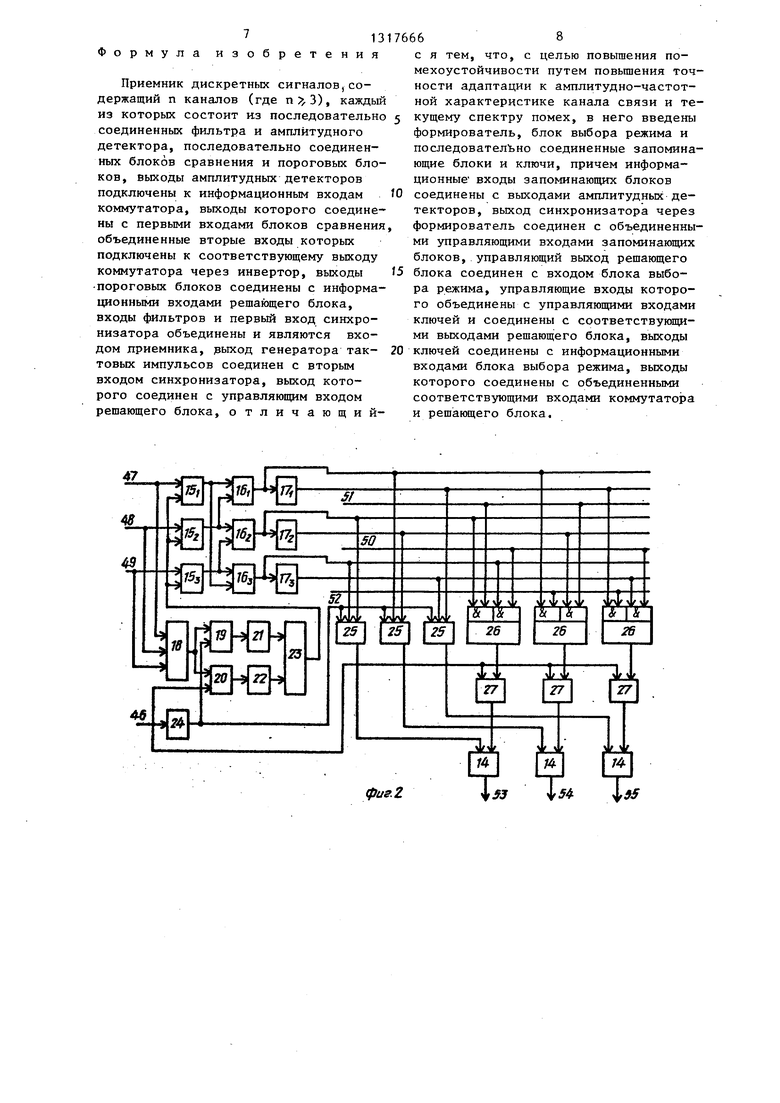

На фиг. 1 изображена структурная электрическая схема предложенного приемника5 на фиг. .2 - структурная схема блока выбора режима; на фиг.З структурная схема решающего блока.

Приемник содержит фильтры 1, амплитудные детекторы 2, коммутатор 3, инвертор 4, блоки 5 сравнения, пороговые блоки 6, рещающий блок 7, запоминающие блоки 8, ключи 9, блок 10 выбора режима, формирователь 11, генератор 12 тактовых импульсов и синхронизатор 13о

Блок 10 состоит из элементов ИЛИ 14, вычитаюпщх блоков 15, пороговых блоков 16, элементов НЕ 17, первого аналогового сумматор.а 18, первых 19 и вторых 20 ключей, аналогового делителя на три 21, аналогового делителя на два 22, аналогового сумматора 23, элемента НЕ 24, элемента И 25, элемента И-ИЛИ 2б и элемента И 27. Решающий блок 7 выполнен на элементе И 28, элементах ИЛИ 29 и 30,; элементах И-ИЛИ 31-33, триггерах 34-36, элементе ИЛИ 37, триггере 38, умножителе частоты на два 39, формироват ле 40, элементе И 41, элементах ИЛИ 42 и 43 и триггеров 44 и 45.

Приемник работает следующим образом.

При отсутствии полезного сигнала или идентичных характеристиках фильтров 1 и амплитудных детекторов 2 воздействие помех не вызывает срабатывания пороговых блоков 6 и на выходе решающего блока 7. не появляется разрешенньк значений символа. При появле.нии полезного сигнала на выходах соответствующих блоков 5 сравнения появляется сигнал рассогласования, которьш вызывает срабатывание соответствующих пороговых блоков 6 и рещающий блок 7 выдает требуемое значение информационного символа. При появлении сигналов в канале, используемом для сравнения с остальными, срабатывают все пороговые блоки 6. При появлении полезного сиг76662

нала в одном .из остальных каналов срабатывает пороговьй блок 6, соответствующий этому каналу. Все остальные сочетания сработавших поро- - говьгх блоков 6 являются для приемника запрещенными. Реально полезный сигнал на входе одного из каналов приемника присутствует всегда. Отсутствие хотя бы одного сигнала в

JO каналах приемника может быть вызвано помехой и вызывает появление в решающем блоке 7 сигнала стирания. Выдача информации решающим блоком 7 на выход производится по сигt5 налам с синхронизатора 13, причем, поскольк у число каналов больше или равно трем, принятие одной посылки вызывает появление на выходе более одного символа. С синхронизатора 13

20 сигналы поступают на формирователь- 11, обеспечивающий запись мгновенного значения уровня сигналов с требуемым значением фазы элементарной посылки ,в запоминающие блоки 8. С при25 ходом очередного импульса от формирователя 11 происходит перезапись в запоминающем блоке 8 мгновенного значения сигнала в канале приемника, запоминающие блоки 8 выполняют функ30 Ции выборки и хранения; перезапись .производится одним импульсом.

Момент перезаписи определяется формирователем 11 и обусловлен двумя

jr факторами: момент времени внутри элементарной посылки выбирается rt3 условий установления входного сигнала, т.е. окончания переходных процессов, при изменении канала приемника, по

40 которому идет сигнал, формирователь 11 может включать делитель, который осуществляет выбор частоты подстрой- ки, т.е. сравнение каналов, выбор среднего значения осуществляется

45 не по каждой посылке, а через определенное число посылок, что обусловлено медленным изменением амплитудно- частотной характеристики канала связи и спектра помех, а также сниже5Q нием числа и длительности переходных процессов при изменении сравниваемог канала.

Определение решаю1 а м блоком 7 зна чёния принятого сигнала позволяет

ГС одновременно определить номер канала приемного, по которому принят полезньм сигнал. Решающий блок 7 вьщает управляющий сигнал на ключи 9 и блок 10 выбора режима. Ключ 9,

соответствующий каналу, по которому принят полезный сигнал, закрывается и не пропускает данное значение сигнала в соответствующем канале приемника на вход блока 10, для вычислени среднего значения. Блок 10 выполняет следующие функции: определяет среднее значение сигнала по всем каналам приемника: определяет номер канала приемника, значение сигнала в кото- ром наиболее близко к среднему значению и вьщает сигналы на коммутатор 3 и решающий блок 7 для ,их переключения таким образом, чтобы для сравнения с остальными использовался тот канал приемника, значение сигнала в котором наиболее близко к среднему. Схемы коммутатора 3 и рещающего ка 7 выполнены таким образом, чтобы обеспечить йнва)иантность выхода при емника от номера канала, выбранного для сравнения с остгШьными. Далее (для следующей посылки) схема работает аналогичным образом. При возникновении ситуации, когда решающий блок 7 не вьщает ни одного разрешенного значения символа, по сигналу, вьщаваемому им непосредственно на блок 10, происходит изменение коэффициента усреднения для правильного разрешения проблемы вычисления среднего, так как в этом случае ни один запрещающий сигнал на ключи 9 не поступает и на блок 10 подаются сигнал со всех запоминающих блоков 8 (в не- .определенной ситуации целесообразно принимать решение по.всем каналам, так как неизвестно, какой следует исключить из анализа), При использовании трех каналов коэффициент усред нения изменяется с 2 по 3. Коммутатор 3 и решающий блок 7 в этом случае позволяет осуществить инвариантность выходного сигнала,

Фильтры 1 являются узкополосными. Выходной сигнал на синхронизатор 13 поступает в момент смены одного значения входного сигнала приемника на iдругой. Момент смены может быть ис- кажен помехами и расхождением частот задающих генераторов передатчика и приемника, однако синхронизатор 13 за счет принципа функционирования и наличия демпфирующего устройства, обеспечивает тактовую (фазовую) подстройку частот принимаемого сигнала и местного генератора тактовых импульсов.

Блок 10 работает следукмцим образом.

Сигналы с ключей 9 поступают на первый аналоговый сумматор 18 и при вьщаче решающим блоком 7 разрешенного изменения символов (на вход 46 поступает единичный сигнал и открывает ключ 20) поступают на аналоговый делитель на два 22 и через аналоговый

Канал I 24x17.,x173-f-35x(33x173x17)

. Канал 2 24x16. х17,,+35х(32х174+ +34x16,);

Канал 3 24x16 х16 +35x(32x164 +33x16),

Сигналы с элементов НЕ 17 являются инверсиями соответствующих сигналов с пороговых блоков 16,

Например, если сигнал:/ с вычитающего блока 15 больше сигнала с вычитающего блока 15 2, и оба они больше сигнала с вычитающего блока 15 у то при наличии разрешенного значения символа с решающего блока 7 (на входе ) и при единичном сигнале на входе 50 (что соответствует решению решающего блока 7 о том, что сигнал передавался по второму каналу решение о передаче сигнала по.первом каналу вызывает появление единичного сигнала на входе 51, а по третьему - на входе 52, в соответствии с выражениями (1) при нулевом значении порога срабатьгеания пороговых блоков 16.на них соответственно появляются сигналы 16., 1, , , а на элемен- ;тах НЕ (для сравнения с остальными будет выбран третий канал, так как только вторая часть выраже-. ния для канала 3 принимает значение 1, При отсутствии разрешенного значения символа (,24 2 1, -32 33 34 0) будет сделан тот же выбор по первой части для канала 3 в выражении (1), В любом из описанных случаев появляется сигнал на выходе 53, что свидетельствует о выборе для сравнения с остальными третьего канала. Аналогично при выборе второго канала появляется сигнал на выходе 54, а при выборе первого - на выходе 55,

Решающий блок 7 работает следующи образом,

В зависимости от того, какой кана используется в сумматор (второй вход его закрыт ключом 9) на вторые входы вычитающих блоков 15, вычитаются из

значений сигналов, поступивших с соответствующих запоминающих блоков 8 Вычитающие блоки 15 определяют модуль разности соответствующего сигнала с запоминающих блоков 8 и сред- него значения аналогового сумматора 23.

Допустим, что на входы 47-49 поступают сигналы соответственно с первого, второго и третьего каналов приемника. Далее логика работы блоко приемника инвариантна номеру канала, используемого для сравнения с остальными на блоках 5 сравнения.

Пороговые устройства определяют знак разности между модулями, поступившими с вычитающих блоков 15.

16, /U,-U,p/-/U,-Uep/,

16 /и,-и,, ,р/,

16з /и,-и,р .р /.

где 16,2,, - соответственно выходы пороговых блоков 16. При положительном знаке разности пороговые блоки 16 вьщают единичный сигнал, в противном случае - нулевой.

Когда решающий блок 7 не вьщает ни одного разрешенного значения символа, на входе 46 имеется нулевой сигнал, срабатывает (открывается) Ключ 19 и происходит усреднение по всем каналам через аналоговый делитель на три 21, Ключ 20 в это время закрыт.

Логические выражения для каждого канала имеют вид: в приемнике для сравнения с остальными, выходы триггеров 34, 35 и 36 для инвариантной работы приемника от выбранного канала приемника должны реализовать следующие логические функции:

(34)- (канал 1) 56х(57+58) + +56х59х60;

(35)- (канал 2) 56x60+59x58+ +56x59x57;

(36)- (канал 3) 59х(60х57)+ +56x59x58.

При различных каналах, использующихся для сравнения с остальными,по входам 56 и 59 поступают соответ- ственно сигналы со следующих каналов при выборе для сравнения канала 1 по входу 56 поступает сигнал с канала 2, по входу 59 - с канала 3, пр выборе канала 2 по входу 56 поступа- ет сигнал с канала 1, по входу 59 - с канала 3, при выборе канала 3 по входу 60 поступает сигнал с канала 1, по входу 59 - сигнала 2.

При отсутствии хотя бы одного разрешенного значения символа с выходов злементов И-ИЛИ 31,32, и 33 поступают нулевые значения сигналов и через элементы ИЛИ 37 в триггер 38 записывается О, что-свидетельствует о неопределенной ситуации, и усреднение в соответствии с алгоритмом работы блока 10 проводится по всем

трем каналам.

I

Исходной информацией для вычисления решающим блоком 7 данных о канале, по которому поступил полезный сигнал, является информация, поступающая на решаннций блок 7 с пороговых влоков 6 по входам 56 и 59 (это комплексная информация о взаимном состоянии сигналов в каналах приемника.) , а также информация о том, какой сигнал выбран в данном такте для сравнения (входы: 60 - канал 1, 57 - канал 2, 58 - канал 3). Эта информация является необходимой и достаточной для правильной работы решающего блока 7.

Поскольку в приемнике используются три канала, каждая элементарная посылка несет больше одного бита информации. Схема решающего блока построена так, что при поступлении сигнала по первому каналу решающий блок 7 вырабатывает последовательность символов 00, по второму - 1iy по третьему - 10 (возможны и любые другие варианты). Элементы И 41 и ИЛИ 42 вырабатывают соответствую- щие сигналы для переключения триггеров 44 и 45. Выход элемента И 41, на вход которой подан сигнал с элемента И-ИЛИ 31, подключен к входу элемента ИЛИ 43 и входу установки в О триггера 44. Выход элемента И 41, к входу которого подключен выход элемента И-ИЛИ 32, соединен с входом элемента ИЛИ 42 и входом установки в 1. триггера 45. Выход элемента И 41, к входу которого подключен выход элемента И-ИЛИ 33, соединен с входами элементов ИЛИ 42 и 43, выходы которых подключены со- оч -ветственно к входу установки в 1 триггера 44 и входу установки в О триггера 45, обеспечивая работу выходной в соответствии с описанными соотношениями сигналов в каналах и выходных последовательностей символов.

Формула изобретения

Приемник дискретных сигналов,содержащий п каналов (где п;5.3), каждый из которых состоит из последовательно соединенных фильтра и амплитудного детектора, последовательно соединенных блоков сравнения и пороговых блоков, выходы амплитудных детекторов подключены к информационным входам коммутатора, выходы которого соединены с первыми входами блоков сравнения объединенные вторые входы которых подключены к соответствующему выходу коммутатора через инвертор, выходы -пороговых блоков соединены с информационными входами решающего блока, входы фильтров и первый вход синхронизатора объединены и являются входом приемника, рыход генератора так- товых импульсов соединен с вторым входом синхронизатора, выход которого соединен с управляющим входом решающего блока, отличающийс я тем, что, с целью повышения помехоустойчивости путем повьш1ения точности адаптации к амплитудно-частотной характеристике канала связи и текущему спектру помех, в него введены формирователь, блок выбора режима и последовательно соединенные запоминающие блоки и ключи, причем информационные входы запоминающих блоков соединены с выходами амплитудных детекторов, выход синхронизатора через формирователь соединен с объединенными управляющими входами запоминающих блоков, управляющий выход решающего блока соединен с входом блока выбора режима, управляющие входы которого объединены с управляющими входами ключей и соединены с соответствующими вькодами решающего блока, выходы ключей соединены с информационными входами блока выбора режима, выходы которого соединены с объединенными соответствующими входами коммутатора и решающего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный коммутатор телеизмерительной системы | 1990 |

|

SU1785020A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Передающее многоканальное телеметрическое устройство | 1977 |

|

SU690523A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| Способ передачи дискретных сообщений с расширенной системой синхронизируемого шифрования и устройство для его осуществления | 2024 |

|

RU2832047C1 |

| Устройство адаптивной дельта-модуляции | 1979 |

|

SU773929A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Способ передачи дискретных сообщений с синхронизируемой системой двойного шифрования и устройство для его осуществления | 2024 |

|

RU2831996C1 |

| Способ передачи дискретных сообщений с синхронизируемой системой двухоперационного шифрования и устройство для его осуществления | 2024 |

|

RU2834001C1 |

Изобретение относится .к технике связи. Цель изобретения - повышение помехоустойчивости путем повьшения точности адаптации к АЧХ канала связи и текущему спектру.помех. Устр-во содержит фильтры 1, амплитудные детекторы 2, коммутатор 3, инвертор 4, блоки 5 сравнения, пороговые блоки 6, решающий блок 7, запоминающие блоки 8, ключи 9, блок 10 выбора режима, формирователь 11, генератор 12 тактовых импульсов, синхронизатор 13.Фильтры 1 - узкополосные. В устр-ве используются три канала, каждая элементарная посылка несет больше одного бита информации. Схема блока 7. построена так, что при поступлении сигнала по 1-му каналу блок 7 вырабатывает последовательность символов 00, по 2j-My - 11, по 3-му - 10 (возможны и др. варианты). 3 ил. с сл cfrtfSi

фие.2

3 Н Н

53 5 95

1 I

| Приемник дискретных сигналов | 1978 |

|

SU771889A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-15—Публикация

1985-12-12—Подача