1

Изобретение относится к преобразованию аналоговых сигналов в цифро- . вые сигналы адаптивной дельта-модуляции л может быть использовано приj передаче видеосигналов изображения и речи по цифровым каналам связи.

Известен адаптивный дельта-модулятор, содержащий элемент вычитания, квантователь, выход которого через JQ блок адаптации и непосредственно подключен к умнох ителю, соеди ненному через интегратор с элементом вычитания, и блок установления включенный между элементом вычитания и квантователем l.

Недостатком известного адаптивного дельта-модулятора является низкая точность аппроксимации фронтов передаваемого сигнала из-за того, что аппроксимирующий сигнал может значительно отличаться от исходного сигнала на участках его резкого изменения.

Известно также устройство адаптив-25 ной дельта-модуляции, содержащее блок вычитания, первый вход которого подключен к шине аналогового сигнала, второй - к выходу интегратора, а выход - ко входу решающего блока,

формирователь размера шага, соединенный первым входом с выходом решающего блока, а первым выходом - с первым входом интегратора, и синхронизатор, подключенный к первому входу решаквдего блока и второму входу формирователя размера шага 2 .

Недостаток этого устройства адаптивной дельта-модуляции также заключается в низкой точности аппроксимации фронтов передаваемого сигнала в результате того, что аппроксимирующий сигнал (копия) может значительно отличаться от исходного сигнала на участках его резкого изменения,т.е. при передаче фронтов. Расхождение аналогового сигнала с его копией вызывает искажения, в результате чего на границах (контурах) принимаемого изображения могут иметь место разрывы.

Целью изобретения является повышение точности аппроксимации фронтов передаваемого сигнала.

Поставленная цель достигается тем, что в устройство адаптивной дельта-модуляции, содержащее блок вычитания, первый вход которого подключен к шине аналогового сигнала.

а второй к выходу интегратора, формирователь размера шага, соединенный первым входом с выходом решакщего блока, а первым выходом - с первым входом интегратора, и синхронизатор, подключенный к первому входу решшоцего блока и второму входу формирователя размера шага, введены 1второй блоквычитания, второй интегратор, коммутатор и элемент сравнения, причем первый.вход второго блока вычитания подключен к шине анало,гового сигнала, а второй - к выходу второго интегратора, первый вход которого соединен со вторым выходом формирователя размера шага, выходы блоков вычитания соединены со входами элемента сравнения, выход которого соединен со вторым входом решающего блока, соединенного выходом с первым входом коммутатора, выходы интеграторов подключены ко второму и третьему входам коммутатора, а их вторые входы подключены к первому и втором. выходам коммутатора.

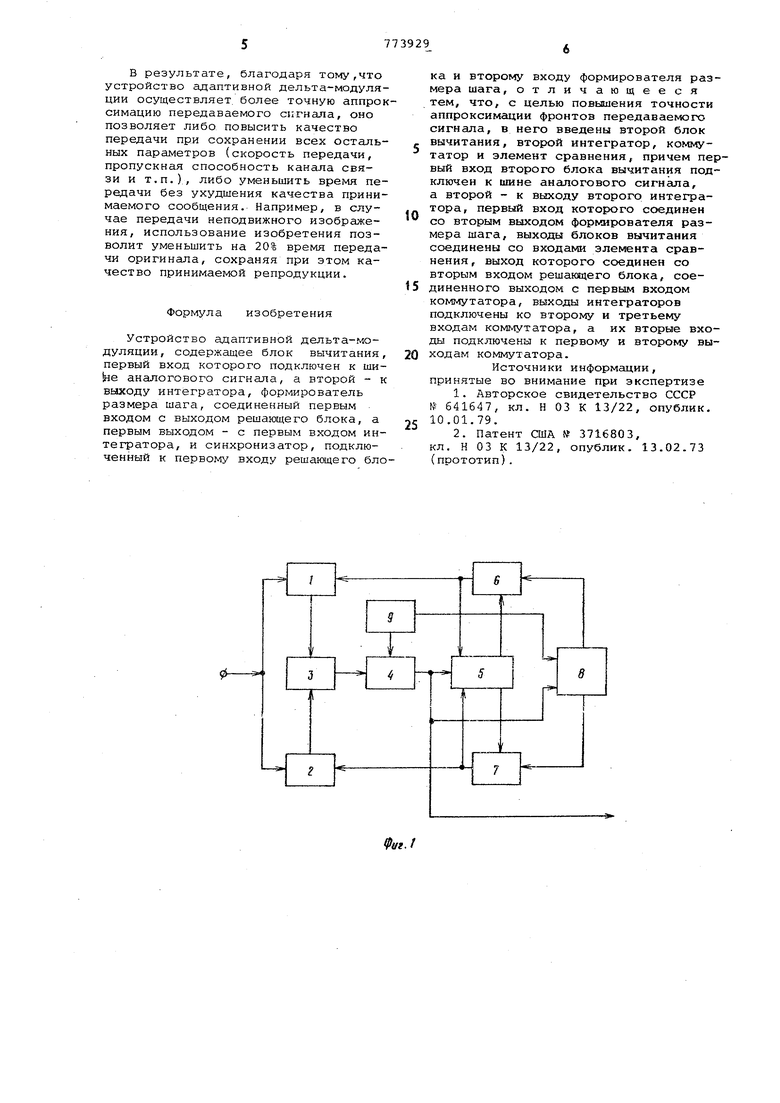

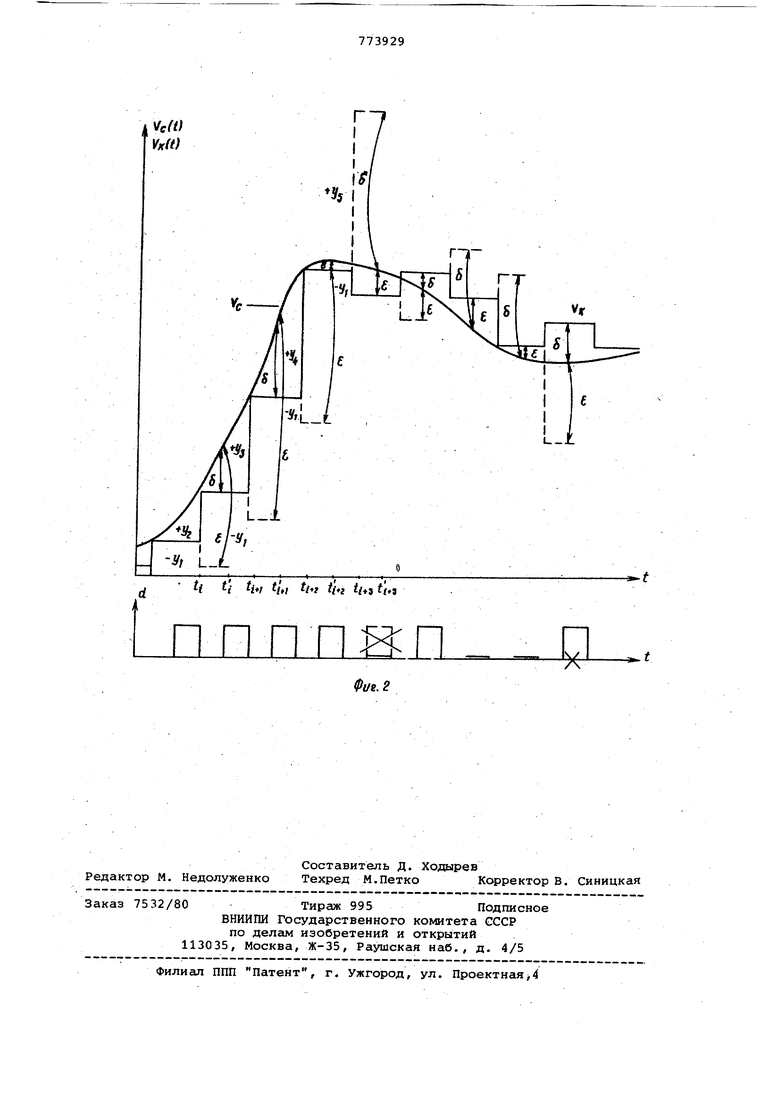

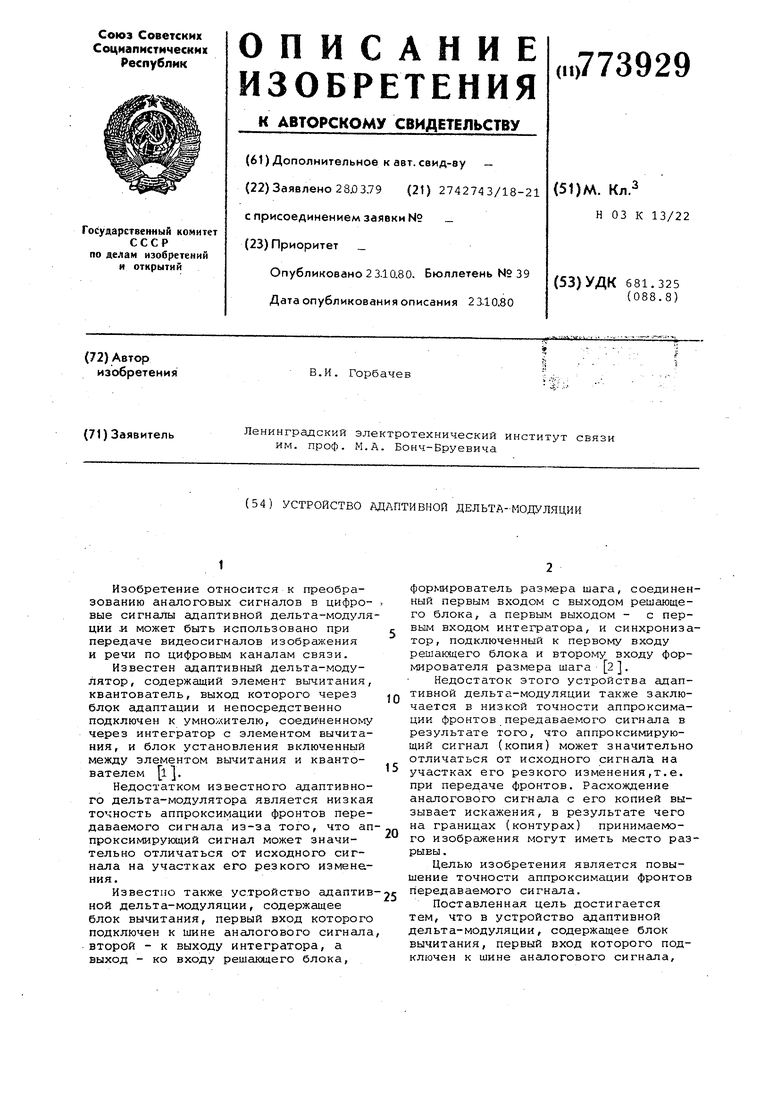

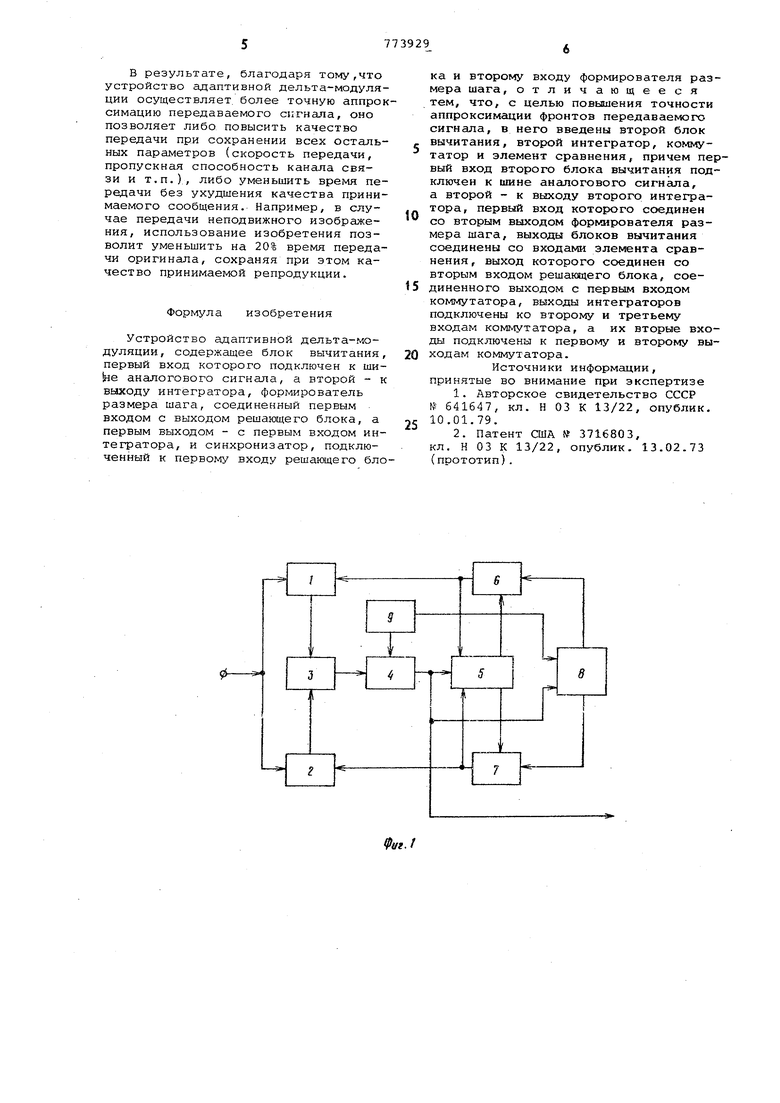

На фиг.1 представлена структурная схема устройства адаптивной дельтамодуляции; на фиг. 2 - временные диаграммы его работы.

Устройство адаптивной дельта-модуляции содержит блок вычитания 1 и 2, первые входы которых подключены к шине аналого-вого сигнала, выходы ко входам элемента 3 сравнения,, выход которого подключен ко второму входу решающего блока 4, соединенного своим выходом с первым входом коммутатора 5, подключенного первым и вторым выходом ко вторым входам интеграторов б и 7, к первым входам которых подключе1 ы выходы формирователя 8 размера шага, первый вход КОТОРОГО соединен с nepBFJM входом коь-т-гутавтора, синхронизатор 9, выходы которого соединены с первым входом решагадего блока и вторым входом формирователя размера Lua.ra, а выходы интеграторов соединены со вторыми входами вычитающих блоков и со вторым и третьим входами коммутатора.

Устройство адаптивной дeльтa- юдyляции работает следующим образом.

Преобразование аналогового сигнала в сигналы дельта-модуляции осуществляется следующим образом.

По сигналу синхронизатора 9 формирователь 8 размера шага выдает по . заданному алгоритму адаптивной дельта-модуляции положительные и отрицательные приращения (шаги) одновременно на интеграторы 6 и 7 соответственно. Копии, сформированные на интеграторах 6 и 7, вычитаются из входного анапогового сигнала на блоках 1 и 2 вычитания соответственно и определи-готся ошибки аппроксимацр И .Элемент 3 сравнения сравнивает ошибки .аппроксимации по абсолютной величине, а решающий блок 4 по результату сравнения

выбирает из двух сравниваемых копий ту, ошибка аппроксимации которой меньше. В зависимости от выбора в канал идет соответствующая кодовая посылка, ког.1мутатор 5 стирает неприемлемое значение копии в одном интеграторе и записывает в него оптимальное значение копии, сформированное в другом интеграторе.

В 14омент времени t формирователь размера ujara вьздает на интеграторы 6 и 7 положительный шаг (+У2.) и и отрицательный (-у ) соответственно (фиг.2). На интеграторе 6 формируется копия V с положительным приращением, а на интеграторе 7 форWpyeTCH копия Укг отрицательным приращением. В блоке 1 вычитания первая копия вычитается из аналогового сигнала и находится ошибка аппроксимации (S

-

V,

в блоке 2 вычитания вычитается вторая копия и находится ошибка аппроксимации

V

I.. К2.

В элементе 3 сравнения по абсолюной величине сравниваются модули О11:кбок аппроксимации / d / и j , / по критерию минимальных ошибок аппроксимации. Если /сГ/ то решаквдий блок в NOM.eHT времени t - выдает единицу в канал, на комг т;/татор 5 и на сброс формирователя 8 размера шаг. По единичному сигналу коммутатор 5 стирает в интеграторе 7 неприемлемое значение копии Vi и загпсывает в него оптимальное значение копии Уц от интегратора 6, а формирователь размера шага сбрасывает код, соответствующий ранее преложенному шагу (-у), как неприемлем-:й. В момент времени t: происходят анализ сформированных копий по величине - аименьшей оашбки .Аналогично изложенному выбирается оптимальное значение копии, которое устаканливается в обоих интегратора в канал идет соответствующая кодовая посылка. Проработка заднего фронта аналогового сигнала происходит аналогично.

Таким образом, в каждом интервале дискретизации происходит анализ и Быбор оптимального значения копии аналогового сигнала.

. Поскольку устройство адаптивной дельта-модуляции исправляет ошибки аппроксимации, то при построении алгоритма изменения шага адаптивной дельта-модуляции можно расширит диапазон амплитудных приращений (шагов), т.е. прорабатывать резкий перепад (фронт) аналогового сигНс1ла за меньшее количество тактовых точек.

В результате, благодаря тому,что устройство адаптивной дельта-модуляции осуществляет, более точную аппроксимацию передаваемого сигнала, оно позволяет либо повысить качество передачи при сохранении всех остальных параметров (скорость передачи, пропускная способность кангша связи и т.п.), либо уменьшить время передачи без ухудшения качества принимаемого сообщения. Например, в случае передачи неподвижного изображения, использование изобретения позволит уменьшить на 20% время передачи оригинаша, сохраняя при этом качество принимаемой репродукции.

Формула изобретения

Устройство адаптивной дельта-модуляции, содержащее блок вычитания, первый вход которого подключен к аналогового сигнала, а второй - к выходу интегратора, формирователь размера шага, соединенный первым входом с выходом решающего блока, а первым выходом - с первым входом интегратора, и синхронизатор, подключенный к первому входу решающего блока и второму входу формирователя размера шага, отличающееся тем, что, с целью повышения точности аппроксимации фронтов передаваемого сигнала, в него введены второй блок вычитания, второй интегратор, коммутатор и элемент сравнения, причем первый вход второго блока вычитания подключен к огане аналогового сигнала, а второй - к выходу второго интегратора, первый вход которого соединен со вторым выходом формирователя размера шага, выходы блоков вычитания соединены со входами элемента сравнения , выход которого соединен со вторым входом решающего блока, соединенного выходом с первым входом коммутатора, выходы интеграторов подключены ко второму и третьему входам коммутатора, а их вторые входы подключены к первому и второму выходам коммутатора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 641647, кл. Н 03 К 13/22, опублик. 10.01.79.

2.Патент США № 3716803,

кл. Н 03 К 13/22, опублик. 13.02.73 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи сообщений с адаптивной дельта-модуляцией | 1981 |

|

SU1025011A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ С АДАПТИВНОЙ ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1972 |

|

SU349080A1 |

| Устройство для передачи и приема сообщений | 1977 |

|

SU641488A1 |

| Устройство связи с дельта-модуляцией | 1983 |

|

SU1095395A1 |

| Адаптивная система связи с дельта-модуляцией | 1989 |

|

SU1764164A2 |

| Многоканальное устройство с адаптивной дельта-модуляцией и временным разделением каналов | 1986 |

|

SU1453606A1 |

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

| ВЫСОКОИНФОРМАТИВНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ИСПОЛЬЗОВАНИЕМ ДЕЛЬТА-МОДУЛЯЦИИ ДЛЯ СЕЙСМИЧЕСКИХ ИССЛЕДОВАНИЙ | 1997 |

|

RU2128880C1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Дискретный адаптивный дельта-модулятор | 1976 |

|

SU641647A1 |

Авторы

Даты

1980-10-23—Публикация

1979-03-28—Подача