13

15, 44, два элемента НЕ 17, 46, три счетчика 33, 40, 62, регистр 20, реверсивный счетчик 42, делитель частоты 52 и блок 65 передачи данных. Блок 65, приняв из тракта передачи данных комбинацию испытательного текста, формирует сигнал, по которому с датчика 2 на сумматор 8 поступает первая кодовая комбинация (КК). На другой вход сумматора 8 поступает аналогичная комбинация из блока 65. Если в результате сравнения комбинаций в сумматоре 8 ошибки не будут обнаружены, то. будет осуществляться сравнение следующей комбинации. Если сумматор 8 выделит сигнал ошибки.

Изобретение относится к технике передачи данных и может использоваться для обнаружения ошибок на выходе тракта передачи данных.

Цель изобретения - повышение достоверности при одновременном повышении быстродействия.

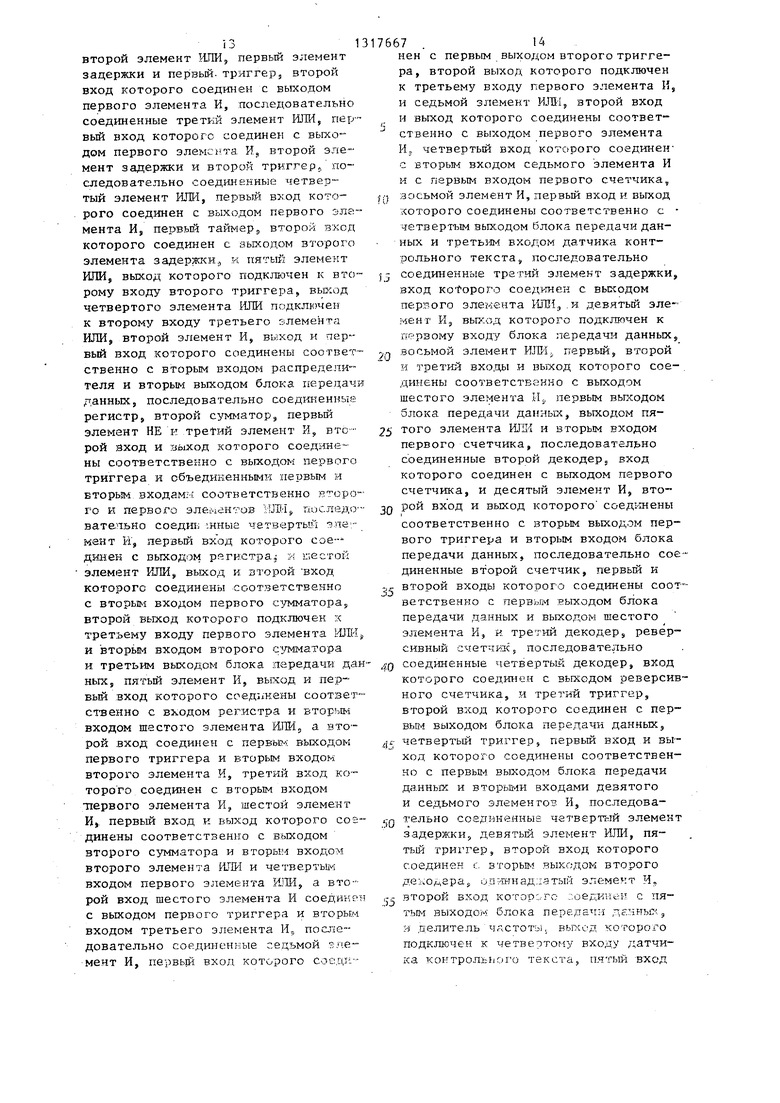

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство для контроля тракта передачи данных содержит первый декодер 1, датчик 2 контрольного текста (ДКТ), распределитель 3, первый элемент ИЛИ 4, первый э гтемент И 5, второй элемент ИЛИ 6, второй элемент И 7, первьй сумматор 8, первый элемент 9 задержки, третий 10 и четвертый 11 элементы ИЛИ, первьш триггер 12, третий элемент И 13, второй элемент 14 задержки, первый таймер 15, четвертый элемент И 16, первый элемент НЕ 17, пятый элемент ИЛИ 18, пятьш элемент И 19, регистр 20, второй сумматор 21, второй триггер 22, шестой 23, седьмой 24 и восьмой 25 элементы И, шестой элемент ИЛИ 26, третий элемент 27 задержки, девятьй элемент И 28, седьмой элемент ИЛИ 29 третий 30 и четвертый 31 триггеры, восьмой элемент ИЛИ 32, первьй счетчик 33, второй декодер 34, десятый элемент И 3S, девятый элемент ИЛИ-36, одиннадцатьй 37 и двенадца- тьш 38 элементы И, третий декодер

667

то происходит проверка исправности стыка между блоком 65 и устройством контроля. При этом из блока 65 повторно выводится комбинация, при которой была обнаружена ошибка. Повторная комбинация поступает только на сумматор 21, где происходит сравнение ее с записанной ранее в регистре 20 комбинацией. Ошибки, выявленные сумматором 21, фиксируются счетчиком 40. Таймер 15 совместно с триггером 22 обнаруживает подряд идущие сигналы ошибок, число которьпс подсчитывает счетчик 33. По результатам анализа ошибок уточняется число зафиксированных не обнаруженных в блоке 65 ошибок. 1 ил.

0

5

0

5

0

5

39, второй счетчик 40, десятый элемент ИШ 41, реверсивньш счетчик 42, четвертый декодер 43, второй таймер 44, пятый триггер 45, второй элемент НЕ 46, тринадвдатый элемент И 47, шестой триггер 48, четырнадцатый 49 и пятнадцатый 50 элементы И, одиннадцатый элемент ИЛИ 51, делитель 52 частоты, двенадцатый элемент ИЛИ 53, четвертый элемент 54 задержки, седьмой триггер 55, пятьй элемент 56 задержки, шестнадцатый элемент И 57, восьмой триггер 58, сем- надцатьй элемент И 59, тринадцатый 60 и- четырнадцатьй 61 элементы ИЛИ, третий счетчик 62, пятьй декодер 63, шестой элемент 64 задержки и блок 65 передачи данных.

Устройство работает следующим образом.

Исходное состояние устройства, осуществляемое под влиянием внешнего сигнала Установка исходного состояния (УМС), предусматривает ус- , тановку (через элемент ИЛИ 6 и элемент 9 задержки) триггера 12 в единичное состояние (единичньй потенциал на единичном выходе), триггера 22 (через элемент ИЛИ 18) - в нулевое состояние (нулевой потенциал., на единичном выходе), триггера 45 - в нулевое состояние (через элемент ИЛИ 36), триггера 55 - в нулевое состояние (через элемент ИЛИ 51),

триггера 58 - в нулевое состояние (через элемент ИЛИ 60),

Блок 65, приняв из тракта передачи данных (ПД) комбинацию испытательного текста формирует сигнал Наличие информации, под влиянием которого производятся исходные установки ДКТ 2, распределителя 3, триггеров 30, 31 и 48, счетчика 33 (через элемент ИЛИ 32), счетчика 40, реверсивного счетчика 42 (через элемент ИЛИ 41) и счетчика 62. Через элемент ИЛИ 4, элемент 27 задержки и элемент И 28 образуется сигнал Готовность, поступающий в блок 65. По сигналу Готовность блок 65 формирует на одном из своих выходов сигнал Пуск ДКТ, который через открытый элемент И 25 поступает на ДКТ 2, С вькода ДКТ 2 на первое плечо сумматора 8 поступает первая кодовая комбинация. На другое его плечо поступает аналогичная комбинация из блока 65 (через элемент ИЛИ 26). Есся триггер 22, а через элемент ИЛИ 11

осуществляется сброс (установка исходного состояния) таймера 15,

Сигнал ошибки с выхода элемента И 5 через элемент ИЛИ 29 увеличивает на единицу содержимое счетчика 33 и реверсивного счетчика 42.

Состояние первого счетчика 33 после , поступления первого входного га-:-- пульса отмечает декодер 34, на первом выходе которого возникает-сл-гтиал

fO

f5

20

Повторение. Блок 65 с получением этого сигнала (через элемент И 33) обеспечивает повторный вывод кокбина- ции, при проверке которой была обнаружена ошибка.

Повторно вьшедшая комбинация поступает только на второе плечо второго с;ьтчматора 21. В регистре 20 остается ранее записанная комб шация, так как элемент И 19, через которьй вход регистра 20 соединен с виходом блока 65, после выхода сигнала ошибки запирается нулевым потенциалом с

ли в результате сравнения комбинаций 25 единичного выхода триггера 12. После ошибки не обнаружены, то из первого сумматора В выходит сигнал Продолжение цикла, который, воздействуя через элемент ИЛИ 4, элемент 27 задержки и элемент И 28,формирует зо

35

40

очередной сигнал Готовность, по которому осуществляется сравнение следующей комбинации.

Каждая новая комбинация, выходящая из блока 65, через элемент И 19 записьшается в регистр 20, выход которого соединен с первым плечом сумматора 21, на другое плечо которого поступает та же комбинация непосредственно с выхода блока 65. До обнаружения ошибок выходной сигнал сумматора 21 не используется.

Если в очередном цикле контроля первьш сумматор 8 обнаруживает несравнение, на его выходе возникает сигнал ошибки, который поступает на входы элементов И 5 и 24. Сигнал i ошибки с выхода элемента И 5 устанавливает триггер 12 в нулевое состояние, характеризующееся нулевым по- Q тенциалом на единичном выходе и роответственно единичным потенциалом на нулевом выходе. В результате запираются для прохождения сигналов элементы И 19 и 7 и открьтаются элементы И 13 и 23. Кроме того, сигналом ошибки с выхода элемента И 5 через элемент ИЛИ 10 и элемент 14 задержки в единичное состояние устанавливает45

55

повторного поступления комбинации сумматор 21 осуществляет сравнение последней с комбинацией, записанной в регистре 20. Обнаруженное несравнение комбинаций отмечается сигналом ошибки на выходе c S MMaTopa 21. Под влиянием последнего на выходе элемента И 23 возникает сигнал, указывающий на сбой в стыке между блоком 65 и устройством контроля (не показано). Этот сигнал через элемент ИЛИ 32 устанавливает в нулевое состояние счетчик 33, записывается в счетчик 40 и через элемент ИЛИ 61 осуществляет вычитание единицы в реверсивном счетчике 42. В процессе проверки всего контрольного текста могут иметь место повторные сбои стыка ,фик- сируемые счетчиком 40.

Когда в процессе контроля счетч1Ж 40 отсчитывает S сигналов, на выходе декодера 39 возникает сигнал Стык неустойчив.

Сигналом с выхода элемента И 23 через второй элемент ИЛИ 6 триггер 12 возвращается в исходное состояние. Триггер 12 функционирует в тот отрезок контрольного цикла, когда происходит индентификация ошибок стыка.

Таким образом, если при повторном выводе из блока 65 кодовой комбина- .

ции сумматор 21 обнаруж1шает ошибку, она относится к сбою стыка между блоком 65 и устройством контроля и фик176674

ся триггер 22, а через элемент ИЛИ 11

осуществляется сброс (установка исходного состояния) таймера 15,

Сигнал ошибки с выхода элемента И 5 через элемент ИЛИ 29 увеличивает на единицу содержимое счетчика 33 и реверсивного счетчика 42.

Состояние первого счетчика 33 после , поступления первого входного га-:-- пульса отмечает декодер 34, на первом выходе которого возникает-сл-гтиал

fO

5

0

Повторение. Блок 65 с получением этого сигнала (через элемент И 33) обеспечивает повторный вывод кокбина- ции, при проверке которой была обнаружена ошибка.

Повторно вьшедшая комбинация поступает только на второе плечо второго с;ьтчматора 21. В регистре 20 остается ранее записанная комб шация, так как элемент И 19, через которьй вход регистра 20 соединен с виходом блока 65, после выхода сигнала ошибки запирается нулевым потенциалом с

5 единичного выхода триггера 12. После о

5

0

Q

5

5

повторного поступления комбинации сумматор 21 осуществляет сравнение последней с комбинацией, записанной в регистре 20. Обнаруженное несравнение комбинаций отмечается сигналом ошибки на выходе c S MMaTopa 21. Под влиянием последнего на выходе элемента И 23 возникает сигнал, указывающий на сбой в стыке между блоком 65 и устройством контроля (не показано). Этот сигнал через элемент ИЛИ 32 устанавливает в нулевое состояние счетчик 33, записывается в счетчик 40 и через элемент ИЛИ 61 осуществляет вычитание единицы в реверсивном счетчике 42. В процессе проверки всего контрольного текста могут иметь место повторные сбои стыка ,фик- сируемые счетчиком 40.

Когда в процессе контроля счетч1Ж 40 отсчитывает S сигналов, на выходе декодера 39 возникает сигнал Стык неустойчив.

Сигналом с выхода элемента И 23 через второй элемент ИЛИ 6 триггер 12 возвращается в исходное состояние. Триггер 12 функционирует в тот отрезок контрольного цикла, когда происходит индентификация ошибок стыка.

Таким образом, если при повторном выводе из блока 65 кодовой комбина- .

ции сумматор 21 обнаруж1шает ошибку, она относится к сбою стыка между блоком 65 и устройством контроля и фик5.

сируется счетчиком 40 (а в счетчике 33 и реверсивном счетчике 42 стирается) .

Если при повторной проверке сумматор 21 ошибки не обнаруживает, то ранее зафиксированная сумматором 8 ошибка может быть либо не обнаруженной в блоке 65 ошибкой, либо ошибкой, возникшей под влиянием нарушения синфазности в поступлении комбинаций на входы первого сумматора 8, либо ошибкой под влиянием устойчивого отказа в стыке между блоком 65 и устройством -контроля.

В этом случае на выходе первого элемента НЕ 17 возникает инвертированный (единичный) сигнал, котррьй через элемент И 13, элемент ИЛИ 6 и элемент 9 задержки возвращает триггер 12 в исходное (единичное) состояние. В результате запираются для прохождения сигналов элементы И 13, 23 и 35, но при этом счетчик 33 и реверсивный счетчик 42 хранят отсчет одной не обнаруженной в блоке 65 ошибки.

Сигнал с выхода третьего элемента И 13 через элемент ИЛИ 4, элемент 27 задержки и элемент И 28 вновь формирует сигнал Готовность, по которому аналогично описанному на сумматор 8 поступают очередные комбинации от ДКТ 2 и из блока 65 и вновь продолжается поочередное сравнение комбинаций. Если при этом ошибок не обнаруживается, то таймер 15, запущенный сигналом ошибки с.выхода первого сумматора 8, через интервал .времени, превышающий момент возможного выхода следующего сигнала ошибки, если бы она возникла, воздействуя через пятый элемент ИЛИ 18, возвращает второй триггер 22 в исходное состояние.

Кроме этого, выходной сигнал таймера 15 через восьмой элемент ИЛИ 32 осуществляет сброс первого счетчи- .ка 33.

Таймер 15 вместе с триггером 22 обнаруживает, подряд идущие сигналы ошибок, число которых считает счетчик 33, при нарушении синфазности поступления комбинаций на первьй сумматор 8 и при устойчивом, отказе. . Если в процессе дальнейшего по- комбинационного контроля сумматор 8 вновь обнаруживает ошибку, то повторно включается механизм проверки исправности стыка между блоком 65 и

176676

устройством контроля. При этом сигналом с выхода элемента И 5 в нуле- вое состояние устанавливается триггер 12, запирая элемент И 19 и откры- , вая элементы И 13, 26 и 35. Кроме того, сигнал ошибки.с выхода первого элемента И 5 вновь записывает единицу в счетчик 33, в результате чего на первом выходе декодера 34 вновь

10 возникает сигнал, образующий на выходе элемента И 35 сигнал Повторение. В сумматоре 21 выполняется операция сравнения комбинации из регистра 20 и комбинации повторно поступив15 шей из.блока 65. В случае несравнения осуществляется фиксация ошибки стыка в счетчике 40 и вычитание единицы в реверсивном счетчике 42. В случае отсутствия ошибки стыка обна20 РУженная первым сумматором 8 ошибка сначала квалифицируется как не обнаруженная в блоке 65 ошибка и запоминается реверсивным счетчиком 42. Если рассмотренная ошибка - одиночная,

25 то таймер 15 сбрасыв.ает в исходное . состояние второй триггер 22, .

В процессе сравнения комбинаций с выхода блока 65 и выхода ДКТ 2 уст30 ройство для контроля тракта отдельно фиксирует либо ошибки стыка между блоком 65 и собственно устройством контроля, либо ошибки, не обнаруженные в блоке 65. При этом производит-

.jc ся анализ,не являются ли обнаруженные ошибки результатом нарушения синфазности или устойчивого отказа.

По результатам этого анализа уточняется число зафиксированньсх не об- 40 наруженных в блоке 65 ошибок.

В известном устройстве ошибки стыка обнаруживаются с помощью сумматора по модулю три. Но так Kaic указанный сумматор обнаруживает толь45 ко одиночные ошибки, то имеют место случаи, когда ошибки стыка между блоком 65 и устройством контроля, не обнаруженные ci MMaTopoM по модулю три, зачисляют в разряд не обнару50 женных в АЛД ошибок, т.е. основная функция устройства контроля по выяв-. лению не обнаруженных в АДЦ ошибок в прототипе выполняется с низкой достоверностью.

55 В предложенном устройстве ошибки стыка выявляются при поэлементном сравнении комбинаций (ранее принятой с ошибкой и повторенной), т.е. полностью исключается ложное зачисление.ошибок стыка в разряд ошибок, не обнаруженных в блоке 65, что и определяет высокую достоверность выявления не обнаруженных в блоке 65 ошибок,

Если число ошибок стыка, зафиксированное вторым счетчиком 40, превышает наперед заданное число S, на выходе декодера 39 возникает сигнал Стык-неустойчив.

За состоянием реверсивного счетчика 42 следит декодер 43, который при достижении L ошибок формирует сигнал Предупреждение, а при возникновении R ошибок - сигнал Аварийное состояние. Эти сигналы являются исходными при формировании устройством одноименных внешних управляющих сигналов с помощью триггеров 30 и 48, а также элементов И 38, 47 и 49.

Сигнал предупреждение с первого выхода декодера 43 устанавливает триггер 30 в нулевое состояние, характеризующееся единичным потенциа-. лом на нулевом выходе. Благодаря этому по второму входу открывается злемент И 47 и закрьшается (за счет нулевого потенциала на единичном выходе третьего триггера 30) элемент И 38. Когда число ошибок, зафиксированное реверсивным счетчиком 42 R, на втором выходе четвертого декодера 43 возникает сигнал Аварийное состояние, под воздействием которого триггер 48 устанавливается в единичное состояние, открьтая единичным потенциалом с единичного выхода элемент И 49 и запирая нулевым потенциалом с нулевого выхода элемент И 47.

Формирование одного из трех сигналов, характеризующих результат контроля Норма, Предупреждение или Аварийное состояние происходит по окончании вывода контрольного текста из ДКТ 2. В этот момент на выходе первого декодера 1 возникает сигнал Конец текста (КТ), который одновременно поступает на соответствующие входы элементов И 38, 47 и 49. В зависимости от состояния триггеров 30 или 48 возникает либо сигнал Норма на выходе элемента И 38, либо сигнал Предупреждение - на выходе элемента И 47, либо сигнал Аварийно состояние - на выходе элемента И 49

Триггер 22 совместно с сопряженными с ним элементами обнаруживает

подряд идущие сигналы ошибок. Это необходимо для того, чтобы выявить нарушение синфазности между комбинациями, поступающими из блока 65, и

опорными комбинациями с выхода дат- чика 2, и установить возникновение в системе устойчивого отказа.

Если устройство обнаружит К подряд идущих сигналов ошибки, то оно

должно выполнить операцию по установлению синфазности поступления комбинаций на сравнение следующим образом.

Первый возникший сигнал ошибки

с выхода сумматора 8 через элемени И 5, элемент ИЛИ 10 и элемент 14 задержки устанавливает в единичное состояние триггер 22, открьшающий по первому входу элемент И 24 и запирающий по третьему входу элемент И 5. Поэтому запись первого сигнала ошибки в реверсивный счетчик 42 осуществляется с выхода элемента И 5 через элемент ИЛИ 29, а идущий подряд второй сигнал ошибки 42 поступает в реверсивный счетчик через элемент И 24 и элемент ИЛИ 29.

Первый возникший сигнал ошибки с выхода элемента И -5 через элемент

ИПИ 11 осуществляет сброс таймера 15, который под воздействием того же сигнала ошибки, но задержанного элементом 14 задержки, вновь запускается.

Время появления выходного сигнала

таймера 15 от момента его запуска превьш1ает время поступления подряд идущего второго сигнала ошибки, поэтому при возникновении подряд идущих ошибок переброс триггера 22 не происходит, что обеспечивает прохождение второго сигнала ошибки через элемент И 24 и далее через элемент

ИПИ 29 на запись в счетчик 33 и реверсивный счетчик 42.

Кроме того, сигнал с выхода элемента И 24 через элемент ИЛИ 11 осуществляет; сброс таймера 15, а через

элемент ИЛИ 10 и элемент 14 задержки - повторный его запуск, что обеспечивает фиксацию третьего подряд идущего сигнала ошибки и т.д.

Если имеет место нарушение синфазности при сравнении комбинаций, то на первый счетчик 33 поступает серия подряд идущих сигналов ошибки. Когда число их достигает К, на выходе декодера 34 возникает сигнал, ко

торый устанавливает триггер 45 в единичное состояние. При этом единич ньм потенциалом с его единичного выхода открываются по одному из входов элементы И 37, 50 и 16, а нулевым потенциалом с нулевого выхода запираются элементы И 28, 25, 2.4, 7 и 5.

Через-открывшийся элемент И 37 к дат 2 из блока 65 поступает последовательность тактовых импульсов с частотой следования, на два-три порядка превьппающей частоту следования тактовых импульсов, которые блок 65 выдает при выполнении операций сравнения комбинаций.

Высокочастотная тактовая последовательность с выхода элемента И 37 поступает также на делитель 52 частоты, который производит деление час- тоты следования в таком же соотношении, в каком соотносятся между собой частоты повторения выходящих из блока 65 при выполнении операции сравнения тактовых импульсов и сигналов Пуск ДКТ.

Выходные импульсы делителя 52 частоты при установлении синфазности выполняют ту же функцию, что и сигналы Пуск ДКТ при основном функционировании устройства (операция сравнения комбинаций).

Закрытый под влиянием триггера 45 элемент И 28 прерывает вькод сигнала Готовности, -закрытьй элемент И 25 отключает сигнал Пуск ДКТ, закрытый седьмой элемент И 24 прерывает выход сигналов ошибок на счетчик 33 и реверсивньй счетчик 42, закрытый элемент И 7 отключает подачу тактовых импульсов с рабочей частотой следования, закрытый элемент И 5 прерывает поступление сигналов ошибки в счетчик 33 и реверсивный счетчик 42. В результате происходит такая перестройка схемы, что на второй вход сумматора 8 на все вре- мя установления синфазности через открытый элемент И 16 подается комбинация, при сравнении с которой был выработан К-й сигнал ошибки.

На первый вход сумматора 8 на очень большой скорости последовательно поступают комбинации от датчика 2, составляющие контрольньй текст. Если в системе не произошел устойчивый отказ, то на некотором цикле сравнения возникает совпадение ком

10

20

31766710

бйнации от датчика 2 с комбинацией, выставленной с выхода регистра 20. В этот момент сигнал ошибки на выходе сумматора 8 отсутствует и, следовательно, на выходе элемента НЕ 46 возникает единичный сигнал (ОШ), которьй на выходе открытого пятнадцатого элемента И 50 образует сигнал Синфазноеть.

При отсутствии отказа появление сигнала Синфазность указьшает на то, что при переходе вновь в режим сравнения комбинаций очередная комбинация из блока 65, следующая

15 за комбинацией, при сравнении с которой был выработан К-й сигнал ошибки, совпадает с очередной комбинацией из ДКТ 2.

Основное функционирование устройства (сравнение комбинаций) продолжается после перестройки схемы под воздействием сигнала Синфазность. При этом указанный сигнал с выхода пятнадцатого элемента И 50

25 через восьмой элемент ИЛИ 32 осуществляет сброс первого счетчика 33, производит сброс таймера 44, а также после задержки элементом 54 задержки через элемент ИЛИ 36 возвра ца30 ет в исходное состояние триггер 45, благодари чему закрываются элементы И 37, 50, 16 и открываются элементы И 28, 25, 24, 7 и 5. Кроме того, для восстановления рабочего состоя35 ния устройства и реверсивном счетчике 42 должны быть стерты К импуль-. сов, которые бьши в нем записаны во время выполнения операции по установлению синфазности. Это выполняет40 ся на очень большой скорости с использованием той же высокочастотной последовательности, которая обеспечивает установление .синфазности. При этом счетчик 62, управляемый

45 триггером 58, отсчитьшает К импульсов, которые поступают на вычитающий вход реверсивного счетчика 42.

Задержанный элементом 54 задержки сигнал Синфазность с выхода Cj (за50 держка устанавливает триггер 58 в единичное состояние, благо- - даря чему открьгоается по первому входу элемент И 59. Это обеспечивает поступление на счетчик 62 и через

55 элемент ИЛИ 61 на вычитающий вход реверсивного счетчика 42 серии высокочастотных тактовых импульсов. Когда количество поступивших высокочастотных импульсов достигает К, на выходе декодера 63 возникает сигнал, который через элемент 64 задерж ки и элемент ИЛИ 60 возвращает триггер 58 в исходное (нулевое) состоя- ние. При этом закрьшается семнадцатый элемент И 59 и прекращается поступление импульсов на вычитающий вход реверсивного счетчика 42.

Таким образом, в реверсивном счетчике 42 остаются зафиксированными только ранее записанные ошибки, не обнаруженные в блоке 65, а сигналы ошибок, возникшие вследствие нарушения синфазности, стираются.

Задержанный сигнал Синфазность с выхода, через элемент ИЛИ 4, элемент 27 задержки, элемент И 28 формирует сигнал Готовность, по которому вновь возобновляется срав- нение комбинаций.

После завершения проверки контрольного текста по сигналу КТ в устройстве формируется оценка результата выполненной операции сравнения - Норма, Предупреясдение или Ав.а- рийное состояние.

Появление К ошибок, зафиксированных в счетчике 33 и реверсивном счетчике 42, может быть вызвано не на- рушением синфазности в системе, а устойчивым отказом в блоке 65 или в устройстве контроля.

В этом случае сигнал Синфазность либо вообще не формируется, либо возникает ложный сигнал.

Поэтому в устройстве предусмотрен соответствующий контроль. Сигналом t выхода К декодера 34 запускается таймер 44. Выходной сигнал таймера 44 может появиться через интервал времени, превышающий максимальное расчетное время выполнения операции по установлению синфазности, поэтому с появлением сигнала синфазности таймер 44 сбрасьтается в О.. Если сигнал синфазности в заданное время не поступает, та.ймер 44 формирует сигнал Отказ, .который через элемен ИЛИ 53 поступает на выход устройства

Возникновение ложного сигнала Синфазность обнаруживается следующим образом.

Задержанным в элементе 54 задержки сигналом Синфазность (с выхода ) в единичное состояние устанавливается седьмой триггер 55, единичный потенциал с единичного выхода которого открывает по первому входу эле-

5

д

5

мент И 57, На второй вход последнего подаются сигналы с выхода элемента ИЛИ 29. Единичное состояние триггера 55 длится в течение интервала времени, задаваемого элементом 56 задержки, выходной сигнал которого через элемент ИЛИ 51 возвращает триггер 55 в исходное состояние.

Поэтому, если после возобновления операции сравнения в первом ее цикле на выходе элемента ИЛИ 29 возникает сигнал ошибки, что характерно для случая формирования ложного сигнала Сийфазность , то этот сигнал проходит через элемент И 57, образуя на выходе элемента ИЛИ 53 сигнал Отказ. По сигналу Отказ работа должна быть прекращена с помощью триггера 31, который в начале работы устанавливается в единичное состояние сигналом Наличие информации из блока 65, благодаря чему открыты по соответствующим входам элементы И 28, 5 и 24.

По сигналу Отказ четвертый триг гер 31 возвращается в нулевое состояние, элементы И 28, 5 и 24 запираются, и функционирование устройства прекращается до устранения отказа. При этом по сигналу Отказ осуществляется также сброс в О счетчика 33 и реверсивного счетчика 42, а также установка триггера 45 в нулевое состояние (через девятый элемент ИЛИ 36) и триггера 58 также в О через элемент ИЛИ 60.

Формула изобретения

Устройство для контроля тракта передачи данных, содержащее последовательно соединенные распределитель и датчик контрольного текста, первый счетчик, последовательно соединенные первьш сзт матор, первьй вход которого соединен с выходом датчика контрольного текста и первьй элемент И, блок передачи данных, первый элемент ИЛИ, первый вход которого соединен с первым выходом блока передачи данных и вторым входом датчика контрольного текста, первый вход распределителя соединен с первым выходом блока передачи данных,. отличающееся тем, что, с целью повьш1ения достоверности при одновр.еменном повьш1ении быстродействия, в него введены первьй декодер, последовательно соединенные

13131

второй элемент ИЛИ, первый элемент задержки и первый, триггерj второй вход которого соединен с выходом первого элемента И, поспедовательно соединенные третий элемент ИЛИ первый вход которого соединен с выходом первого элемс} та И, второй элемент задержки и второй триггер, последовательно соединЕ;ННые четвертый элемент ИЛИ, первый вход кото- роге соединен с выходом первого элемента И, первый таймер5 второй вход которого соединен с выходом второго элемента задержки,, к пятьй элемент ИЛИ, выход которого подклк чен к второму входу второго триггера вькод четвертого элемента ИЛИ подключен к второму входу третьего гзлемента ИЛИ, второй элемент И, выход и первый вход которого соединены соответственно с вторым входом распределителя и вторым выходом блока нерецачрт данных, последовательно соединенные регистр, второй сумматор, первый элемент НЕ и третий элемент И, второй вход и выход которого соединены соответственно с выходом первого триггера и объединенными первым и Бторьгм входами соответственно кторо- го и первого элемгн7 ов ИЖц тмследо - вательно соеди;; .иные четвертый -элемент И , первый вход которого сое- динек с выходом регистра; и :;естой элемент ИЛИ, выход и второй вход которого соединены соответственно с вторьм входом первого с/уммагора, второй выход которого подключен к третьему входу первого элемента ЖШ и BTOpbiM входом второго С умматора и третьим выходом блока передачи данных, пятый элемент И, вьмод и первый вход которого соед1шены соответственно с входом регистра и вторьм входом шестого элемента ИПИ,, а второй вход соединен с первму; выходом первого триггера и Е;торым входом второго элемента И, третий вход которого соединен с вторым входом первого элемента И, шестой элемент И), первый вход и выход которого соединены соответственно с выходом второго сумматора и вторым входом второго элемента ИЛИ и четверть ; входом первого элемента HJTO, а второй вход шестого элемента И соединен с выходом первого триггера и вторым входом третьего элемента И, последовательно сор-дииенкые седьмой элемент И, первьщ вход которого сосдк 7 .14

нен с первым выходом второго триггера, второй выход которого подключен к третьему входу первого элемента И, и седьмой элемент HJTIi, второй вход и выход которого соединены соответственно с выходом первого элемента И, четвертый вход которого соединен с вторым входом седьмого элемента И и с первым входом первого счетчика,

восьмой элемент И, первый вход и выход которого соединены соответственно с четвертым вьгх;одом блока передачи данных и третьз-Е 1 входом датчика контрольного текста, последовательно

соединенные третий элемент задержки, вход Kotoporo соединен с выходом первого элемента ИЛИ,.и девятый элемент И5 вы.ад которого подключен к первому входу блока передачи данных,

восьмой элемент ИЛИ,, первый, второй и тpeти; вхо.цы и выход которого соединены соответственно с выходом шестого элемента И. первым выходом блока передачи данных, выходом пятого элемента ИЛИ и вторым входом первого счетчика, последовательно соединенные второй декодер вход которого соединен с выходом первого счетчика, и десятый элемент И, второй вход и выход которого соед Шены соответственно с вторым выходом первого триггера и вторым входом блока передачи данных, последовательно сое- диненные второй счетчик, первый и

второй входы которого соединены соответственно с первьпч выходом блока передачи данных и выходом шестого элемента И, и. третий декодер, реверсивный счетчш-с, последовательно

соединенные четвертый декодер, вход которого соединен с выходом реверсивного счетчика, и третий триггер, второй вход которого соединен с первым выходом блока передачи данных,

четвертый триггер, первый вход и выход которого соединены соответственно с первьм выходом блока передачи данных и вторыми входами девятого и седьмого элементов И, последовательно соединенные четвертый элемент задержки, девятью элемент ИЛИ, пятый триггер, второй вход которого соединен ::. вторьм выходом второго декодера, опяянадлатый элемент И, второй вход которого ::оеди 1им с пя- Tbnv выходом: блока передачи дгнньс-:., и делитель чястоть, вьпсод «отсфого подключен к четветтону входу датчика контролььог о текста, пятый вход

15

которого соединен с выходом одиннадцатого элемента И, двенадцатый элемент И, первый, второй и третий входы которого соединены соответственно с выходом первого декодера, вход которого соединен с вьтходом датчика контрольного текста, первым выходом третьего триггера.и выходом четвертого триггера, последовательно соединенные шестой триггер, первый и второй входы которого соединены соответственно с вторым выходом четвертого декодера и первым выходом блока передачи данных и тринадцатьй элемент И, второй, третий и четвертый входы которого соединены соответственно с вторым выходом третьего триггера, выходом четвертого триггера и выходом первого декодера, десятый элемент ИЛИ, первый вход и выход которого соединены соответственно с первым выходом блока передачи данных и первым входом реверсивнрго счетчика, четырнадцатый элемент И, первый, второй и третий входы которого соедире ны соответственно с вторым выходом шестого триггера, выходом четвертого триггера и выходом первого декодера, последовательно соединенные второй элемент НЕ, вход которого соединен с первым выходом первого сумматора, пятнадцатый элемент И, второй вход которого соединен с выходом пятого триггера, и второй таймер, второй вход которого соединен с вторым выходом второго декодера, выход пятнадцатого элемента И подключен к входу четвертого элемента задержки, второй выход которого подключен к пятому входу первого элемента ИЛИ, первый выход пятого триггера подключен к второму входу четвертого элемента И, выход пятнадцатого элемента И подключен к четвертому входу восьмого элемента ИЛИ, пятьй элемент задержки, вход которого соединен с вторым выходом четвертого элемента задержки, последовательно соединенные одиннадцатый элемент ИЛИ, первый вход которого соединен с выходом пятого элемента задержки, седьмой триггер, второй вход которого соединен с вторым выходом четвертого элемента задержки.

ВНИИПИ Заказ 2436/55

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

1766716

шестнадцатый элемент И, второй вход которого соединен с выходом седьмого элемента ИЛИ, двенадцатый элемент ИЛИ, второй вход которого

с соединен с выходом второго таймера, тринадцатый элемент ИЛИ, восьмой триггер, вто рой вход которого соединен с вторым выходом четвертого элемента з-адержки, семнадца тый элемент

10 И, второй вход которого соединен с пятым выходом блока передачи данных, третий счетчик, второй вход которого соединен с первым выходом блока передачи данных, пятьм декодер и шес15 той элемент задержки, выход которого подключен к второму входу тринадцатого элемента ИЛИ, четырнадцатый элемент ИЛИ, первый вход и выход которого соединены соответственно с

20 выходом семнадцатого элемента И и вторым входом реверсивного счетчика, а второй вход четырнадцатого элемента ИЛИ соединен с выходом шестого элемента И, выход двенадцатого эле25 мента ИЛИ подключен к второму входу девятого элемента ИЛИ, второму входу десятого элемента ИЛИ, пятому входу восьмого элемента ИЛИ и второму входу четвертого триггера, вто30 рой выход пятого триггера подключен к третьему входу девятого элемента И, второму входу восьмого элемента И, третьему входу седьмого элемента И и второму входу первого элемента И, вертый входи выход седьмого элемента И соединены соответственно с первым выходом первого сумматора и шестым входом первого элемента ИЛИ и вторым входом четвертого элемента

40 ИЛИ, третий вход тринадцатого элемента ИЛИ соединен с вторым входом одиннадцатого элемента ИЛИ, третьим входом девятого элемента ИЛИ, вторым входом пятого элемента ИЛИ и третьим

45 входом второго элемента ИЛИ, третий вход реверсивного счетчика соединен с выходом седьмого элемента ИЛИ, выходы двенадцатого элемента И, Т15И- надцатого элемента И, третьего де50 кодера, четырнадцатого элемента И и двенадцатого элемента- ИЛИ являются соответственно первым, вторым, третьим, четвертым и пятым выходами устройства, входом которого является

55 третий вход тринадцатого элемента ИЛИ.

Тираж 638

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля и регистрации служебных признаков в системе телемеханики | 1984 |

|

SU1275513A1 |

| Устройство для контроля системы телемеханики с решающей обратной связью | 1980 |

|

SU943805A1 |

| Датчик испытательных комбинаций | 1987 |

|

SU1496012A1 |

| Устройство адаптивного приема дискретных сигналов с амплитудно-фазовой модуляцией | 1986 |

|

SU1309319A1 |

| Устройство для синхронизации биимпульсного сигнала | 1985 |

|

SU1350837A1 |

| Датчик сообщений | 1985 |

|

SU1282348A1 |

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

| Устройство для контроля системы телемеханики | 1980 |

|

SU898489A1 |

| Устройство для передачи и приемаСигНАлОВ | 1979 |

|

SU830486A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Устройство для контроля тракта передачи данных | 1973 |

|

SU477547A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-15—Публикация

1985-12-26—Подача