13

при любом алгоритме коммутации фаз. Устройство содержит формирователь импульсов 3, коммутатор 2 фаз ШД15 блок синхронизации 4. Логический блок 5 содержит элемент сравнения кодов 7 и кольцевой сдвиговый регистр 6, информационные входы которого подключены к фазам ЦЦ1, управляющие входы - к выходам блока синхронизации 4, а выходы .- к входам сравнения В элемента сравнения кодов 7, входы сравнения А которого подключены к фазам ШД 1. Сдвиговые- импульсы с шины управления 10 производят сдвиг управляющих фаза

1

Изобретение относится к управлению электрическими машинами и может быть использовано в шаговом электроприводе с программным управлением.

Цель изобретения - расширение функциональных возможностей путем регистрации отка.зов при любом алгоритме коммутации фаз.

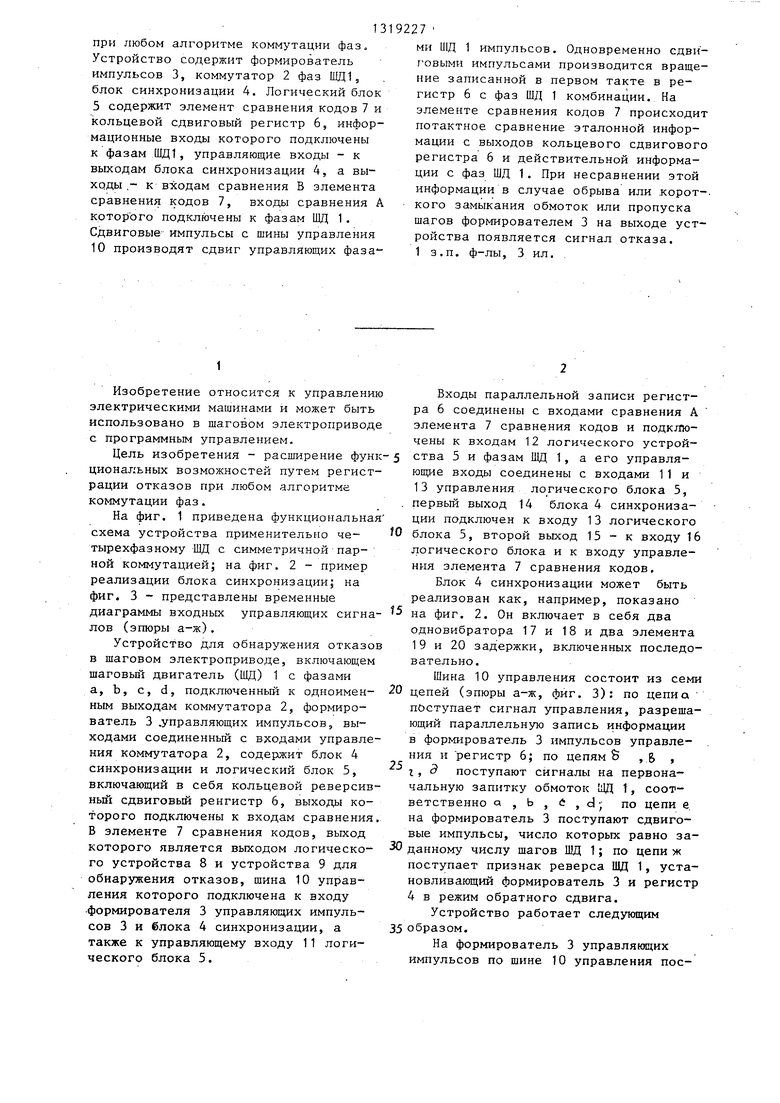

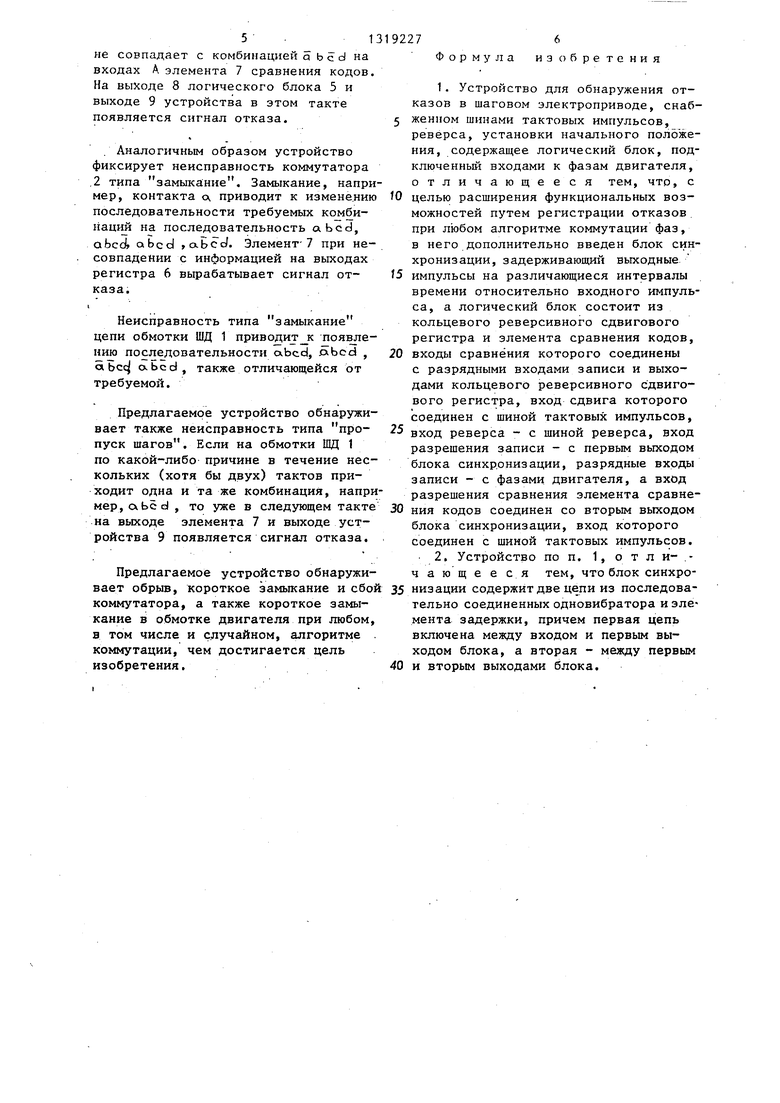

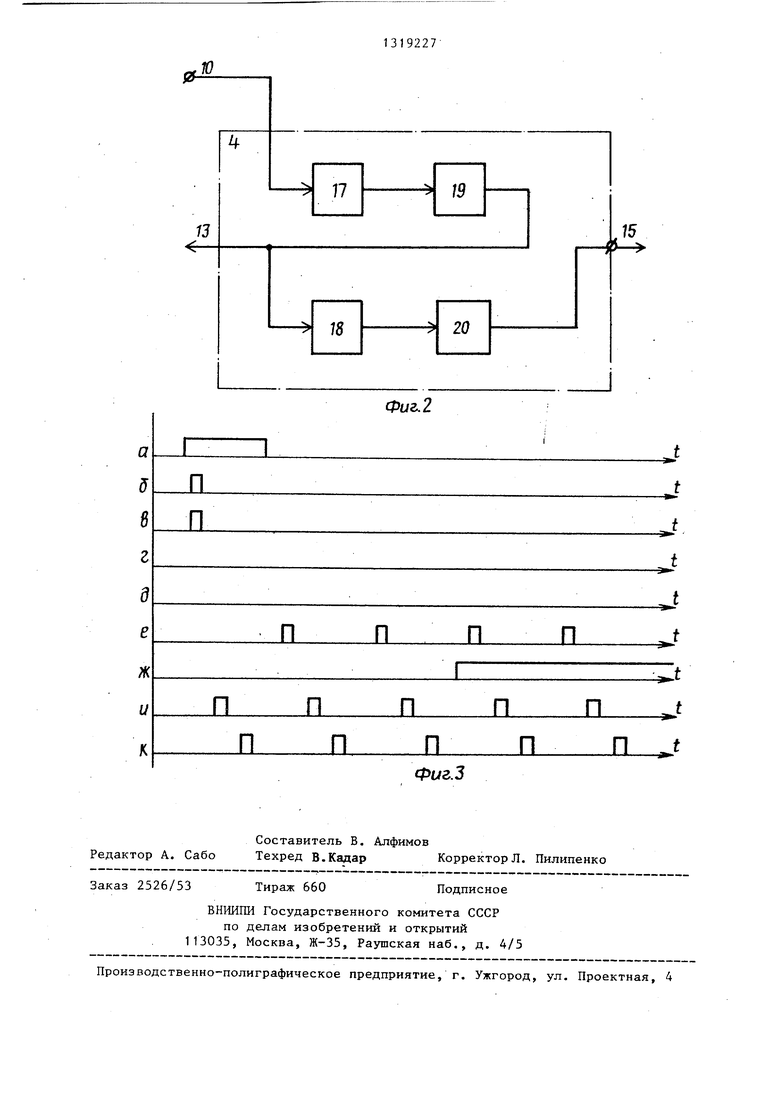

На фиг. 1 приведена функциональная схема устройства применительно че- тырехфазному ШД с симметричной парной коммутациейJ на фиг. 2 - пример реализации блока синхронизации; на фиг. 3 - представлены временные диаграммы входных управляющих сигналов (эпюры а-ж).

Устройство для обнаружения отказов в шаговом электроприводе, включающем шаговьй двигатель (ШД) 1 с фазами а, Ь, с, d, подключенный к одноименным выходам коммутатора 2, формирователь 3 .управляющих импульсов, выходами соединенный с входами управления коммутатора 2, содержит блок 4 синхронизации и логический блок 5, включающий в себя кольцевой реверсив- Hbrfi сдвиговый ренгистр 6, выходы которого подключены к входам сравнения. В элементе 7 сравнения кодов, выход которого является выходом логического устройства 8 и устройства 9 для обнаружения отказов, шина 10 управления которого подключена к входу формирователя 3 управляющих импульсов 3 и блока 4 синхронизации, а также к управляющему входу 11 логического блока 5.

9227

ми 111Д 1 импульсов. Одновременно сдвиговыми импульсами производится вращение записанной в первом такте в регистр 6 с фаз ШД 1 комбинации. На элементе сравнения кодов 7 происходит потактное сравнение эталонной информации с выходов кольцевого сдвигового регистра 6 и действительной информации с фаз ШД 1. При несравнении этой информации в случае обрыва или корот-. кого замыкания обмоток или пропуска шагов формирователем 3 на выходе устройства появляется сигнал отказа. 1 3.п. ф-лы, 3 ил. .

Входы параллельной записи регистра 6 соединены с входами сравнения А элемента 7 сравнения кодов и подключены к входам 12 логического устройства 5 и фазам ШД 1, а его управляющие входы соединены с входами 11 и 13 управления логического блока 5, . первый выход 14 блока 4 синхронизации подключен к входу 13 логического

блока 5, второй выход 15 - к входу 16 логического блока и к входу управления элемента 7 сравнения кодов.

Блок 4 синхронизации может быть реализован как, например, показано

5 на фиг. 2. Он включает в себя два одновибратора 17 и 18 и два элемента 19 и 20 задержки, включенных последовательно.

Шина 10 управления состоит из семи

0 цепей (эпюры а-ж, фиг. 3): по цепиа поступает сигнал управления, разрешающий параллельную запись информации в формирователь 3 импульсов управления и регистр 6; по цепям S ,6 1,3 поступают сигналы на первоначальную запитку обмоток ШД 1, соответственно о , Ь , i , d J по цепи е на формирователь 3 поступают сдвиговые импульсы, число которых равно заданному числу шагов ШД 1; по цепи ж поступает признак реверса ШД 1, уста- новливающий формирователь 3 и регистр 4 в режим обратного сдвига.

Устройство работает следующим

5 образом.

На формирователь 3 управляющих импульсов по шине 10 управления пос313192274

тупают сигналы первоначальной запит- сдвига (эпюра е, фиг. 3). Блок син- ки обмоток (эпюры б-д, фиг. 3) и хронизации вырабатывает импульсы синхронизации регистра 6, сдвигающие информацию в регистре и импульсы разсигнал разрешения параллельной записи (эпюра а, фиг. 3). Коммутатор 2, управляемый формирователем 3, включает соответствующие обмотки ШД 1. На фазы ШД 1 п оступает комбинация, например, abed , где символ без черты обозначает высокий потенциал.

решения сравнения (эпюра к, фиг. 3).

Эти импульсы поступают на входы регистра 6 и элемента 7 сравнения кодов через входы 13 и 16 логических блоков соответственно. При необходи- а с чертой - низкий. Сигнал разреше- fo мости на формирователь 3 и вход 11 ния параллельной записи по тиине 10 логического блока может быть подан управления поступает на регистр 6 сигнал реверса (эпюра ж, фиг. 3). и блок 4 синхронизации, а появйвшая- При отсутствии неисправностей после ся на фазах ШД 1 комбинация поступает первого импульса сдвига на фазах ШД 1 на входы сравнения А элемента 7 срав-fj и входах сравнения А элемента 7 сравнения кодов и записывается в регистр нения кодов появляется комбинация 6 по сигналу с первого выхода 14 блока синхронизации 4 (эпюра и, фиг. 3). Записанная в регистр 6 информация поступает с его вькодов на входы сравнения 6- блока 7 сравнения кодов..

Таким образом, комбинации на вхо20

(пpи вращении по часовой стрелке), после второго импульса -abed, после третьего - аЪ с d, после четвертого - abed .

Такие же комбинации появляются на выходах регистра 6 в результате синхронного с вращением ШД 1 сдвига

Такие же комбинации появляются на выходах регистра 6 в результате синхронного с вращением ШД 1 сдвига

дах сравнения А и В блока 7 сравнения

кодов одинаковы и на выходе устройст-25 информации, записанной в регистр 6

ва 9 сигнал отказа отсутствует, а - перед началом вращения. Сдвиг осурегистр 6 запоминает информацию, записанную с обмоток ШД.

Блок 4 синхронизации работает следующим образом. Одновибратор 17 за- ЗО пускается сигналами, поступающими с .шины 10 управления (эпюры б-е, фиг.З). Одновибратор 17 вырабатывает короткий импульс, который задерживается элеществляется импульсами, появляющимися на первом выходе 14 блока 4 синхронизации. Информация с выхода регистра 6 поступает на входы В элемента 7 сравнения кодов. Так как на входах сравнения А и 6 элемента 7 сравнения кодов одинаковые сигналы, то с приходом на вход управления сигнала ментом 19 задержки на время, необхо- с второго выхода 15 схемы 4 синхродимое для завершения переходных про- -цессов в формирователе 3 и коммутаторе 2, и с выхода элемента 19 задержки поступает на первый выход 14 блока синх зонизации (эпюра и фиг. 3). о и на вход второго одновибратора 18. .Второй Одновибратор 18 вырабатывает короткий импульс, который задерживается элементом 20 задержки на время,

необходимое для завершения переходных -мутатора 2 на фазе а ЧЩ 1 не может процессов в регистре 6 при записи в появиться высокий потенциал, т.е. него информации или сдвиге и появляется на втором выходе 15 схемы 4 синхронизации (эпюра к, фиг. 3).

Первоначальная запитка обмоток jg ром - oibcd,B третьем -cibcd, в ШД 1 осуществляется один раз в нача- четвертом -abed. Соответственно в ле работы ШД 1. Повтор запитки обмоток в процессе работы может быть использован для коррекции запитки обмоток в результате обнаружения отказа. 55 первого сдвигового импульса со

Для осуществления вращения ШД 1 схемы синхронизации изменяется на по шине 10 управления на формирователь 3 управляющих импульсов и блок 4 синхронизации поступают импульсы

низации на ее выходе и на выходе 8 логического устройства 5 и, соответственно, па выходе устройства 9 сигнал отказа отсутствует.

Наличие в коммутаторе 2 неисправностей типа обрыв приводит к пропаданию сигналов на соответствующих входах 12 логического устройства 5. При обрыве, например, в фазе ot комвместо требуемой последовательности комбинаций имеет мecтo пo CJ eдoвaтeль- ность: в первом тактеаЬс4 во вторегистр 6 в такте запитки ШД 1 записывается комбинация cxboJ, соответ- ствующдя коду 0100, который с прихокод 0010. Следовательно, во втором такте на выходе регистра 6 комбинация а Ьс4 соответствующая коду 0010,

решения сравнения (эпюра к, фиг. 3).

Эти импульсы поступают на входы регистра 6 и элемента 7 сравнения кодов через входы 13 и 16 логических блоков соответственно. При необходи- o мости на формирователь 3 и вход 11 логического блока может быть подан сигнал реверса (эпюра ж, фиг. 3). При отсутствии неисправностей после первого импульса сдвига на фазах ШД 1 fj и входах сравнения А элемента 7 сравнения кодов появляется комбинация

0

(пpи вращении по часовой стрелке), после второго импульса -abed, после третьего - аЪ с d, после четвертого - abed .

Эти импульсы поступают на входы регистра 6 и элемента 7 сравнения кодов через входы 13 и 16 логических блоков соответственно. При необходи- ости на формирователь 3 и вход 11 огического блока может быть подан сигнал реверса (эпюра ж, фиг. 3). При отсутствии неисправностей после первого импульса сдвига на фазах ШД входах сравнения А элемента 7 срав нения кодов появляется комбинация

Такие же комбинации появляются на выходах регистра 6 в результате синхронного с вращением ШД 1 сдвига

ществляется импульсами, появляющимися на первом выходе 14 блока 4 синхронизации. Информация с выхода регистра 6 поступает на входы В элемента 7 сравнения кодов. Так как на входах сравнения А и 6 элемента 7 сравнения кодов одинаковые сигналы, то с приходом на вход управления сигнала с второго выхода 15 схемы 4 синхро -низации на ее выходе и на выходе 8 логического устройства 5 и, соответственно, па выходе устройства 9 сигнал отказа отсутствует.

Наличие в коммутаторе 2 неисправностей типа обрыв приводит к пропаданию сигналов на соответствующих входах 12 логического устройства 5. При обрыве, например, в фазе ot ком-мутатора 2 на фазе а ЧЩ 1 не может появиться высокий потенциал, т.е.

ром - oibcd,B третьем -cibcd, в четвертом -abed. Соответственно в первого сдвигового импульса со

вместо требуемой последовательности комбинаций имеет мecтo пo CJ eдoвaтeль- ность: в первом тактеаЬс4 во втором - oibcd,B третьем -cibcd, в четвертом -abed. Соответственно в первого сдвигового импульса со

регистр 6 в такте запитки ШД 1 записывается комбинация cxboJ, соответ- ствующдя коду 0100, который с прихосхемы синхронизации изменяется на

код 0010. Следовательно, во втором такте на выходе регистра 6 комбинация а Ьс4 соответствующая коду 0010,

не совпадает с комбинацией abed на входах А элемента 7 сравнения кодов. На выходе 8 логического блока 5 и выходе 9 устройства в этом такте появляется сигнал отказа.

Аналогичным образом устройство фиксирует неисправность коммутатора ,2 типа замыкание. Замыкание, например, контакта о, приводит к изменению последовательности требуемых комбинаций на последовательность abed, abed abed ,аЬсс/. Элемент 7 при несовпадении с информацией на выходах регистра 6 вьфабатывает сигнал от- каза.

I

Неисправность типа замыкание цепи обмотки ШД 1 приводит к появле- ниJp последовательности cxbcd, о bed , а bc о. bed, также отличающейся от требуемой.

Предлагаемое устройство обнаруживает также неисправность типа про- пуск шагов, Если на обмотки ШД 1 по какой-либо причине в течение нескольких (хотя бы двух) тактов приходит одна и та же комбинация, например, abed, то уже в следующем такте на выходе элемента 7 и выходе устройства 9 появляется сигнал отказа.

Предлагаемое устройство обнаруживает обрыв, короткое замыкание и сбой коммутатора, а также короткое замыкание в обмотке двигателя при любом, в том числе и случайном, алгоритме . коммутации, чем достигается цель изобретения.

Формула изобретения

1.Устройство для обнаружения отказов в шаговом электроприводе, снабженном шинами тактовых импульсов, реверса, установки начального положения, содержащее логический блок, подключенный входами к фазам двигателя, отличающееся тем, что, с целью расширения функциональных возможностей путем регистрации отказов при любом алгоритме коммутации фаз,

в него дополнительно введен блок синхронизации, задерживающий выходные импульсы на различающиеся интервалы времени относительно входного импульса, а логический блок состоит из кольцевого реверсивного сдвигового регистра и элемента сравнения кодов, входы сравнения которого соединены с разрядными входами записи и выходами кольцевого реверсивного сдвигового регистра, вход сдвига которого соединен с шиной тактовых импульсов, вход реверса - с шиной реверса, вход разрешения записи - с первым выходом блока синхронизации, разрядные входы записи - с фазами двигателя, а вход разрешения сравнения элемента сравнения кодов соединен со вторьм выходом блока синхронизации, вход которого соединен с шиной тактовых импульсов.

2.Устройство по п. 1, о т л и- .- чaющeecя тем, что блок синхронизации содержит две цепи из последовательно соединенных одновибратора и элемента задержки, причем первая цепь включена между входом и первым выходом блока, а вторая - между первым и вторым выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения отказов в шаговом электроприводе | 1987 |

|

SU1415401A1 |

| Устройство для обнаружения отказов в шаговом электроприводе | 1988 |

|

SU1511843A1 |

| Электропривод с устройством обнаружения отказов | 1990 |

|

SU1781811A1 |

| Устройство для программного управления шаговым двигателем | 1989 |

|

SU1675850A1 |

| Устройство для обнаружения отказов в шаговом электроприводе | 1989 |

|

SU1640811A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОТКАЗОВ В ШАГОВОМ ЭЛЕКТРОПРИВОДЕ | 1992 |

|

RU2037264C1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОТКАЗОВ В ШАГОВОМ ЭЛЕКТРОПРИВОДЕ | 1991 |

|

RU2032265C1 |

| Резервированный преобразователь напряжения в код | 1975 |

|

SU663101A1 |

| Устройство для имитации неисправностей | 1985 |

|

SU1283775A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПАРАМЕТРОВ НАПРЯЖЕНИЯ | 1990 |

|

RU2018147C1 |

Изобретение относится к электротехнике, а именно к электроприводу, и может быть использовано в системах управления шаговыми двигателями (ШД) с программным управлением. Цель состоит в расширении функциональных возможностей путем регистрации отказов сл lAd UD N3 О Ч

| Устройство для управления многофазным шаговым двигателем | 1976 |

|

SU547955A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для обнаружения отказов в системе управления шаговым двигателем | 1981 |

|

SU1029371A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-06-23—Публикация

1985-06-11—Подача