11

Изобретение относится к вычислительной технике и может быть использовано при отработке оборудования и программ, выполняющих контроль и диагностирование неисправностей.

Цель изобретения - расширение функциональных возможностей устройства за счет имитации неисправностей заданной длительности и имитации повторных неисправностей.

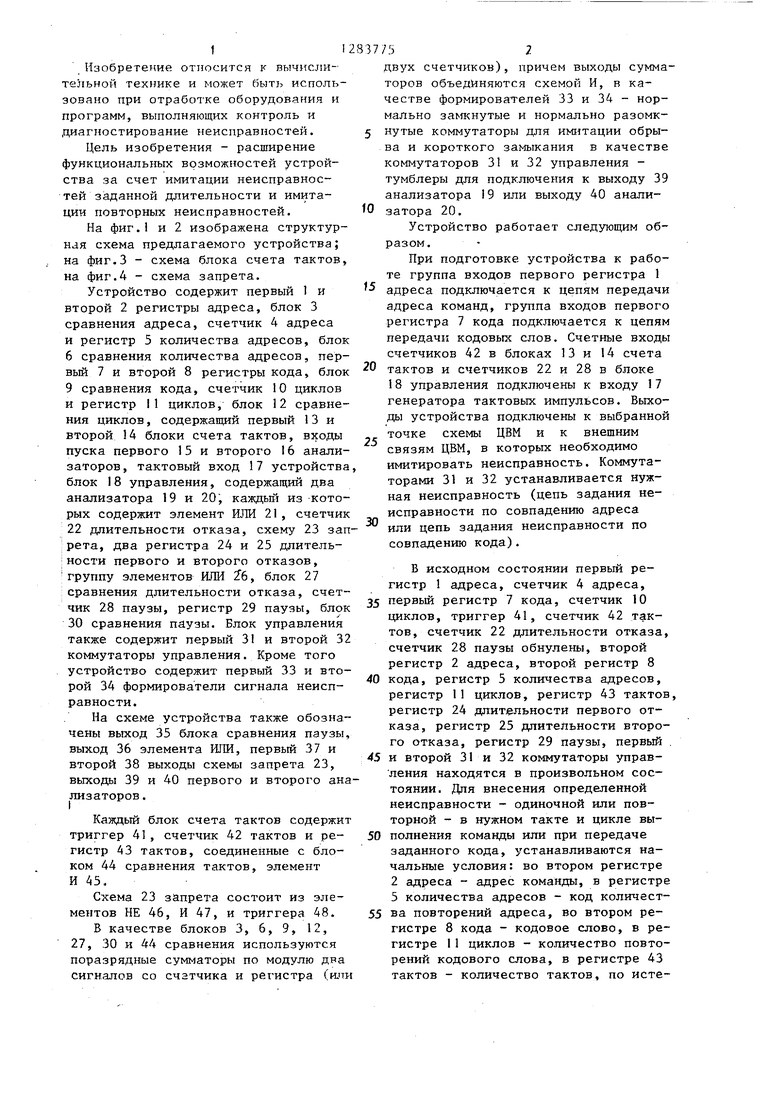

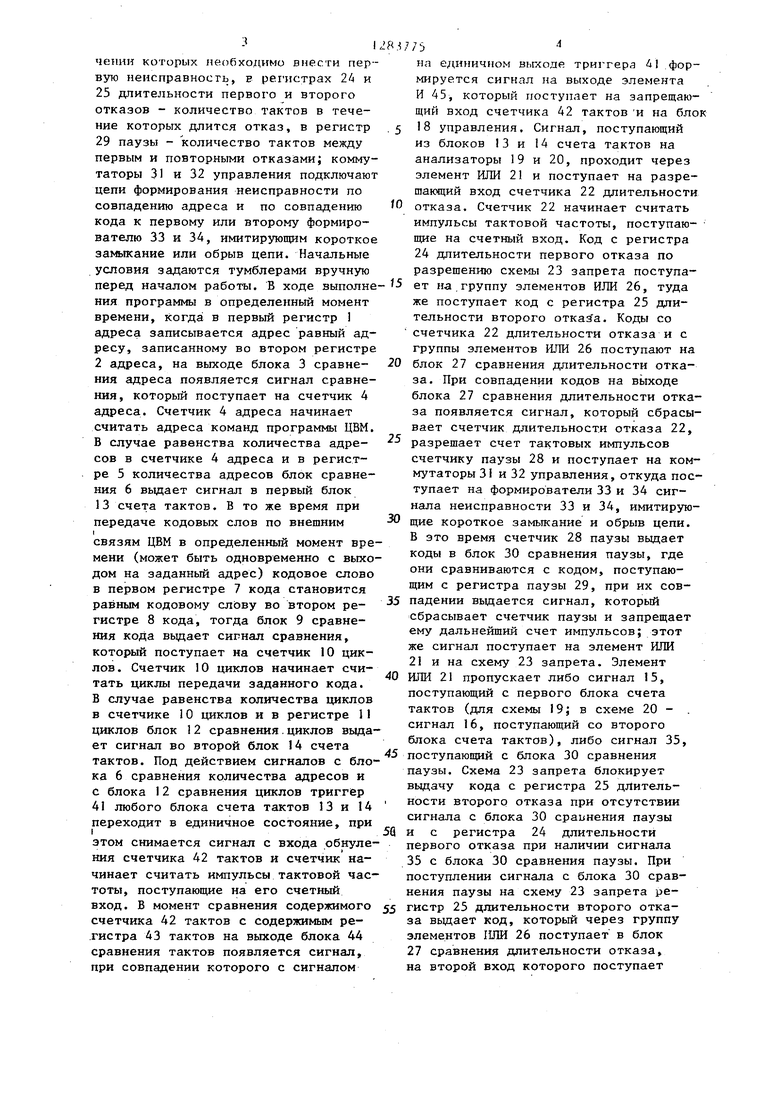

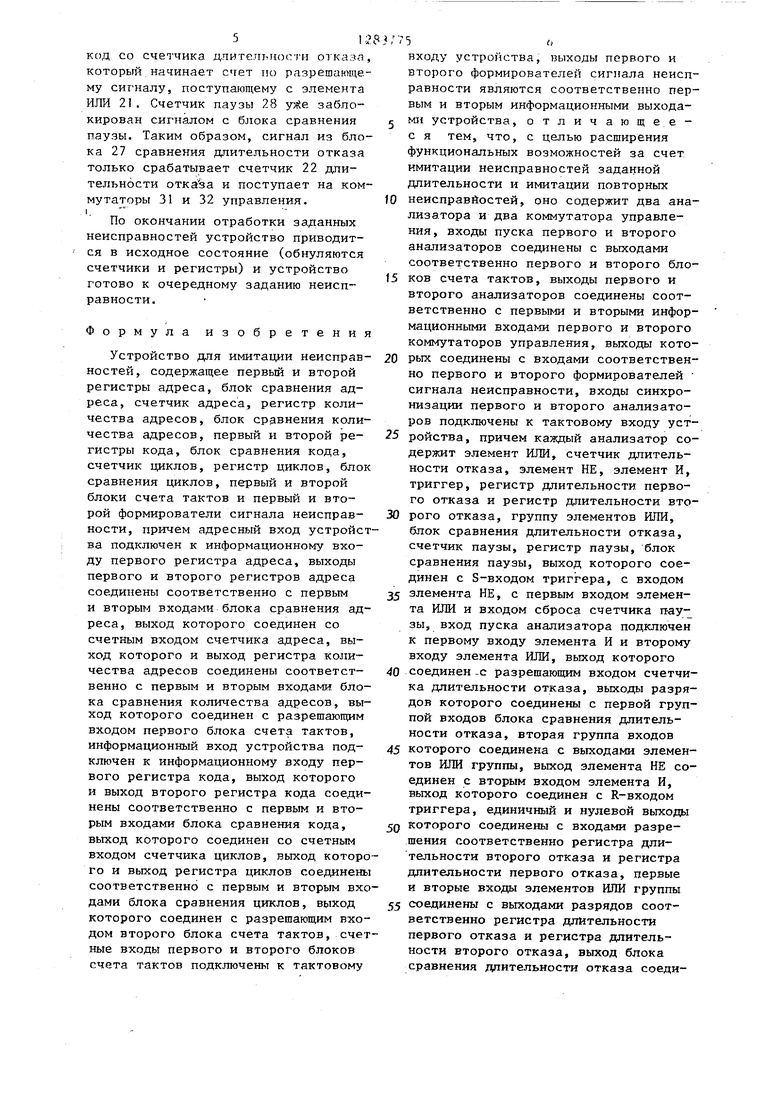

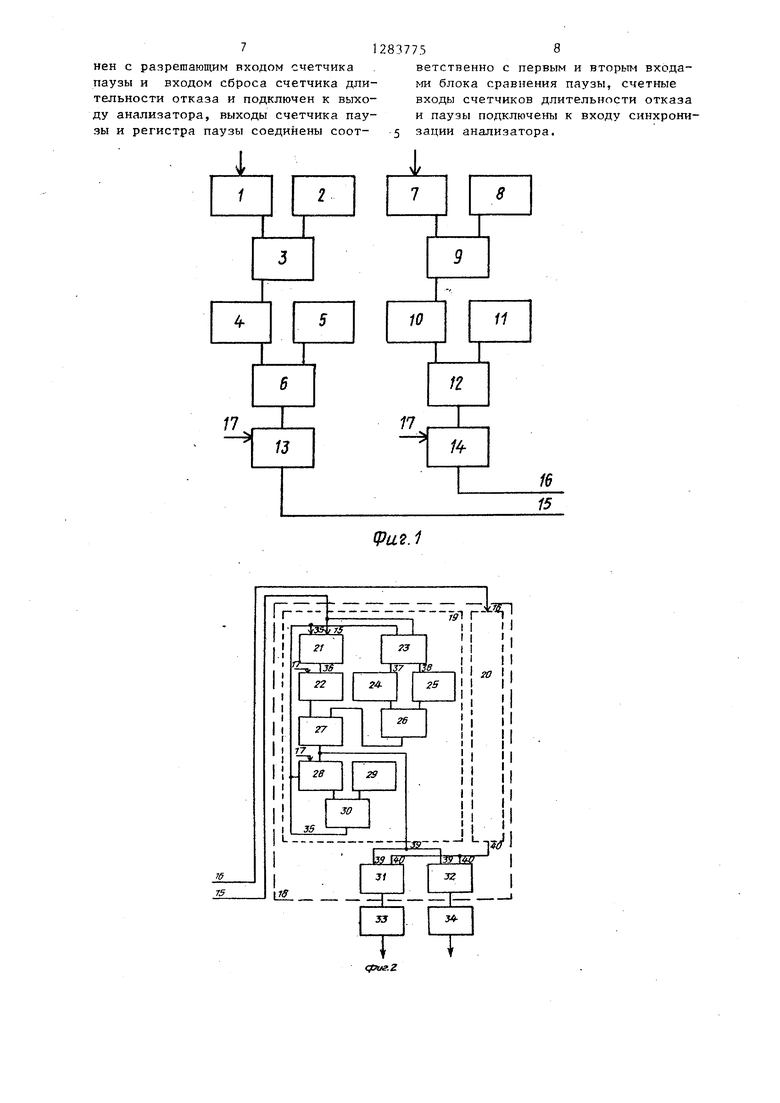

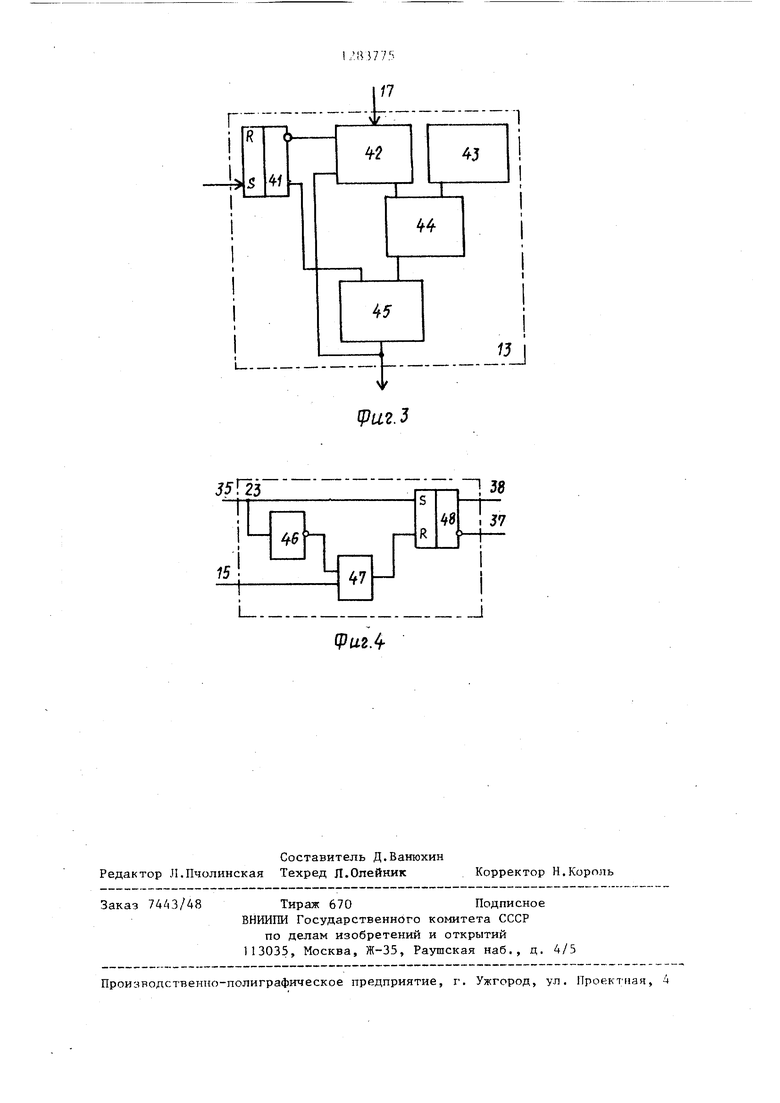

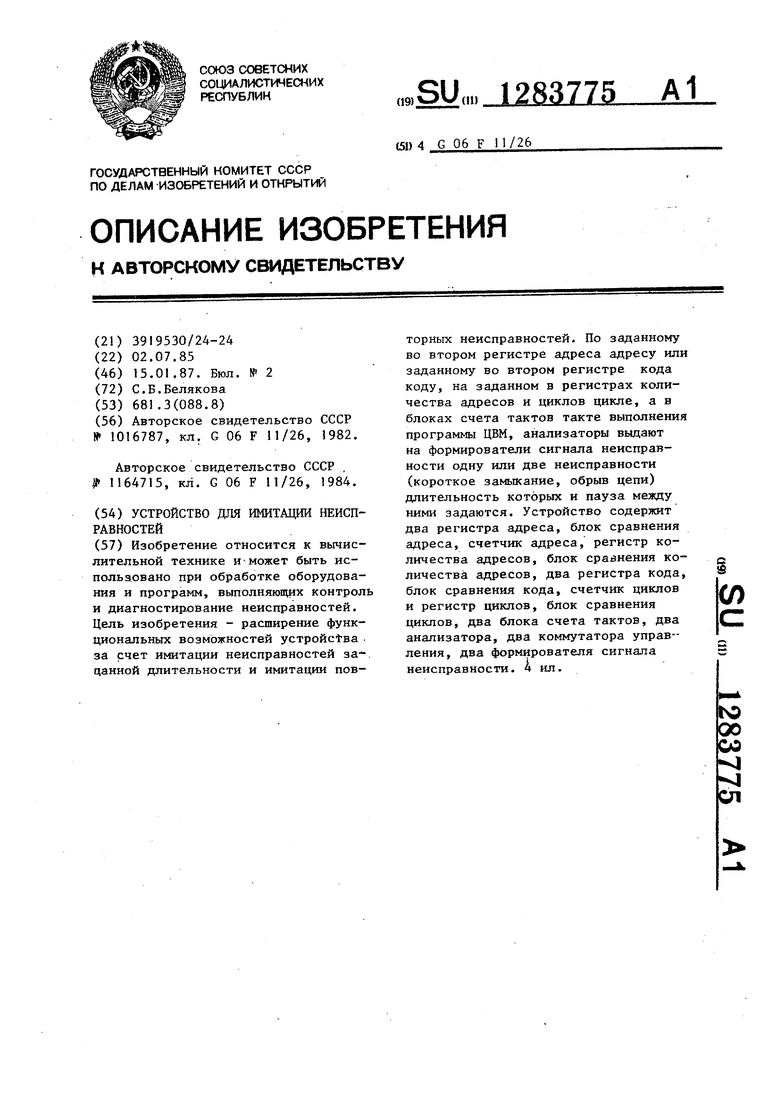

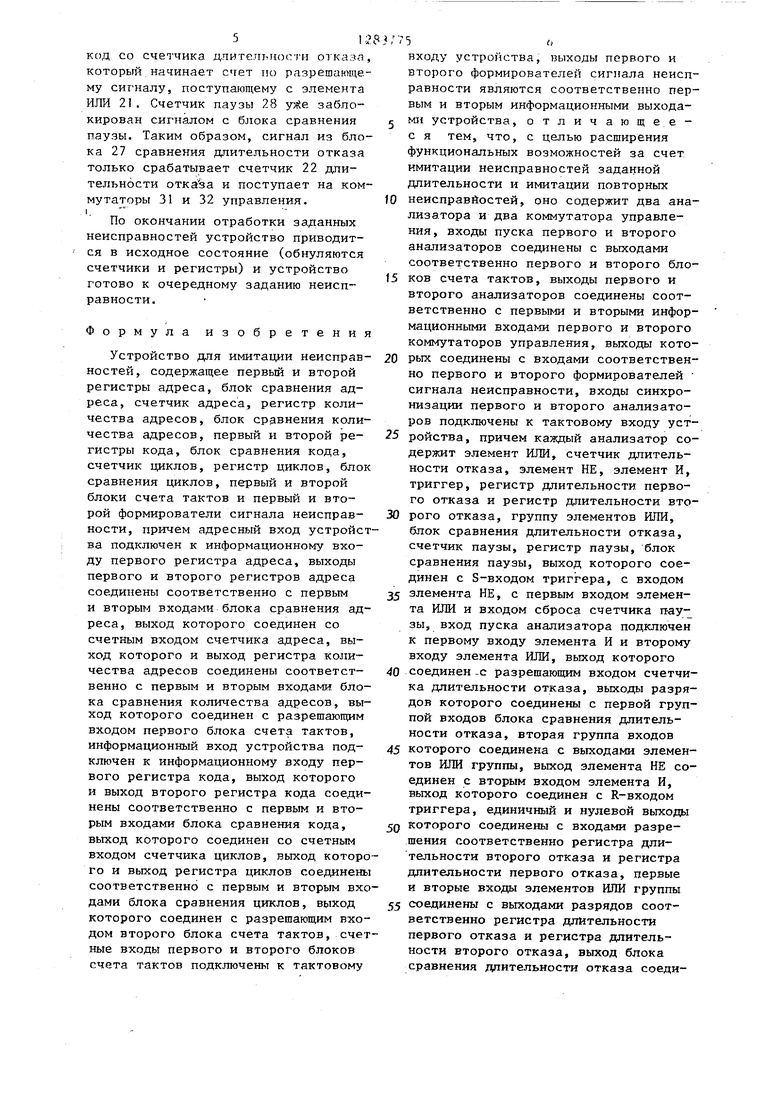

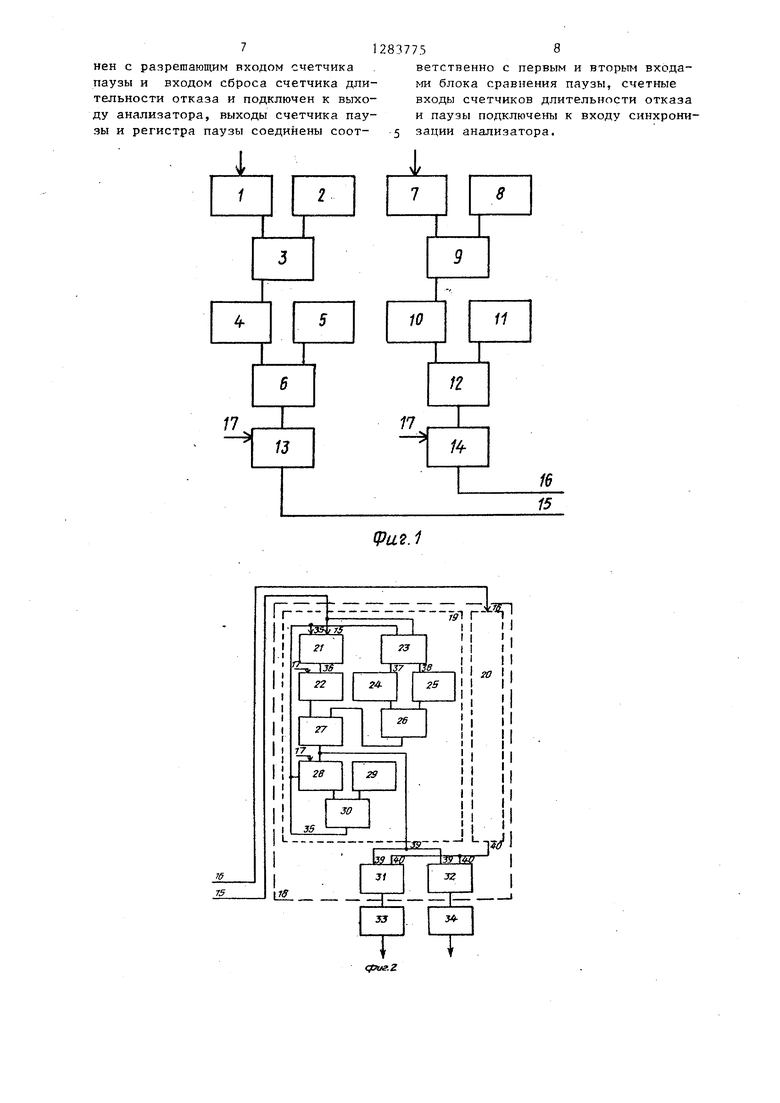

На фиг.1 и 2 изображена структурная схема предлагаемого устройства; на фиг.З - схема блока счета тактов, на фиг.4 - схема запрета.

Устройство содержит первый 1 и второй 2 регистры адреса, блок 3 сравнения адреса, счетчик 4 адреса и регистр 5 количества адресов, блок 6 сравнения количества адресов, первый 7 и второй 8 регистры кода, блок 9 сравнения кода, счетчик 10 циклов и регистр II циклов, блок 12 сравнения циклов, содержащий первый 13 и второй 14 блоки счета тактов, входы пуска первого 15 и второго 16 анализаторов , тактовый вход 17 устройства блок 18 управления, содержащий два анализатора 19 и 20, каждьй из которых содержит элемент ИЛИ 21, счетчик 22 длительности отказа, схему 23 запрета, два регистра 24 и 25 длитель- ;ности первого и второго отказов, группу элементов ИЛИ б, блок 27 сравнения длительности отказа, счетчик 28 паузы, регистр 29 паузы, блок 30 сравнения паузы. Блок управления также содержит первый 31 и второй 32 коммутаторы управления. Кроме того устройство содержит первый 33 и второй 34 формирователи сигнала неисправности.

На схеме устройства также обозначены выход 35 блока сравнения паузы, выход 36 элемента ИЛИ, первый 37 и второй 38 выходы схемы запрета 23, выходы 39 и 40 первого и второго анализаторов.

Каждый блок счета тактов содержит триггер 41, счетчик 42 тактов и ре- гистр 43 тактов, соединенные с блоком 44 сравнения тактов, элемент И 45.

Схема 23 запрета состоит из элементов НЕ 46, И 47, и триггера 48.

В качестве блоков 3, 6, 9, 12, 27, 30 и 44 сравнения используются поразрядные сумматоры по модулю два сигналов со счатчика и регистра (шш

5

7

0

5

0

0

752

двух счетчиков), причем выходы сумматоров объединяются схемой И, в качестве формирователей 33 и 34 - нормально замкнутые и нормально разомкнутые коммутаторы для имитации обрыва и короткого замыкания в качестве коммутаторов 31 и 32 управления - тумблеры для подключения к выходу 39 анализатора I9 или выходу 40 анализатора 20.

Устройство работает следующим образом.

При подготовке, устройства к работе группа входов первого регистра 1 адреса подключается к цепям передачи адреса команд, группа входов первого регистра 7 кода подключается к цепям передачи кодовых слов. Счетные входы счетчиков 42 в блоках 13 и 14 счета тактов и счетчиков 22 и 28 в блоке 18 управления подключены к входу 17 генератора тактовых импульсов. Выходы устройства подключены к выбранной точке схемы ЦВМ и к внешним связям ЦВМ, в которых необходимо имитировать неисправность. Коммутаторами 31 и 32 устанавливается нужная неисправность (цепь задания неисправности по совпадению адреса или цепь задания неисправности по совпадению кода).

В исходном состоянии первый регистр 1 адреса, счетчик 4 адреса, первый регистр 7 кода, счетчик 10 циклов, триггер 41, счетчик 42 тактов, счетчик 22 длительности отказа, счетчик 28 паузы обнулены, второй регистр 2 адреса, второй регистр 8 кода, регистр 5 количества адресов, регистр 11 циклов, регистр 43 тактов, регистр 24 длительности первого отказа, регистр 25 длительности второго отказа, регистр 29 паузы, первый . и второй 3 и 32 коммутаторы управления находятся в произвольном состоянии. Для внесения определенной неисправности - одиночной или повторной - в нужном такте и цикле выполнения команды или при передаче заданного кода, устанавливаются начальные условия: во втором регистре 2 адреса - адрес команды, в регистре 5 количества адресов - код количества повторений адреса, во втором регистре 8 кода - кодовое слово, в регистре 11 циклов - количество повторений кодового слова, в регистре 43 тактов - количество тактов, по исте- I

ченнн которых необходимо внести первую неисправность, н регистрах 2/-I и 25 длительности первого и второго отказов - количество тактов в течение которых длится отказ, в регистр 29 паузы - количество тактов между первым и повторными отказами; коммутаторы 31 и 32 управления подключают цепи формирования неисправности по совпадению адреса и по совпадению кода к первому или второму формирователю 33 и 34, имитирующим короткое замыкание или обрыв цепи. Начальные условия задаются тумблерами вручную перед началом работы. В ходе выполнения программы в определенный момент времени, когда в первый регистр I адреса записывается адрес равный адресу, записанному во втором регистре 2 адреса, на выходе блока 3 сравнения адреса появляется сигнал сравнения, который поступает на счетчик 4 адреса. Счетчик 4 адреса начинает считать адреса команд программы ЦВМ. В случае равенства количества адресов в счетчике 4 адреса и в регистре 5 количества адресов блок сравнения 6 выдает сигнал в первый блок 13 счета тактов. В то же время при

передаче кодовых слов по внешним I

связям ЦВМ в определенный момент времени (может быть одновременно с выходом на заданный адрес) кодовое слово в первом регистре 7 кода становится равным кодовому слову во втором регистре 8 кода, тогда блок 9 сравнения кода выдает сигнал сравнения, который поступает на счетчик 10 циклов. Счетчик 10 циклов начинает считать циклы передачи заданного кода. В случае равенства количества циклов в счетчике 10 циклов и в регистре 11 циклов блок 12 сравнения.циклов выдает сигнал во второй блок 14 счета тактов. Под действием сигналов с блока 6 сравнения количества адресов и с блока 12 сравнения циклов триггер 41 любого блока счета тактов 13 и 14 переходит в единичное состояние, при

этом снимается сигнал с входа обнуления счетчика 42 тактов и счетчик начинает считать импульсы тактовой частоты, поступающие на его счетный вход. В момент сравнения содержимого счетчика 42 тактов с содержимым ре- .гистра 43 тактов на выходе блока 44 сравнения тактов появляется сигнал, при совпадении которого с сигналом

25

.775

на единичном выходе триггера il формируется сигнал на вь(ходе элемента И 45, который поступает на запрещающий вход счетчика 42 тактов и на блок .5 8 управления. Сигнал, поступающий из блоков 13 и 14 счета тактов на анализаторы 19 и 20, проходит через элемент ИЛИ 21 и поступает на разре- шакщий вход счетчика 22 длительности О отказа. Счетчик 22 начинает считать импульсы тактовой частоты, поступающие на счетный вход. Код с регистра 24 длительности первого отказа по разрешению схемы 23 запрета поступа- 15 ет на.группу элементов ИЛИ 26, туда же поступает код с регистра 25 длительности второго отказ а. Коды со счетчика 22 длительности отказа и с группы элементов ИЛИ 26 поступают на 20 блок 27 сравнения длительности отказа. При совпадении кодов па выходе блока 27 сравнения длительности отказа появляется сигнал, который сбрасывает счетчик длительности отказа 22, разрешает счет тактовых импульсов счетчику паузы 28 и поступает на коммутаторы 31 и 32 управления, откуда поступает на формирователи 33 и 34 сигнала неисправности 33 и 34, имитирую- щие короткое замыкание и обрыв цепи. В это время счетчик 28 паузы выдает коды в блок 30 сравнения паузы, где они сравниваются с кодом, поступающим с регистра паузы 29, при их сов- 35 падении выдается сигнал, который

сбрасывает счетчик паузы и запрещает ему дальнейший счет импульсов; этот же сигнал поступает на элемент ИЛИ 21 и на схему 23 запрета. Элемент 0 ИЛИ 21 пропускает либо сигнал 15, поступающий с первого блока счета тактов (для схемы 19; в схеме 20 - . сигнал 16, поступающий со второго блока счета тактов), либо сигнал 35, 5 поступающий с блока 30 сравнения паузы. Схема 23 запрета блокирует выдачу кода с регистра 25 длительности второго отказа при отсутствии сигнала с блока 30 сравнения паузы 6 н с регистра 24 длительности первого отказа при наличии сигнала 35 с блока 30 сравнения паузы. При поступлении сигнала с блока 30 сравнения паузы на схему 23 запрета ре- 5 гистр 25 длительности второго отказа вьщает код, который через группу элементов ИЛИ 26 поступает в блок 27 сравнения длительности отказа, на второй вход которого поступает

512

код со счетчика, длительности отказа, который.начинает счет по разрешающему сигналу, поступающему с элемента ИЛИ 21. Счетчик паузы 28 узйе заблокирован сигналом с блока сравнения паузы. Таким образом, сигнал из блока 27 сравнения длительности отказа только срабатывает счетчик 22 дпи- тельности oTKai sa и поступает на коммутаторы 31 и 32 управления. I

По окончании отработки заданных

неисправностей устройство приводится в исходное состояние (обнуляются счетчики и регистры) и устройство готово к очередному заданию неисправности.

Формула изобретения

Устройство для имитации неисправностей, содержащее первьй и второй регистры адреса, блок сравнения адреса, счетчик адреса, регистр количества адресов, блок сравнения количества адресов, первый и второй регистры кода, блок сравнения кода, счетчик циклов, регистр циклов, блок сравнения циклов, первый и второй блоки счета тактов и первый и второй формирователи сигнала неисправности, причем адресный вход устройства подключен к информационному входу первого регистра адреса, выходы первого и второго регистров адреса соединены соответственно с первым и вторым входами блока сравнения адреса, выход которого соединен со счетным входом счетчика адреса, выход которого и выход регистра количества адресов соединены соответственно с первым и вторым входами блока сравнения количества адресов, выход которого соединен с разрешающим входом первого блока счета тактов, информационный вход устройства подключен к информационному входу первого регистра кода, выход которого и выход второго регистра кода соединены соответственно с первым и вторым входами блока сравнения кода, выход которого соединен со счетным входом счетчика циклов, выход которого и выход регистра циклов соединены соответственно с первым и вторым входами блока сравнения циклов, выход которого соединен с разрешающим входом второго блока счета тактов, счетные входы первого и второго блоков счета тактов подключены к тактовому

/ 7 5{,

входу устройства, выходы первого и второго формирователей сигнала неисправности являются соответственно первым и вторым информационными выхода- ми устройства, отличающее- с я тем, что, с целью расширения функциональных возможностей за счет имитации неисправностей заданной длительности и имитации повторных o неисправйостей, оно содержит два анализатора и два коммутатора управления , входы пуска первого и второго анализаторов соединены с выходами соответственно первого и второго бло- 5 ков счета тактов, выходы первого и второго анализаторов соединены соответственно с первыми и вторыми информационными входами первого и второго коммутаторов управления, выходы кото- 0 рых соединены с входами соответственно первого и второго формирователей сигнала неисправности, входы синхронизации первого и второго анализаторов подключены к тактовому входу уст- 5 ройства, причем каждый анализатор содержит элемент ИЛИ, счетчик длительности отказа, элемент НЕ, элемент И, триггер, регистр длительности первого отказа и регистр длительности вто- 30 рого отказа, группу элементов ИЛИ, блок сравнения длительности отказа, счетчик паузы, регистр паузы, блок сравнения паузы, выход которого соединен с S-входом триггера, с входом 35 элемента НЕ, с первым входом элемента ИЛИ и входом сброса счетчика пау- зы, вход пуска анализатора подключен к первому входу элемента И и второму входу элемента ИЛИ, выход которого 40 соединен-С разрешающим входом счетчика длительности отказа, выходы разрядов которого соединены с первой группой входов блока сравнения длительности отказа, вторая группа входов 45 которого соединена с выходами элементов ИЛИ группы, выход элемента НЕ соединен с вторым входом элемента И, выход которого соединен с R-входом триггера, единичный и нулевой выходы 50 которого соединены с входами разрешения соответственно регистра длительности второго отказа и регистра дпительности первого отказа, первые и вторые входы элементов ИЛИ группы 55 соединены с вьгходамя разрядов соответственно регистра длительности первого отказа и регистра длительности второго отказа, выход блока сравнения дпительности отказа соединен с разрешающим входом счетчика паузы и входом сброса счетчика длительности отказа и подключен к выходу анализатора, выходы счетчика паузы и регистра паузы соединены соот12837758

ветственно с первым и вторым входами блока сравнения паузы, счетные входы счетчиков длительности отказа и паузы подключены к входу синхронизации анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1984 |

|

SU1164715A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536387A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

| Устройство для имитации неисправностей | 1985 |

|

SU1273933A1 |

| Тренажер оператора вычислитель-НыХ уСТРОйСТВ | 1979 |

|

SU798956A1 |

| Устройство для имитации сбоев и неисправностей цифровой вычислительной машины | 1985 |

|

SU1265779A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для имитации отказов дискретной аппаратуры | 1987 |

|

SU1451702A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для имитации отказов дискретной аппаратуры | 1990 |

|

SU1815642A1 |

Изобретение относится к вычислительной технике и может быть использовано при обработке оборудования и программ, выполняющих контроль и диагностир-ование неисправностей. Цель изобретения - расширение функциональных возможностей ycTpoActBa за счет имитации неисправностей за-, цанной длительности и имитации повторных неисправностей. По заданному во втором регистре адреса адресу или заданному во втором регистре кода коду, на заданном в регистрах количества адресов и циклов цикле, а в блоках счета тактов такте выполнения программы ЦВМ, анализаторы выдают на формирователи сигнала неисправности одну или две неисправности (короткое замыкание, обрыв цепи) длительность которых и пауза между ними задаются. Устройство содержит два регистра адреса, блок сравнения адреса, счетчик адреса, регистр количества адресов, блок сравнения количества адресов, два регистра кода, блок сравнения кода, счетчик циклов и регистр циклов, блок сравнения циклов, два блока счета тактов, два анализатора, два коммутатора управления, два формирователя сигнала неисправности. 4 ил. сл ts3 СХ) со ел

(ра2.1

Г

. , Ф . .

фцг.4Составитель Д.Ванюхин Редактор Л.Пчолинская Техред Л.ОлеЙник

Заказ 74АЗ/48

Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производствеипо-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

U2.3

Корректор Н.Король

| Устройство для имитации неисправностей цифровой вычислительной машины | 1982 |

|

SU1016787A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для имитации неисправностей | 1984 |

|

SU1164715A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-07-02—Подача