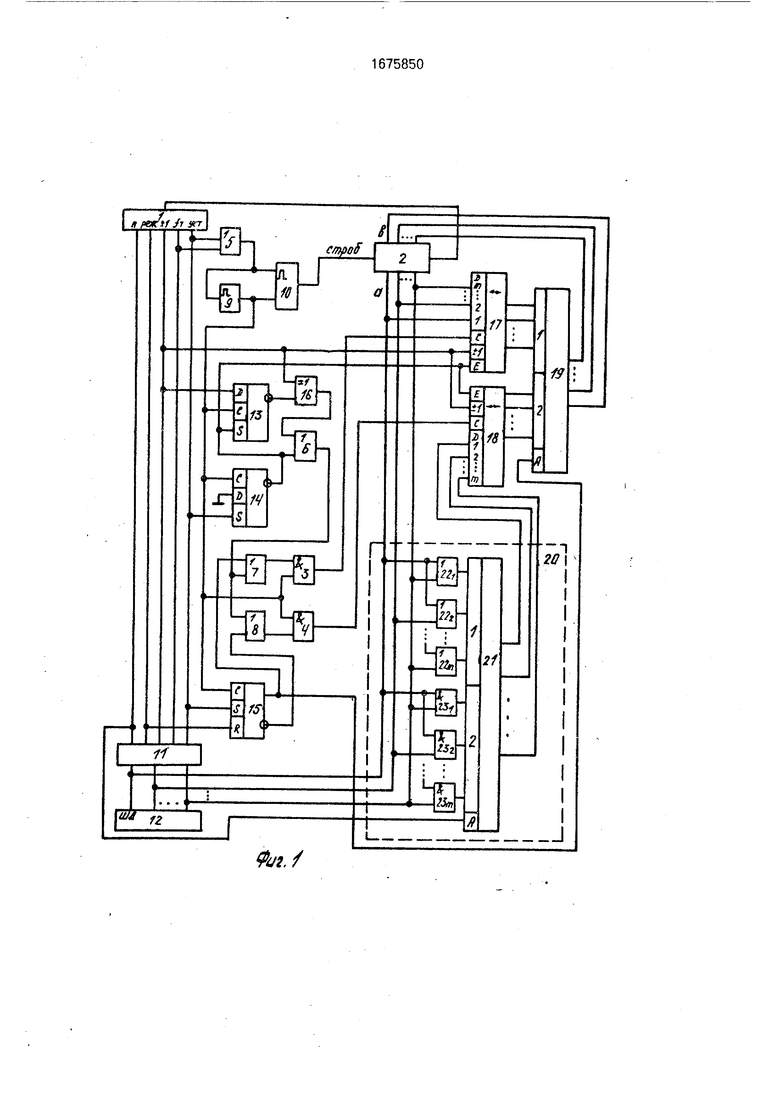

ЩЕЕ ИЛИ 16, первый 17 и второй 18 реверсивные сдвиговые регистры, мультиплексор 19 и логический коммутатор 20.

Логический коммутатор 20 включает в себя селектор-мультиплексор 21, элементы ИЛИ 22i-22m по числу выходов коммутатора 11 фаз и элементы 2И 23ч-23т по числу выходов коммутаторов 11 фаз.

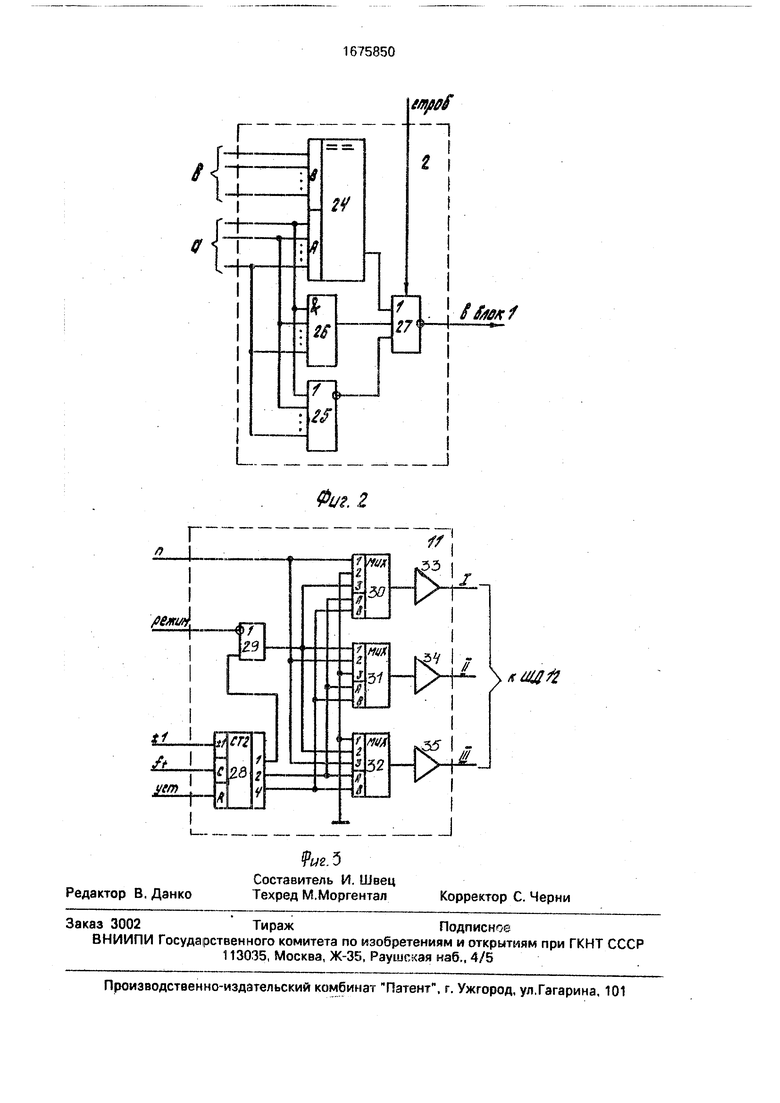

Блок 2 задания режима (фиг. 2) содержит элемент 24 сравнения кодов, элемент ИЛИ-НЕ 25 и элемент И 26, число входов у каждого из которых равно числу выходов коммутатора 11 фаз, элемент ЗИЛИ-НЕ 27 со стробированием.

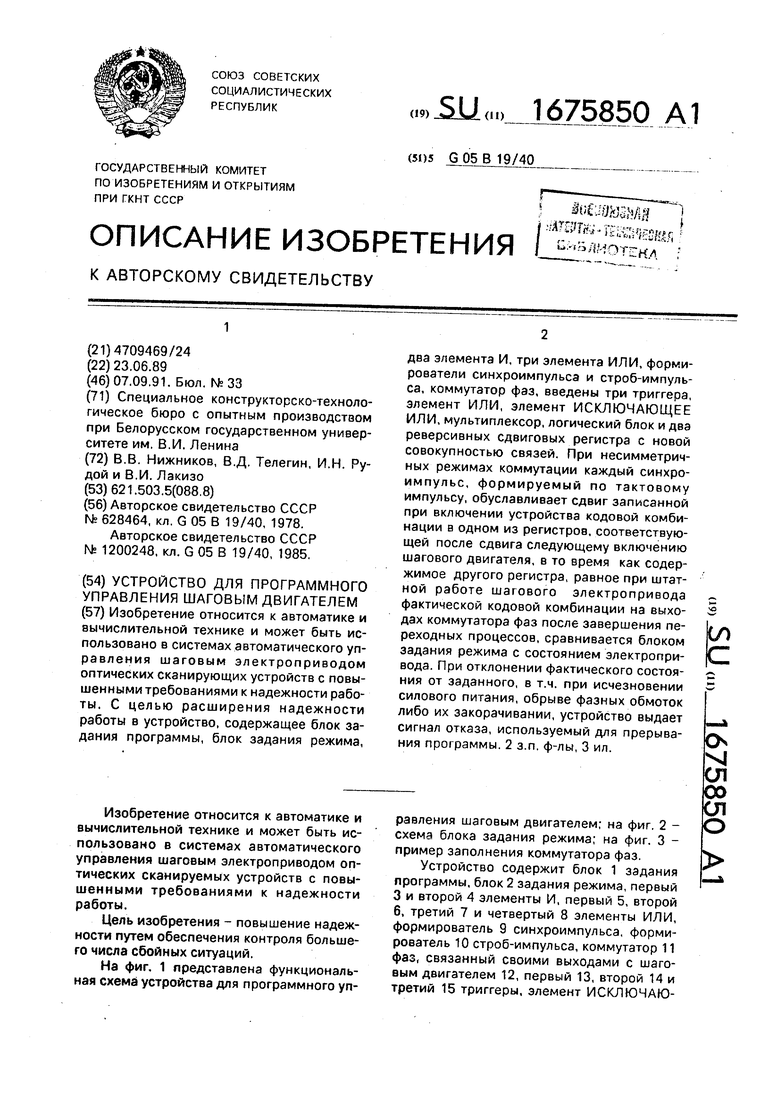

Коммутатор фаз (фиг. 3) содержит реверсивный счетчик 28, элемент ИЛИ-НЕ 29, мультиплексоры 30-32, усилители 33-35.

Устройство работает следующим образом.

При включении устройства на установочном выходе блока 1 задания программ устанавливается сигнал низкого уровня, действующей в течение определенного (10 мкс - 1 мс) промежутка времени сигнал начальной установки) и обуславливающий на это время блокировку коммутатора 11 фаз с обесточиванием обмоток шагового двигателя 12. Поступая далее через элемент ИЛИ 5, работающий в инверсной логике, на первый вход формирователя 10 строб-импульса, сигнал низкого уровня обуславливает появление на выходе формирователя 10 строб-импульса сигнала низкого уровня, который блокирует работу блока 2, обуславливая при этом на его выходе сигнал высокого уровня, являющийся сигналом отсутствия сбоя и разрешающий работу блока 1 задания программы в штатном режиме. Формирователь 10 строб-импульса может быть выполнен, например, на базе триггера, вход установки в нулевое состояние которого подключен к выходу первого элемента ИЛИ 5, вход установки в единичное состояние через элемент задержки связан с выходом формирователя 9 синхроимпульса, а инверсный выход соединен с входом стробирования блока 2.

При задании, к примеру, несимметричного режима коммутации с включением раз- ного количества обмоток шагового двигателя в соседних тактах на выходе для задания режима коммутации блока 1 устанавливается сигнал высокого уровня, и сигнал начальной установки в данном слу- , чае устанавливает третий триггер 15 в единичное состояние. В единичное состояние этим же сигналом устанавливается и триггер 14, обуславливая в свою очередь сигналом низкого уровня с инверсного выхода

установку триггера 13 в единичное состояние. Одновременно сигнал низкого уровня с инверсного выхода триггера 14 подается и на вход элемента ИЛИ 6, обеспечивающего

сложение сигналов низкого уровня. Тем самым с выхода элемента 6 на входы работающих в инверсной логике элементов ИЛИ 7 и 8 поступает сигнал низкого уровня, и независимо от состояния триггера 15 на вхо0 дах элементов И 3 и 4 поддерживается разрешающий сигнал низкого уровня.

По окончании сигнала начальной установки на установочном выходе блока 1 задания программы появляется сигнал высокого

5 уровня, который обуславливает установку коммутатора 11 фаз в исходное состояние, определяемое уро внями потенциальных сигналов на входах коммутатора 11 для задания режима коммутации и количества аоз0 бужденных фаз. При задании, к примеру, минимального количества возбужденных фаз в исходном состоянии в случае несимметричного режима коммутации на вход задания количества возбужденных фаз из

5 блока 1 задания программы подается сигнал низкого уровня (при сигнале высокого уровня на входе для задания режима коммутации). При установке коммутатора 11 фаз в исходное состояние на соответствующих

0 выходах коммутатора появляются сигналы высокого уровня, обуславливающие записывание определенных обмоток шагового двигателя 12.

По перепаду сигнала из О в 1 на

5 установочном выходе блока 1 задания программы и тем самым на выходе элемента ИЛИ 5 запускается формирователь 9 синхроимпульса, вырабатывающий отрицательный импульс, который проходит через

0 открытые элементы И 3, 4 и подается на входы сдвига реверсивных сдвиговых регистров 17 и 18. На входах записи (Е) этих регистров присутствует сигнал низкого уровня, снимаемый с инверсного выхода

5 триггера 14 и являющийся сигналом разрешения параллельной записи информации в регистры, выполняемый по окончании синхроимпульса, т.е. по его переходу из О в 1. В реверсивный сдвиговый регистр 17 при этом записывается кодовая комбинация, присутствующая на выходах коммутатора 11 фаз и соответствующая минимальному количеству возбужденных фаз (например, 100...0) шагового двигателя. Записываемая к реверсивный сдвиговый регистр 18 кодовая комбинация снимается при нулевом состоянии адресно0 го входа селектора-мультиплексора 21с выходов группы элементов ИЛИ 22i-22m и содержит благодаря их кольцевому включению (при работе в положительной логике) на одну логическую единицу больше в сравнении с кодовой комбинацией на выходе коммутатора 11 фаз, соответствуя включению обмоток шагового двигателя 12 в еле- дующем такге коммутации например, 110...0) при движении в прямом направлении, задаваемом высоким уровнем сигнала на выходе направления блока 1 задания программы.

Одновременно с записью информации в реверсивные сдвиговые регистры 17 и 18 триггер 15 по перепаду синхроимпульса из О в 1 переключается в нулевое состояние, обеспечивая сигнал низкого уровня на адресном входе мультиплексора 19 и прохождение кодовой комбинации, записанной в реверсивный сдвиговый регистр 17, через мультиплексор 19 на информационные входы b блока 2.Перепадом синхро- импульса из О в 1 в триггер 14 записывается сигнал низкого уровня с его информационного входа,

На инверсном выходе этого триггера с некоторой временной задержкой, обусяов- ленной записью информации, появляется сигнал высокого уровня, который переводит реверсивные сдвиговые регистры 17 и 18 а режим сдвига записанной информации и деблокирует триггер 13, на инверсном вы- ходе которого благодаря задержке на триггере 14 продолжает сохраняться сигнал низкого уровня. При задании, к примеру, движения в прямом направлении (высокий уровень сигнала на выходе на- правления блока 1) с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 на вход элемента ИЛИ 6 подается сигнал высокого уровня. На первом входе этого элемента присутствует сигнал также высокого уровня и тем самым на первые входы элементов ИЛИ 7 и 8 подается сигнал высокого уровня, что при нулевом состоянии триггера 15 обуславливает сохранение разрешающего сигнала низкого уровня на входе элемента И 3, в то время как элемент И 4 блокируется сигналом высокого уровня с выхода элемента ИЛИ 8.

После окончания синхроимпульса на выходе формирователя 10 строб-импульса с некоторой временной задержкой, необходимой для завершения переходных процессов в реверсивных сдвиговых регистрах 17 и 18 и мультиплексоре 19, появляется сигнал высокого уровня, деблокирующий блок 2. На первые информационные входы а этого блока подана кодовая комбинация с выходов коммутатора 11 фаз, а на вторые информационные входы b i поступает информация с выходов мультиплексора 19,

записанная в реверсивном сдвиговом регистре 17. При равенстве обеих кодовых комбинаций на выходе элемента 24 сравнения кодов, входящего в состав блока 2 (фиг. 2), присутствует сигнал низкого уровня. При первоначальной запитке шагового двигателя и наличии хотя бы одной включенной и хотя бы одной обесточенной обмоток с выходов элементов ИЛИ- НЕ 25 и И 26 также снимаются сигналы низкого уровня и тем самым при штатном включении1 шагового электропривода на выходе блока 2 после снятия строба присутствует сигнал высокого уровня, разрешающий дальнейшую работу блока 1 задания программы в установленном режиме.

При выдаче на тактовый выход блока 1 задания программы отрицательного тактового импульса этот импульс проходит через первый элемент ИЛИ 5 и поступает на вход формирователя 10 строб-импульса, на выходе которого при этом появляется сигнал низкого уровня, запирающий блок 2. По окончании тактового импульса, т.е. по его переходу из О в 1, на выходах коммутатора 11 фаз формируется кодовая комбинация, сдвинутая на один шаг в прямом направлении (110...0) и обуславливающая соответствующее переключение обмоток шагового двигателя 12. Одновременно по тому же переходу тактового импульса запускается формирователь 9 синхроимпульса и отрицательный импульс с его выхода проходит через открытый элемент И 3 на вход сдвига реверсивного сдвигового регистра 17, обуславливая в дальнейшем своим переходом из О и 1 сдвиг записанной в этом регистре информации на один шаг в прямом направлении и появление на его выходах кодовой комбинации (010...0), соответствующей следующему (по второму тактовому импульсу) включению обмоток шагового двигателя. Одновременно перепадом синхроимпульса из О в 1 подтверждается состояние триггера 13 (при отсутствии сигнала реверса) и триггера 14, в то время как триггер 15 переключается перепадом синхроимпульса в единичное состояние, открывая элемент И 4, а также обеспечивая прохождение на информационные входы блока 2 кодовой комбинации с выходов реверсивного сдвигового регистра 18, в котором записана информация (110...0), совпадающая с кодовой комбинацией на выходах коммутатора 11 фаз при штатной отработке шага,

После окончания синхроимпульса и снятия с соответствующей задержкой строба на выходах блока 2 продолжает сохраняться сигнал высокого уровня, подтверждающий

после завершения переходных процессов отсутствие отказа либо сбойной ситуации. При выдаче нового тактового импульса описанный цикл повторяется с той лишь разницей, что отрицательный синхроим- пульс с выхода формирователя 9 поступает через элемент И 4 на вход сдвига регистра 18, обуславливая своим переходом из О в 1 сдвиг записанных в этом регистре данных и появление кодовой комбинации (0110...0) на его выходах, в то время как на вторые входы блока 2 поступает кодовая комбинация (010...0) с выходов регистра 17, соответствующая информации на первых входах блока 2 при штатной работе электро- привода. Синхроимпульс с выхода формирователя 9 переключает далее триггер 15 в нулевое состояние, обеспечивая прохождение следующего синхроимпульса через элемент И 3. Тем самым каждый тактовый импульс при несимметричных режимах коммутации обуславливает сдвиг кодовой комбинации в одном из регистров (т.е. формирование следующей заданной кодовой комбинации) и сравнение содержимо- го второго из регистров, равного при штатной работе шагового электропривода фактическому состоянию последнего после прохождения тактового импульса и завершения переходных процессов.

При изменении направления движения путем выдачи сигнала низкого уровня на выход направления блока 1 задания программы равно как и при задании движения в обратном направлении при первоначаль- ном включении устройства, на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подаются сигналы одинакового (низкого) уровня, и сигнап низкого уровня с выхода этого элемента, поступая через элементы ИЛИ 6-8 на входы элементов И 3 и 7, разрешает прохождение синхроимпульса с выхода формирователя 9 через оба элемента И 3 и 4 на входы сдвига обоих регистров 17 и 18 и синхронный сдвиг записанных в этих ре- (истрах данных в обратном направлении, после чего на сравнение выдается содержимое одного из регистров, равное при отсутствии сбоев в работе кодовой комбинации на выходах коммутатора 11 фаз, сдвинутой соответственно тактовым импульсом (или перепадом из О в 1 по окончании сигнала начальной установки) в обратном направлении.

Если при несимметричном режиме ком- мутации количество возбужденных фаз шагового двигателя 12 в исходном состоянии задается максимальным (к примеру, 110,,.0) путем выдачи сигнала высокого уровня на выход для задания количества

возбужденных фаз блока 1, то данная комбинация будет присутствовать на выходах коммутатора 11 фаз и запишется в реверсивный свдиговый регистр 17 после установки шагового электропривода в исходное состояние, в то время как записываемая в реверсивный сдвиговый регистр 18 кодовая комбинация снимается (при высоком уровне сигнала на адресном входе селектора-мультиплексора 21) с выходов группы элементов И и содержит благодаря кольцевому включению этих работающих в положительной логике элементов на одну логическую единицу меньше в сравнении с кодовой комбинацией на выходе коммутатора 11 фаз, соответствуя включению обмоток шагового двигателя 12 в следующем такте коммутации (010...0) при движении в прямом направлении. После записи информации и установки триггера 14 а нулевом состоянии устройство работает, в т.ч. и при обработке реверса, аналогично описанному.

В случае выбора симметричного режима коммутации путем выдачи сигнала низкого уровня на выход для задания режима коммутации блока 1 триггер 15 фиксируется в нулевом состоянии и не реагирует в дальнейшем на поступающие синхроимпульсы, обуславливая сравнение содержимого только реверсивного сдвигового регистра 17 с данными на первых информационных входах блока 2, так как на адресном входе мультиплексора 19 в этом случае постоянно поддерживается сигнал низкого уровня. На вход сдвига первого регистра 17 при этом поступает каждый синхроимпульс через постоянно открытый первый элемент И 3, в то время как коммутатор 11 фаз формирует при поступлении тактовых импульсов последовательность кодовых комбинаций, соответствующую симметричному режиму (к примеру, 110 ...О, 0110...О и т.д.).

Обеспечивая сравнение фактического состояния шагового электропривода с заданным режимом работы по таким основным параметрам, как количество включаемых в каждом также фазных обмоток, их сдвиг по каждому такту, изменение количества фазных обмоток при несимметричных режимах коммутации, а также отслеживание изменений направления движения и, при необходимости, корректный сдвиг, в т.ч. с учетом переходных про- цессов, устройство выдает сигнал отказа при любом отклонении фактического состояния от заданного режима работы после завершения переходных процессов и снятия строба. Поступая с выхода задания

режима блока на блок задания программы, сигнал отказа обуславливает прерывание выполняемой программы и может быть дополнительно использован для аварийной сигнализации, блокировки управляемого объекта и т.д.

Сигнал отказа выдается устройством и при исчезновении силового питания после включения шагового электропривода, обрыве всех фазных обмоток либо закорачивании всех обмоток на шину питания, в т.ч. и при нештатном обесточивании обмоток во время стоянки (не путем выдачи, сигнала низкого уровня на установочный выход блока 1 задания программы). Во всех этих случаях на выходе элемента ИЛИ-НЕ 25 либо элемента И 26 в зависимости от вида сбойной ситуации появляется сигнал высокого уровня, обуславливающий после снятия строба сигнал низкого уровня на выходе элемента ИЛИ-НЕ 27 со стробированием (фиг. 2), т.е. сигнал отказа, превышающий выполнение текущей программы.

Таким образом, предложенное устройство для программного управления шаговым двигателем обладает, в сравнении с известным, более высокой надежностью, обеспечивая в процессе отработки заданной программы пошаговый контроль последовательности переключения фазных обмоток шагового двигателя, количества включаемых по каждому такту обмоток и их сдвиг, изменения количества включаемых обмоток при несимметричных режимах коммутации. При любом отклонении от заданного режима работы, в т.ч. при обрывах либо коротких замыканиях фазных обмоток, устройство оперативно выдает сигнал отказа, который может быть использован для прерывания программы, блокировки объекта и аварийной сигнализации практически сразу после возникновения сбойной ситуации.

Формула изобретения 1. Устройство для программного управления шаговым двигателем, содержащее блок задания программы, блок задания режима, первый и второй элементы И, первый, второй и третий элементы ИЛИ, формирователь синхроимпульса, формирователь строб-импульса и коммутатор фаз, группа информационных выходов которого подключена к шаговому двигателю, а тактовый вход направления счета и установочный вход соединены с соответствующими выходами блока задания программы, вход которого связан с выходом блока задания режима, отличающееся тем, что, с целью повышения надежности путем обеспечения контроля большего числа сбойных ситуаций, в него введены первый, второй и третий триггеры, четвертый элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. первый и

второй реверсивные сдвиговые регистры, мультиплексор и логический коммутатор, входы для задания количества возбужденных фаз и режима коммутации коммутатора фаз подключены к соответствующим

0 выходам задания блока задания программы, установочный и тактовый выходы которого соединены с первым и вторым входами первого элемента ИЛИ, выход, которого подключен к первому входу формировате5 ля строб-импульса и к входу формирователя синхроимпульса, выход которого соединен с первыми входами первого и второго элементов И. с тактовыми входами триггеров и с вторым входом формиро0 вателя строб-импульса, соединенного выходом с входом стробирования блока задания режима, первая группа информационных входов которого подключена к выходам коммутатора фаз и к группе ин5 формационных входов первого реверсивного сдвигового регистра и логического коммутатора, адресный вход которого объединен с входом коммутатора фаз для задания количества возбужденных фаз, а

0 выходы соединены с группой информационных входов второго реверсивного сдвигового регистра, вход реверса которого объединен с входом направления коммутатора фаз, с информационным входом перво5 го триггера, с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с входом реверса первого реверсивного сдвигового регистра, разрядные выходы которого соединены с первой группой информационных входов

0 мультиплексора, вторая группа информационных входов которого соединена с разрядными выходами второго реверсивного сдвигового регистра, выходы подключены к второй группе информационных входов

5 блока задания режима, а адресный вход подключен к прямому выходу третьего триггера, вход установки в нулевое состояние которого соединен с входом для задания режима коммутации фаз. вход установки в

0 единичное состояние соединен с установочным входом коммутатора фаз и с входом установки в единичное состояние второго триггера, информационный вход которого подключен к общей шине, а вы5 ход соединен с первым входом второго элемента ИЛИ и с входом установки в единичное состояние первого триггера, выход которого соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подключенного выходом к второму входу второго

элемента ИЛИ, выход которого соединен с первыми входами третьего и четвертого элементов ИЛИ, вторые входы которых связаны соответственно с прямым и инверсным выходами третьего триггера, а выходы подключены к вторым входам первого и второго элементов И, выходы которых соединены с входами сдвига соответственно первого и второго реверсивных сдвиговых регистров, входы записи которых подключены к выходу второго триггера.

2. Устройство по п. 1,отличающее- с я тем, что логический коммутатор содержит селектор-мультиплексор, элементы ИЛИ по числу выходов коммутатора фаз и элементы И по числу выходов коммутатора фаз, первые входы первого элемента ИЛИ и первого элемента И подключены к первым входам второго элемента ИЛИ и элемента И, а также к соответствующему входу из группы информационных входов логического коммутатора, вторые входы второго элемента ИЛИ и второго элемента И подключены к второму входу из группы информационных входов логического коммутатора, вторые входы второго элемента ИЛИ и второго элемента И подключены к второму входу из группы информационных входов логического коммутатора, к первым входам третьих элементов ИЛИ и И, вторые входы последних элементов ИЛИ и И соединены с последним входом группы информационных входов логического коммутатора, с вторыми входами первых элементов ИЛИ и И, выходы всех элементов ИЛИ подключены к первой группе информационных входов

селектора-мультиплексора, вторая группа информационных входов которого соединена с выходами элементов И, адресный вход соединен с соответствующим входом логического коммутатора, выходы селекторамультиплексора подключены к группе информационных выходов логического коммутатора.

3. Устройство поп. отличающееся тем, что блок задания режима содержит элемент сравнения кодов, элемент ИЛИ-НЕ и элемент И, число входов у каждого из которых разно числу выходов коммутатора фаз, элемент ЗИЛИ-НЕ со стробированием, выход которого подключен к выходу блока задания режима, вход стробирования которого соединен с соответствующим входом элемента ЗИЛИ-НЕ со стробированием, группа входов соединена с выходами элементов ИЛИ-НЕ,

И и выходом элемента сравнения кодов, первая группа входов которого объединена с соответствующими входами элементов И, ИЛИ-НЕ и подключена к первой группе информационных входов, а вторая

группа входов соединена с второй группой информационных входов блока задания режима,

$/./

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Электропривод с устройством обнаружения отказов | 1990 |

|

SU1781811A1 |

| Устройство для обнаружения отказов в шаговом электроприводе | 1989 |

|

SU1640811A1 |

| Устройство для обнаружения отказов в шаговом электроприводе | 1988 |

|

SU1511843A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОТКАЗОВ В ШАГОВОМ ЭЛЕКТРОПРИВОДЕ | 1991 |

|

RU2032265C1 |

| Устройство для управления @ -фазным шаговым двигателем | 1987 |

|

SU1473066A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Распределитель импульсов для управления четырехфазным шаговым двигателем | 1987 |

|

SU1474822A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Устройство для обмена информацией | 1983 |

|

SU1198530A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматического уп- равления шаговым электроприводом оптических сканирующих устройств с повышенными требованиями к надежности работы. С целью расширения надежности работы в устройство, содержащее блок задания программы, блок задания режима, Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматического управления шаговым электроприводом оптических сканируемых устройств с повышенными требованиями к надежности работы. Цель изобретения - повышение надежности путем обеспечения контроля большего числа сбойных ситуаций. На фиг. 1 представлена функциональная схема устройства для программного упдва элемента И, три элемента ИЛИ, формирователи синхроимпульса и строб-импульса, коммутатор фаз, введены три триггера, элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, мультиплексор, логический блок и два реверсивных сдвиговых регистра с новой совокупностью связей. При несимметричных режимах коммутации каждый синхроимпульс, формируемый по тактовому импульсу, обуславливает сдвиг записанной при включении устройства кодовой комбинации в одном из регистров, соответствующей после сдвига следующему включению шагового двигателя, в то время как содержимое другого регистра, равное при штатной работе шагового электропривода фактической кодовой комбинации на выходах коммутатора фаз после завершения переходных процессов, сравнивается блоком задания режима с состоянием электропривода. При отклонении фактического состояния от заданного, в т.ч. при исчезновении силового питания, обрыве фазных обмоток либо их закорачивании, устройство выдает сигнал отказа, используемый для прерывания программы. 2 з.п. ф-лы, 3 ил. равления шаговым двигателем; на фиг. 2 - схема блока задания режима; на фиг. 3 - пример заполнения коммутатора фаз. Устройство содержит блок 1 задания программы, блок 2 задания режима, первый 3 и второй 4 элементы И, первый 5, второй 6, третий 7 и четвертый 8 элементы ИЛИ, формирователь 9 синхроимпульса, формирователь 10 строб-импульса, коммутатор 11 фаз, связанный своими выходами с шаговым двигателем 12, первый 13, второй 14 и третий 15 триггеры, элемент ИСКЛЮЧАЮСО с Os VJ ел 00 ел о

/

KUtf%

| Устройство для управления шаговым двигателем | 1974 |

|

SU628464A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для программного управления шаговым двигателем | 1984 |

|

SU1200248A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-09-07—Публикация

1989-06-23—Подача