Изобретение относится к вычислительной технике, а именно к преобразователям информации, и может быть использовано для построения кодирующих устройств.

Целью изобретения является повышение точности и быстродействия шифратора.

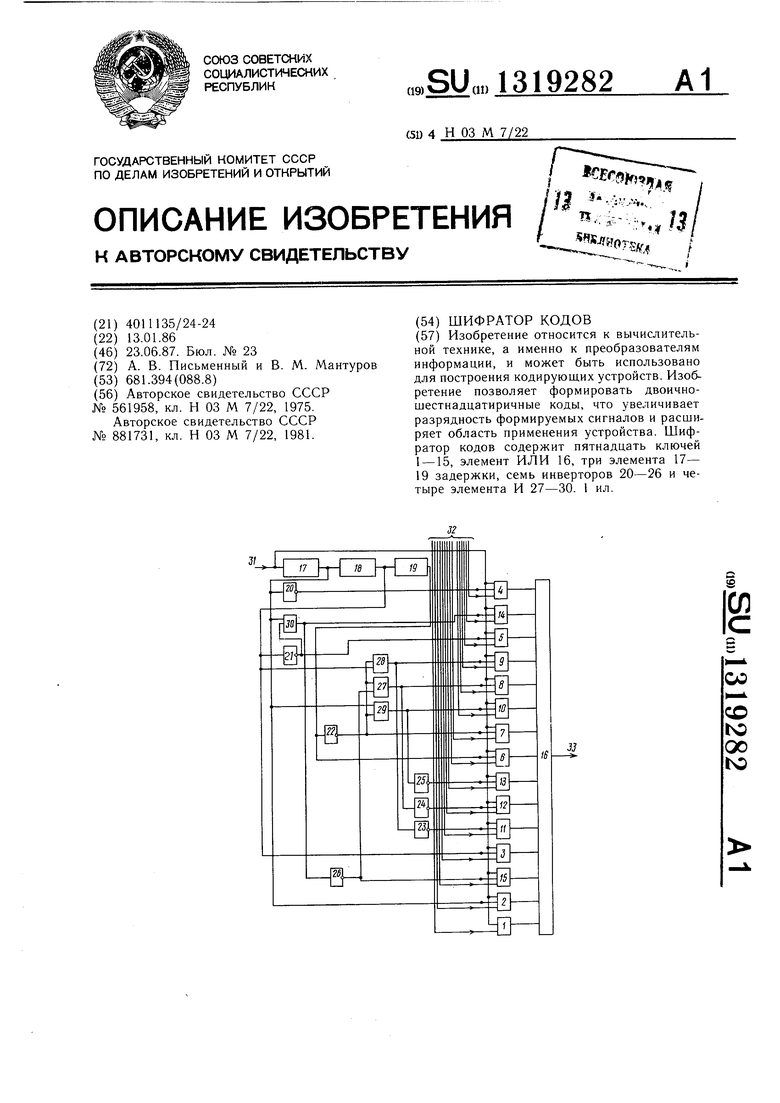

На чертеже представлена функциональная схема шифратора кодов.

Шифратар кодов содержит первый - пятнадцатый ключи 1 -15, элемент ИЛИ 16, первый - третий элементы 17-19 задержки, первый - седьмой инверторы 20-26 и первый - четвертый элементы И 27-30, а также тактовый вход 31, управляюплие входы 32 и выход 33 шифратора.

Шифратор кодов работает следуюш,им образом.

При подаче тактового импульса 7о па вход 31 на первых входах ключей 1 -15 устанавливается логическая единица, которая разреп1ает в течение времени длительности тактового импульса Го передачу двоичной последовательности на соответствую- ший вход элемента ИЛИ 16 (при условии присутствия управляюш,его сигнала на одном из управляюш.их входов). Это обеспечивает получение на выходе 33 шифратора двоично- шестнадцатиричной последовательности за время прохождения тактового импульса Го, а также устраняются временные искажения, образованные задержанными сигналами, присутствующими после окончания тактового импульса Го.

Формирование двоичных комбинаций осуществляется путем логических операций над задержанными тактовыми импульсами. Сдвиг осуществляется на одну четвертую, две четвертые и три четвертые длительности тактового импульса на элементах 17- 19 соответственно. В результате сдвига тактового импульса Го на выходах T|-Тз элементов 17-19 задержки соответственно формируются следующие двоичные последовательности: 0111, ООП, 0001.

Взяв за основу сигналы Го, Т, Т и Гз возможно получение любой двоично-шестнадцатиричной комбинации. В схеме входные и выходные сигналы связаны следующими ло- гиескими соотноп1ениям:

Д1 То; Д2 Т,; Дз Тг; Д4 Т,; Д5 Тг;

Дб Та; Д7 Тз; Д8 Тз(1уГ2); Д9 Т2Тз;

Д|о Т,Тз; Д,,тТТз; (т7Г2); Д,з Т|Тз; Д|4 TiTz; Д15 Т,Т2.

В результате за период прохождения тактового импульса Го на соответствующие входь ключевых элементов поступают следующие двоичпые последовательности: 0001,

Составитель Б. Ходов

Редактор И. ШуллаТехред И. ВересКорректор М. Шароши

Заказ 2531/56Тираж 90 Подписное

ВНИИПИ Государстьенного комипета СССР по делам изобретений и открытий

П3035, Москва. Ж-35, Раушская маб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная. 4

0

0010, ООН, 0100, 0101, оно, 0111, 1000, 1001, 1010, 1011, 1100, 1101, 1110, 1111, При подаче управляющего сигнала на один из входов 32 на выход шифратора посту- пает соответствующая ему последовательность.

Формула изобретения

Q Шифратор кодов, содержащий первый - девятый ключи, выходы которых подключены к одноименным входам элемента ИЛИ, выход которого является выходом шифратора, первые входы ключей являются управляющими входами шифратора, первый и второй

5 элементы задержки, вход первого элемента задержки объединен с вторым входом первого ключа и является тактовым входом шифратора, выход первого элемента задержки соединен с вторым входом второго ключа и с входом второго элемента задержки, выход которого соединен с вторым входом третьего ключа, первый и второй инверторы, выходы которых соединены с вторыми входами соответственно четвертого и пятого ключей, отличающийся тем, что, с це5 лью повышения точности и быстродействия шифратора, в него введены третий элемент задержки, третий - седьмой инверторы, элементы И и десятый - пятнадцатый ключи, выходы которых соединены с одноименными входами элемента ИЛИ, выход

0 третьего элемента задержки соединен непосредственно с вторым входом шестого клю- чаи и через третий инвертор - со вторым входом седьмого ключа и с первыми входами первого, второго и третьего элементов И, выходы которых соединены непо5 средственно с вторыми входами соответственно восьмого, девятого и десятого ключей и соответственно через четвертый, пятый и шестой инверторы с вторыми входами одиннадцатого, двенадцатого и тринадцатого клюд чей, выход четвертого элемента И соединен непосредственно с вторым входом четырнадцатого ключа и через седьмой инвертор с вторым входом пятнадцатого ключа и с вторым входом первого элемента И, второй вход второго элемента И объединен с входами

5 второго инвертора и третьего элемента задержки и подключен к выходу второго элемента задержки, первый вход четвертого элемента И подключен к выходу второго инвертора, вход первого инвертора объединен с вторыми входами третьего и четвертого эле0 ментов И и подключен к выходу первого элемента задержки, третьи входы второго - пятнадцатого ключей подключены к тактовому входу шифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель временных интервалов | 1984 |

|

SU1167576A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297225A1 |

| Шифратор двоично-десятичного кода | 1980 |

|

SU881731A1 |

| Система динамической синхронизации и корректировки рангов объектов в АСУ | 1985 |

|

SU1305630A1 |

| Многоканальное устройство для измерения температуры | 1990 |

|

SU1791731A1 |

| Устройство для передачи и приема дискретной информации | 1990 |

|

SU1807579A1 |

| ШИФРАТОР | 1988 |

|

SU1605892A1 |

| Аналоговый регистратор | 1986 |

|

SU1608795A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1987 |

|

SU1416978A1 |

Изобретение относится к вычислительной технике, а именно к преобразователям информации, и может быть использовано для построения кодирующих устройств. Изобретение позволяет формировать двоично- шестнадцатиричные коды, что увеличивает разрядность формируемых сигналов и расширяет область применения устройства. Шифратор кодов содержит пятнадцать ключей 1 -15, элемент ИЛИ 16, три элемента 17- 19 задержки, семь инверторов 20-26 и четыре элемента И 27-30. 1 ил. сл JJ 00 со ьо 00 ьо

| Двоично-десятичный шифратор | 1975 |

|

SU561958A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шифратор двоично-десятичного кода | 1980 |

|

SU881731A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-13—Подача