Изобретение относится к радиотехнике и вычислительной технике и может использоваться в системах передачи дискретной информации различного назначения.

Цель - повышение пропускной способности канала связи путем увеличения коэффициента сжатия полосы частот пере- .даваемого сигнала за счет преобразования двоичных сигналов в 8-позиционные.

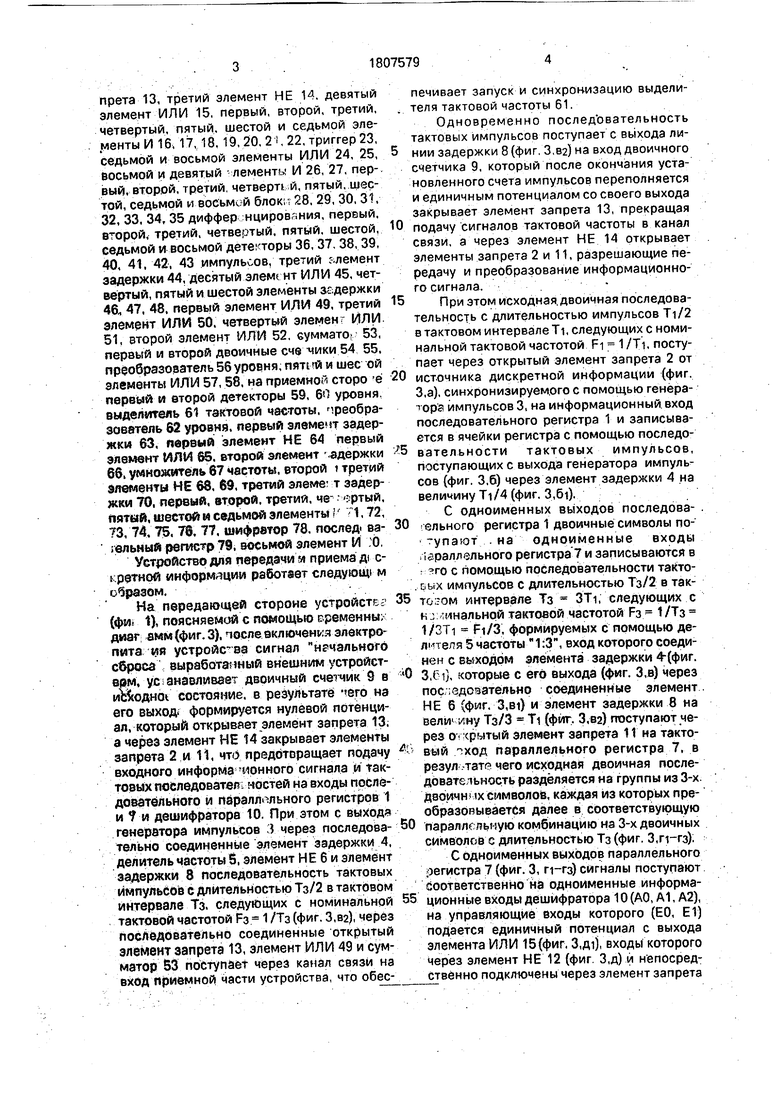

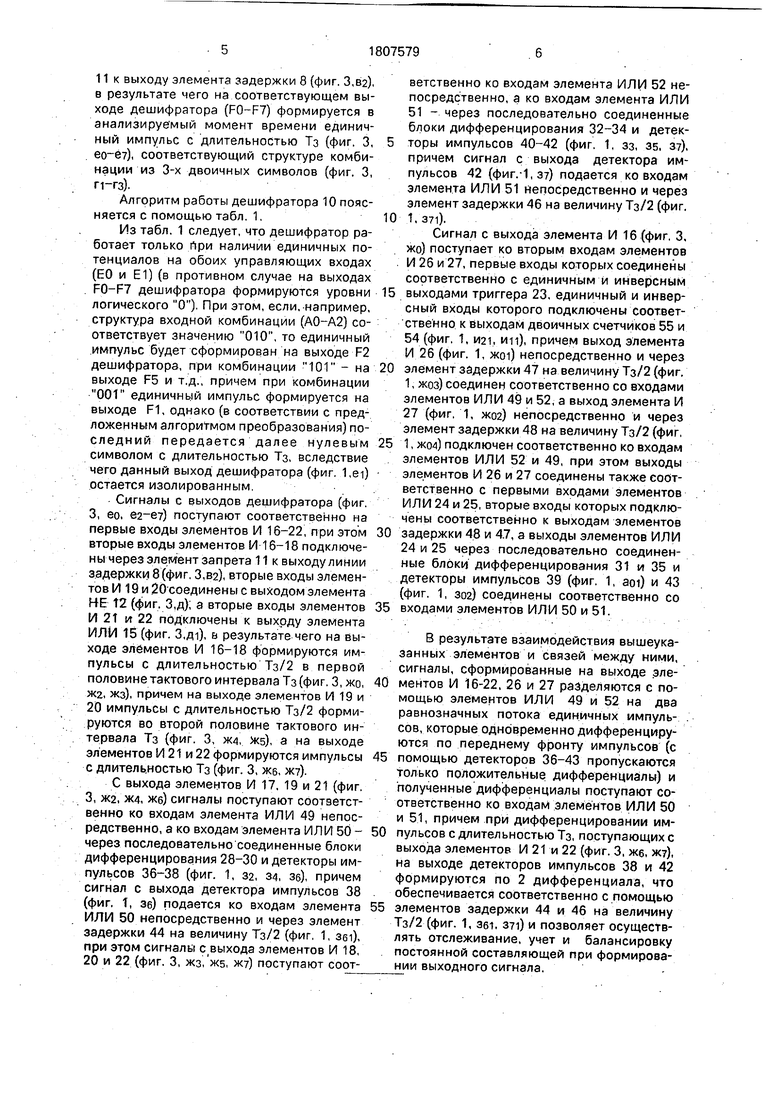

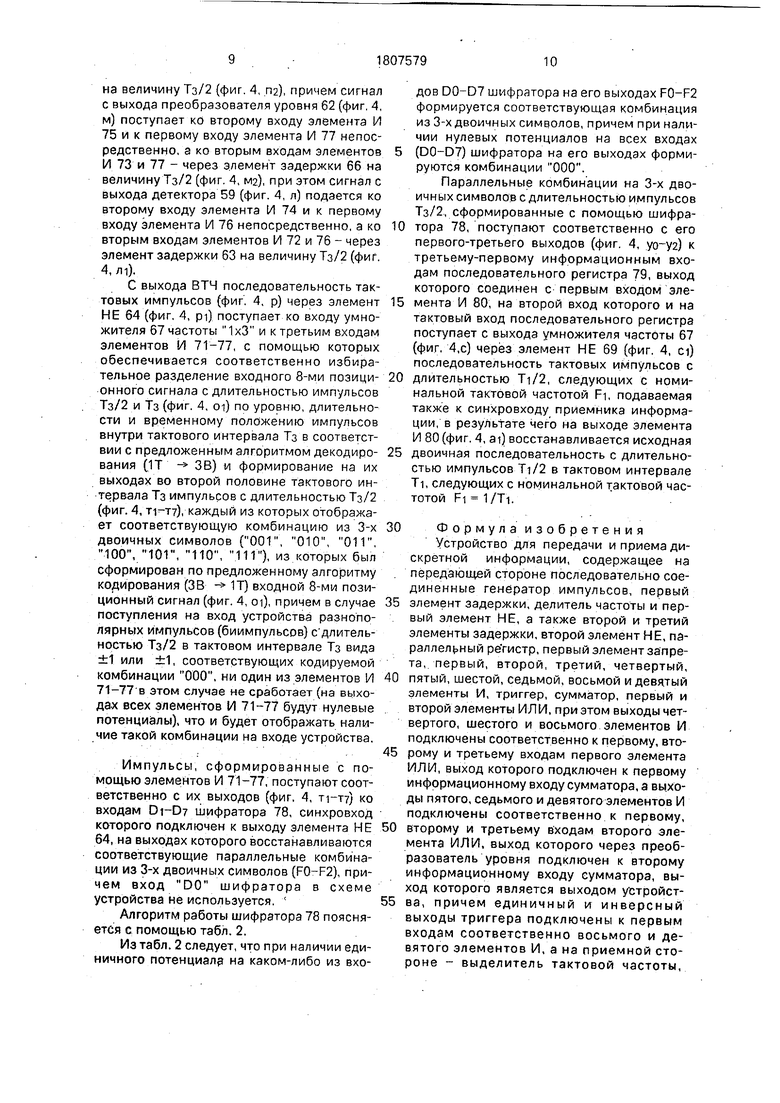

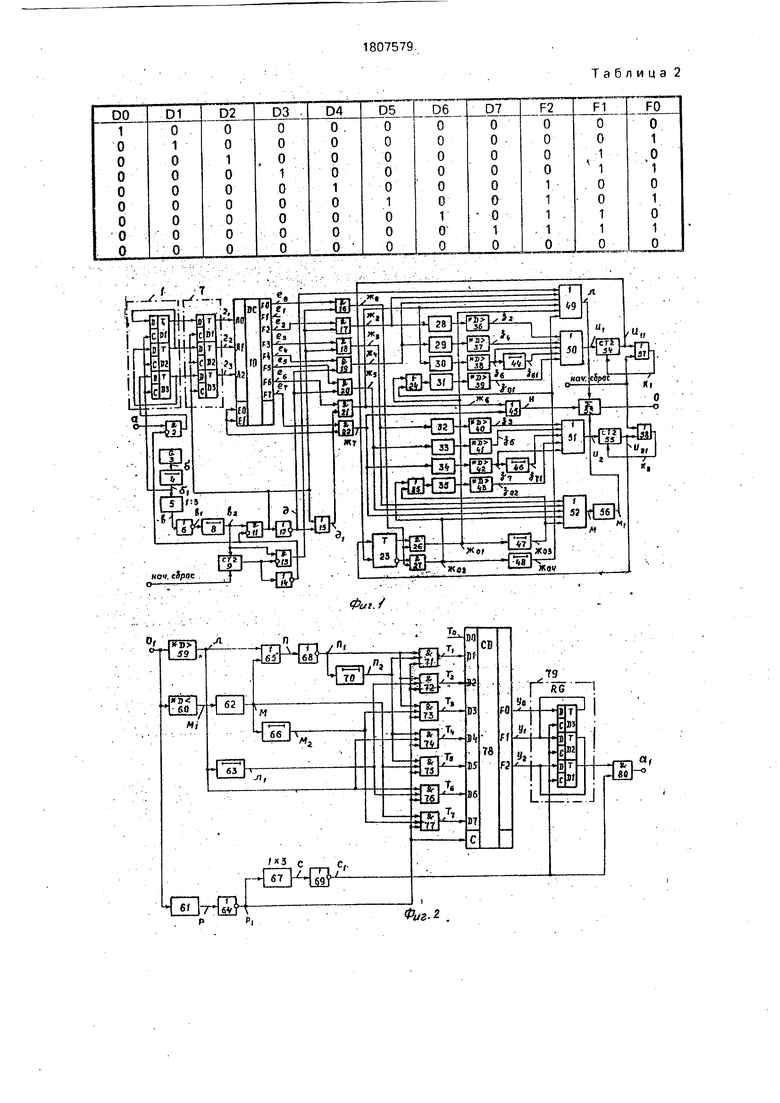

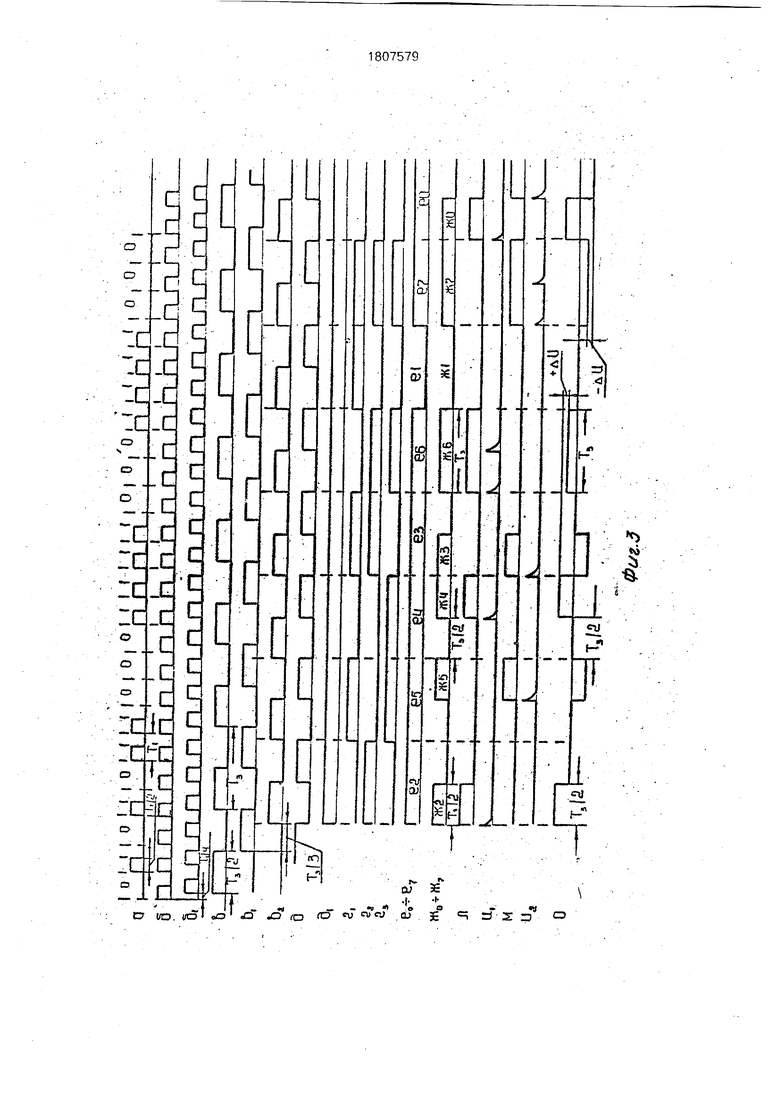

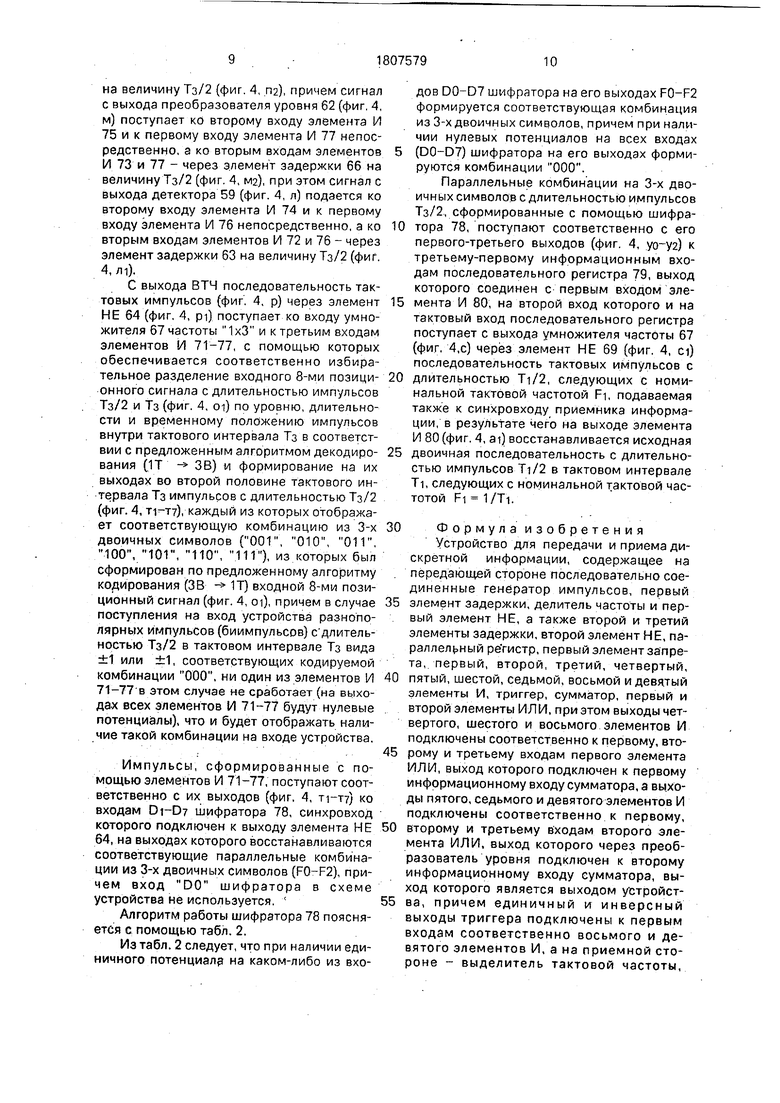

На фиг. 1, 2 представлены структурные электрические схемы передающей и приемной сторон устройства для передачи и приема дискретной информации: на фиг. 3 временные диаграммы работы передающей стороны; на фиг. 4 - временные диаграммы работы приемной стороны.

Устройство для передачи и приема дискретной информации содержит на передающей стороне последовательный регистр 1, первый элемент запрета 2, генератор 3 импульсов, первый элемент задержки 4, делитель 5 частоты, первый элемент НЕ 6, параллельный регистр 7, второй элемент задержки 8. третий двоичный счетчик 9. дешифратор 10, второй элемент запрета 11. второй элемент НЕ 12. третий элемент за00

о

vj 01

3

прета 13, третий элемент НЕ 14. девятый элемент ИЛИ 15, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И 16, 17,18,19,20. 24, 22, триггер 23, седьмой и восьмой элементы ИЛИ 24, 25, восьмой и девятый лементы И 26, 27, первый, второй, третий, четверо и, пятый, шестой, седьмой и восьмой блок;; 28, 29, 30, 31, 32, 33, 34, 35 дифференцирования, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой детекторы 36, 37. 38,39, 40, 41, 42, 43 импульсов, третий элемент задержки 44, десятый элемент ИЛИ 45, четвертый, пятый и шестой элементы задержки 46, 47, 48, первый элемент ИЛИ 49, третий элемент ИЛИ 50. четвертый элемент ИЛИ. 51, второй элемент ИЛИ 52, еуммато; 53, первый и второй двоичные счетчики 54 55, преобразователь 56уровня; пять и шее ой элементы ИЛИ 57, 58, на приемной сторо ё первый и второй детекторы 59, 60 уровня, выделитель 61 тактовой частоты, преобразователь 62 уровня, первый элемент задержки 63, первый элемент НЕ 64 первый элемент ИЛИ 65. второй эяемеит -.вдержки 66, умножитель 67 частоты, второй t третий элементы НЕ 68, 69, третий элеме: т задержки 70, первый, второй, третий, че- «ртый, пятый, шестой и седьмой элементы 71.72, 73, 74,75, ТВ, 77. шифратор 78. послед ва- гвльный регистр 79, восьмой элемент И :Ь,

Устройство для передачи и приема Д1 с- ирвтной информации работает следуют м образом.

На передающей стороне устройств ( 1), поясняемой с помощью временных диаг: амм (фиг. 3), после включения электролита ия устройства сигнал начального сброса выработанный внешним устройством, ус: анавяивает двоичный счетчик 9 в иекодно1 состояние, в результате чего на его выход формируется нулевой потенциал, который открывает .элемент запрета 13, а через элемент НЕ 14 закрывает элементы запрета 2 и 11, что предотвращает подачу входного информа ирнного сигнала и тактовых последоватеш мастей навходы последовательного и параллельного регистров 1 и и дешифратора 10. При этом с выхода генератора импульсов 3 через последова- тельно соединенные элемент задержки 4, делитель частоты 5, элемент НЕ 6 и элемент задержки 8 последовательность тактовых импульсов с длительностью Тз/2 в тактовом интервале Тз. следующих с номинальной тактовой частотой Рз 1 /Тз (фиг. З.ва), через последовательно соединенные открытый элемент запрета 13, элемент ИЛИ 49 и сумматор 53 поступает через канал связи на вход приемной части устройства, что обеспечивает запуск и синхронизацию выделителя тактовой частоты 61.

Одновременно последовательность тактовых импульсов поступает с выхода линии задержки 8 (фиг. З.ва) на вход двоичного счетчика 9, который после окончания установленного счета импульсов переполняется и единичным потенциалом со своего выхода закрывает элемент запрета 13, прекращая подачу сигналов тактовой частоты в канал связи, а через элемент НЕ 14 открывает элементы запрета 2 и 11, разрешающие передачу и преобразование информационного сигнала.

При этом исходная, двоичная последовательность с длительностью импульсов Ti/2 в тактовом интервале Ti, следующих с номинальной тактовой частотой FI 1 /Ti, поступает через открытый элемент запрета 2 от источника дискретной информации (фиг. 3,а), синхронизируемого с помощью генератора импульсов 3, на информационный вход последовательного регистра 1 и записывается в ячейки регистра с помощью последовательности тактовых импульсов, поступающих с выхода генератора импульсов (фиг. 3,6) через элемент задержки 4 на величину Ti/4 (фиг. 3,6i).

С одноименных выходов последовательного регистра 1 двоичные символы покупают . на одноименные входы параллельного регистра 7 и записываются в . пэ с помощью последовательности тактовых импульсов с длительностью Тз/2 в так- тозом интервале Тз 3Ti, следующих с н и мнальной тактовой частотой Рз - 1/Тз 1/ЗТч Fi/3, формируемых с помощью де- лителя 5 частоты 1:3, вход которого соеди- нен с выходом элемента задержки 4-(фиг. З.СН), которые с его выхода (фиг. 3,в) через последовательно соединенные элемент НЕ б (фиг. 3,Bi) и элемент задержки 8 на величину Тз/3 Ti (фит, З.ва) поступают через открытый элемент запрета 11 на тактовый лход параллельного регистра 7, в результате чего исходная двоичная последовательность разделяется на группы из 3-х. двоичных символов, каждая из которых преобразовывается далее в соответствующую параллельную комбинацию на 3-х двоичных символов с длительностью Тз (фиг. 3,п-гз);

С одноименных выходов параллельного регистра 7 (фиг. 3, n-гз) сигналы поступают соответственно на одноименные информационные входы дешифратора 10 (АО, А1, А2), на управляющие входы которого (ЕО, Е1) подается единичный потенциал с выхода элемента ИЛИ 15(фиг. 3,Д1), входы которого через элемент НЕ 12 (фиг. 3,д) и непосредственно подключены через элемент запрета

11 к выходу элемента задержки 8 (фиг. 3,В2), в результате чего на соответствующем выходе дешифратора (FO-F7) формируется в анализируемый момент времени единичный импульс с длительностью Тз (фиг. 3, ), соответствующий структуре комбинации из 3-х двоичных символов (фиг. 3, п-гз).

Алгоритм работы дешифратора 10 поясняется с помощью табл. 1.

Из табл. 1 следует, что дешифратор работает только при нали-чии единичных потенциалов на обоих управляющих входах (ЕО и Е1) (в противном случае на выходах FO-F7 дешифратора формируются уровни логического О). При этом, если,-например, структура входной комбинации (АО-А2) соответствует значению 010, то единичный .импульс будет сформирован на выходе F2 дешифратора, при комбинации 101 - на выходе F5 и т.д., причем при комбинации 001 единичный импульс формируется на выходе F1, однако (в соответствии с предложенным алгоритмом преобразования) последний передается далее нулевым символом с длительностью Тз, вследствие чего данный выход дешифратора (фиг. 1,ei) остается изолированным.

Сигналы с выходов дешифратора (фиг. 3, ео, е2-еу) поступают соответственно на первые входы элементов И 16-22, при этом вторые входы элементов И 16-18 подключены через элемент запрета 11 к выходулинии задержки 8 (фиг. 3,В2), вторые входы элементов И 19 и .20 соединены с выходом элемента НЕ 12 (фиг, 3,д); а вторые входы элементов И 21 и 22 подключены к выходу элемента ИЛИ 15 (фиг. 3,Д1), ь результате чего на выходе элементов И 16-18 формируются импульсы с длительностью Тз/2 в первой половине тактового интервала Тз (фиг. 3, жо, Ж2, жз), причем на выходе элементов И 19 и 20 импульсы с длительностью Тз/2 формируются во второй половине тактового интервала Тз (фиг. 3, ЖА, ЖБ), а на выходе элементов И 21 и 22 формируются импульсы с длительностью Тз (фиг. 3, же, ж).

С выхода элементов И 17. 19 и 21 (фиг. 3, Ж2, Ж4, же) сигналы поступают соответственно ко входам элемента ИЛИ 49 непосредственно, а ко входам элемента ИЛИ 50 - через последовательно соединенные блоки дифференцирования 28-30 и детекторы импульсов 36-38 (фиг. 1, 32, 34, зе), причем сигнал с выхода детектора импульсов 38 (фиг. 1, зе) подается ко входам элемента ИЛИ 50 непосредственно и через элемент задержки 44 на величину Тз/2 (фиг, 1, 351), при этом сигналы выхода элементов И 18, 20 и 22 (фиг. 3, жз, ЖБ, ж) поступают соответственно ко входам элемента ИЛИ 52 непосредственно, а ко входам элемента ИЛИ 51 - через последовательно соединенные блоки дифференцирования 32-34 и детек- торы импульсов 40-42 (фиг. 1, зз, 35, з), причем сигнал с выхода детектора импульсов 42 (фиг.-1, з) подается ко входам элемента ИЛИ 51 непосредственно и через элемент задержки 46 на величину Тз/2 (фиг.

1.371).

Сигнал с выхода элемента И 16 (фиг. 3.

жо) поступает ко вторым входам элементов

И 26 и 27, первые входы которых соединены

соответственно с единичным и инверсным

выходами триггера 23, единичный и инверсный входы которого подключены соответственно к выходам двоичных счетчиков 55 и 54 (фиг. 1, И21, иц), причем выход элемента И 26 (фиг. 1, жси) непосредственно и через

элемент задержки 47 на величину Тз/2 (фиг. 1, жоз) соединен соответственно со входами элементов ИЛИ 49 и 52, а выход элемента И 27 (фиг. 1, жо2) непосредственно и через элемент задержки 48 на величину Тз/2 (фиг,

1, жси) подключен соответственно ко входам элементов ИЛИ 52 и 49, при этом выходы элементов И 26 и 27 соединены также соответственно с первыми входами элементов ИЛИ 24 и 25, вторые входы которых подключены соответственно к выходам элементов

задержки 48 и 47, а выходы элементов ИЛИ 24 и 25 через последовательно соединенные блоки дифференцирования 31 и 35 и детекторы импульсов 39 (фиг. 1, aoi) и 43 (фиг. 1, зо2) соединены соответственно со

входами элементов ИЛИ 50 и 51.

В результате взаимодействия вышеуказанных элементов и связей между ними, сигналы, сформированные на выходе элементов И 16-22, 26 и 27 разделяются с помощью элементов ИЛИ 49 и 52 на два равнозначных потока единичных импульсов, которые одновременно дифференцируются по переднему фронту импульсов (с

помощью детекторов 36-43 пропускаются только положительные дифференциалы) и полученные дифференциалы поступают соответственно ко входам элементов ИЛИ 50 и 51, причем при дифференцировании импульсов с длительностью Тз, поступающих с выхода элементов И 21 и 22 (фиг. 3, же, ж), на выходе детекторов импульсов 38 и 42 формируются по 2 дифференциала, что обеспечивается соответственно с помощью

элементов задержки 44 и 46 на величину Тз/2 (фиг. 1, 361. 37i) и позволяет осуществлять отслеживание, учет и балансировку постоянной составляющей при формировании выходного сигнала.

Положительные дифференциалы, сформированные на выходе элементов ИЛИ 50 и 51 (фиг. 3, HI, иг), поступают соответственно на входы двоичных счетчиков 54 и 55, устз- навливаемых первоначально (при включении электропитания устройства) в исходное состояние сигналом начального сброса, выработанным внешним устройством, который через элементы ИЛИ 57 и 58 подается соответственно на их установочные входы.

С помощью двоичных счетчиков осуществляется раздельный подсчет импульсов для каждого из двух равнозначных потоков дифференциалов (фиг. 1, HI, И2), причем счет импульсов двоичного счетчика устанавливается обычно равным 2П (п 2, 3, 4 ...). При этом следует иметь в виду, что при меньшем значении п осуществляется более точная балансировка сигнала по постоянной составляющей.

При достижении установленного счета импульсов на выходе двоичных счетчиков 54 и 55 формируются единичные сигналы переполнения 9 фиг. 1, ип, И21). которые поступают соответственно на инверсный и единичный входы триггера 23 непосредственно, а на их установочные входы -через элементы ИЛИ 57 и 58, что вызывает переключение триггера 23 в соответствующее положение и сброс счетчиков в исходное состояние, после чего цикл работы счетчиков повторяется аналогично.

.Импульсы с длительностью Тз/2 и Тз, сформированные с помощью элементов ИЛИ 49 и 52, поступают соответственно с их выходов (фиг. 3, л, м) к первому и второму информационным входам сумматора 53 непосредственно и через преобразователь уровня 56, обеспечивающий преобразование положительных импульсов (фиг. 1, м) в отрицательные (фиг. 3,.Mi), в результате чего на выходе сумматора формируется разнопо- лярный 8-ми позиционный сигнал с длительностью импульсов Тз/2 и Тз (фиг. 3,о), частота следования которых соответствует значению Тз Р1/3.

В соответствии с предложенным алгоритмом преобразования, при равной вероятности появления 1 и О в структуре исходной двоичной последовательности /р(1) р(0) - 0,5/ и при достаточно длинном интервале анализа постоянная составляющая в спектре разнополярного 8-ми позиционного сигнала отсутствует.

При появлении комбинации 000 в структуре входной двоичной последовательности на выходе сумматора формируются разнопблярные импульсы (биимпульсы) вида ± 1 или ± 1 с длительностью Тз/2, полярность которых устанавливается переключением триггера 23, управляемым сигналами с выхода двоичных счетчиков, что, в свою очередь, значительно

улучшает текущую балансировку 8-ми позиционного сигнала по постоянной составляющей и повышает его помехоустойчивость. Для обеспечения одинаковой помехозащищенности импульсов, передаваемых с

длительностью Тз/2 иТз, введена корректировка выходных импульсов, в соответствии с которой амплитуда положительных и отрицательных импульсов с длительностью Тз уменьшается соответственно- на величину

± Ди (с учетом искажений, вносимых линией связи при заданной скорости передачи), что достигается в результате воздействия единичного сигнала, поступающего с выхода элементов И 21 и 22 (фиг. 3,

же. ж) через элемент ИЛИ 45 (фиг. 3,н) на управляющий вход сумматора 53.

На приемной стороне устройства (фиг. 2), поясняемой с помощью временных диаграмм (фиг. 4), входной 8-ми позиционный сигнал с длительностью импульсов Тз/2 и Тз (фиг. 4, Oi) поступает на вход выделителя тактовой частоты (ВТЧ) 61, который после прекращения подачи с передающей стороны синхросигнала тактовой частоты с длительностью импульсов Тз/2 (меандра), передние фронты импульсов в котором совпадают с началом тактового интервала Тз, переходит в режим синхронизации входной

последовательностью импульсов.

При этом равнополярный 8-ми позиционный сигнал поступает одновременно на входы детекторов уровня 59 и 60, включенных соответственно в прямом и обратном

направлениях, с помощью которых разделяется соответственно на последовательности положительных (фиг. 4, л) и отрицательных (фиг, 4, м) импульсов.

Затем последовательность положительных импульсов с выхода детекторов 59 и 60 (фиг. 4, л) непосредственно, а последовательность отрицательных импульсов с выхода детектора 60 - через преобразователь

уровня 62, обеспечивающий преобразование отрицательных импульсов (фиг. 4, MI) в положительные (фиг. 4, MI), поступает ко входам элемента ИЛИ 65, сформированный однополярный сигнал с выхода которого

(фиг. 4,п) через элемент НЕ 68 (фиг.4, щ) подается к первым входам элементов И 71- 73 непосредственно, а к первым входам элементов И 7.4 и 75 и ко второму входу элемента И 71 - через элемент задержки 70

на величину Тз/2 (фиг. 4, П2), причем сигнал с выхода преобразователя уровня 62 (фиг. 4, м) поступает ко второму входу элемента И 75 и к первому входу элемента И 77 непосредственно, а ко вторым входам элементов И 73 и 77 - через элемент задержки 66 на величину Тз/2 (фиг. 4, ма), при этом сигнал с выхода детектора 59 (фиг. 4, л) подается ко второму входу элемента И 74 и к первому входу элемента И 76 непосредственно, а ко вторым входам элементов И 72 и 76 - через элемент задержки 63 на величину Тз/2 (фиг, 4,Л1).

С выхода ВТЧ последовательность тактовых импульсов (фиг. 4, р) через элемент НЕ 64 (фиг, 4, pi) поступает ко входу умножителя 67 частоты 1x3 и к третьим входам элементов И 71-77, с помощью которых обеспечивается соответственно избирательное разделение входного 8-ми позиционного сигнала с длительностью импульсов Тз/2 и Тз (фиг. 4, oi) по уровню, длительности и временному положению импульсов внутри тактового интервала Тз в соответствии с предложенным алгоритмом декодирования (IT - 3В) и формирование на их выходах во второй половине тактового интервала Тз импульсов с длительностью Тз/2 (фиг. 4, тч-ту), каждый из которых отображает соответствующую комбинацию из 3-х двоичных символов (001, 010, 011, 100, 101, 110, 111), из которых был сформирован по предложенному алгоритму кодирования (3В - 1Т) входной 8-ми позиционный сигнал (фиг. 4, oi), причем в случае поступления на вход устройства разнопо- лярных импульсов (биимпульсов) с длительностью Тз/2 в тактовом интервале Тз вида ±1 или ±1, соответствующих кодируемой комбинации 000, ни один из элементов И 71-77 в этом случае не сработает (на выходах всех элементов И 71-77 будут нулевые потенциалы), что и будет отображать наличие такой комбинации на входе устройства.

Импульсы, сформированные с помощью элементов И 71-77, поступают соответственно с их выходов (фиг, 4, TI-T) ко входам Di-D шифратора 78, синхровход которого подключен к выходу элемента НЕ 64, на выходах которого восстанавливаются соответствующие параллельные комбинации из 3-х двоичных символов (FQ-F2), причем вход DO шифратора в схеме устройства не используется.

Алгоритм работы шифратора 78 поясняется с помощью табл. 2.

Из табл. 2 следует, что при наличии единичного потенциала на каком-либо из входов DO-D7 шифратора на его выходах FO-F2 формируется соответствующая комбинация из 3-х двоичных символов, причем при наличии нулевых потенциалов на всех входах

5 (DO-D7) шифратора на его выходах формируются комбинации 000.

Параллельные комбинации на 3-х двоичных символов с длительностью импульсов Тз/2, сформированные с помощью шифра0 тора 78, поступают соответственно с его первого-третьего выходов (фиг. 4, уо-у2) к третьему-первому информационным входам последовательного регистра 79, выход которого соединен с первым входом эле5 мента И 80, на второй вход которого и на тактовый вход последовательного регистра поступает с выхода умножителя частоты 67 (фиг, 4,с) через элемент НЕ 69 (фиг. 4, ci) последовательность тактовых импульсов с

0 длительностью Ti/2, следующих с номинальной тактовой частотой FI, подаваемая также к синхровходу приемника информации, в результате чего на выходе элемента И 80 (фиг. 4, at) восстанавливается исходная

5 двоичная последовательность с длительностью импульсов Ti/2 в тактовом интервале Ti, следующих с номинальной тактовой частотой FI 1/T i.

0 Фор мула изобретения

Устройство для передачи и приема дискретной информации, содержащее на передающей стороне последовательно соединенные генератор импульсов, первый

5 элемент задержки, делитель частоты и первый элемент НЕ, а также второй и третий элементы задержки, второй элемент НЕ, параллельный ре гистр, первый элемент запрета, первый, второй, третий, четвертый,

0 пятый, шестой, седьмой, восьмой и девятый элементы И, триггер, сумматор, первый и второй элементы ИЛИ, при этом выходы четвертого, шестого и восьмого элементов И подключены соответственно к первому, вто5 рому и третьему входам первого элемента ИЛИ, выход которого подключен к первому информационному входу сумматора, а выходы пятого, седьмого и девятого элементов И подключены соответственно к первому,

0 второму и третьему входам второго элемента ИЛИ, выход которого через преобразователь уровня подключен к второму информационному входу сумматора, выход которого является выходом уьтройст5 ва, причем единичный и инверсный выходы триггера подключены к первым входам соответственно восьмого и девятого элементов И, а на приемной стороне - выделитель тактовой частоты,

вход которого соединён с входами первого и второго детекторов уровня и является входом устройства, а также первый, второй и третий элементы задержки, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И, умножитель частоты, первый, второй и третий элементы НЕ, при этом выходы выделителя тактовой частоты и умножителя частоты подключены ко входам соответственно первого и третьего элементов НЕ, выход первого детектора уровня подключен к первому входу элемента ИЛИ, к второму входу которого через прёобразо- вательуровня подключен выход второго детектора уровня, а выход элемента ИЛИ через последовательно соединенные второй элемент НЕ и третий элемент задержки подключен к первому входу пятого элемента И, от л и ч а ю ще ё с я тем, что, с целью повышения пропускной способности канала связи путем увеличения коэффициента сжатия полосы частот передаваемого сигна- . ла за счет преобразования двоичных сигна- лювв восьмйпозиционНые, введены на передающей стороне дешифратор, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой блоки дифференцирования, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой детекторы импульсов, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый элементы ИЛИ, первый, второй и третий двоичные счетчики, четвертый, пятый и шестой элементы задержки, третий элемент НЕ, второй и третий элементы запрета и последовательный регистр, к информационному входу которого подключен выход первого элемента запрета, прямой вход которого является входом устройства/при этом выход первого элемента задержки подключен к тактовому входу последовательного регистра, одноименные выходы которого ЪдключеньГсоответственно к одноименным входам параллельного регистра, одноимённые выходы которого подключены к одноименным входам дешифратора, первый ёыхбд которого подключен к первому входу первого элемента И, а третий, четвертый, пятый, Шестой, седьмой и восьмой выходы дешифратора подключены соответственно к первым входам второго, третьего, четвертого, пятого, шестого и седьмого элементов И, при этом выходы первого, второго, третьего, четвёртого, пятого, шестого, седьмого и восьмого блоков дифференцирования подключены к входам соответствующих детекторов импульсов, причем выходы первого, второго, третьего и четвертого де- тёктОрбб импульсов подключены соответственно к первому, второму, третьему и четвертому входам третьего элемента ИЛИ, к пятому входу которого через третий элемент задержки подключен выход третьего детектора импульсов, а выходы пятого, шестого, седьмого и восьмого детекторов импульсов подключены соответственно к первому, второму, третьему и четвертому входам четвертого элемента ИЛИ, к пятому входу которого

через четвертый элемент задержки подключен выход седьмого детектора импульсов, выходы третьего и четвертого элементов ИЛИ подключены к входам соответственно первого и второго двоичных счетчиков, выходы которых подключены соответственно к инверсному и единичному входам триггера и к первым входам соответственно пятого и шестого элементов ИЛИ, выходы которых подключены к установочным входам соответственно первого и второго двоичных счетчиков, вторые входы пятого и шестого элементов ИЛИ объединены и являются входом сигнала начального сброса устройства, при этом выход первого элемента И подключен к вторым входам восьмого и девятого элементов И, выходы которых соответственно через пятый и шестой элементы задержки подключены к четвертым входам соответственно второго и первого эпементов ИЛ И и к первым входам соответственно восьмого и седьмого элементов ИЛИ, к вторым входам которых подключены выхоДы соответственно девятого и восьмого эле- 7ментрв и, а выходы седьмого и восьмого

элементов ИЛИ подключены соответственно к входам четвертого и восьмого блоков дифференцирования, выходы второго и третьего элементов И подключены к пятым входам соответственно первого и второго

элементов ИЛИ и к входам соответственно первого и пятого блоков дифференцирования, выходы четвертого, пятого, шестого и седьмого элементов И подключены к входам соответственно второго, шестого,

третьего и седьмого блоков дифференцирования, а выход первого элемента НЕ подключен к входу второго элемента задержки, выход которого подключен к прямым входам второго и третьего элементов запрета и

к входу третьего двоичного счетчика, установочный вход которого является входом сигнала начального сброса устройства, а выход третьего двоичного счетчика подключен к инверсному входу третьего элемента запрета и через третий элемент НЕ - к инверсным входам первого и второго элементов Запрета, при этом выход второго элемента запрета подключен к тактовому входу параллельного регистра, вторым входам первого, второго и третьего элементов И, первому входу девятого элемента ИЛИ и к входу второго элемента НЕ. выход которого подключен к вторым входам четвертого и пятого элементов И и к второму входу девятого элемента ИЛИ, выход которого подключен к управляющим входам дешифратора и вторым входам шестого и седьмого элементов И, выходы которых подключены соответственно к первому и второму входам десятого элемента ИЛИ, выход которого подключен к управляющему входу сумматора, а выход третьего элемента запрета подключен к шестому входу первого элемента ИЛИ, а на приемной стороне - последовательный ре- гистр и шифратор, к первому, второму, третьему, четвертому, пятому, шестому и седьмому входам которого подключенй выходы соответственно первого, второго, третьего, четвертого, пятого, шестого и седьмого элементов И, а первый, второй и третий выходы шифратора подключены со- отв етственно к третьему, второму и первому входам последовательного регистра, выход которого подключен к первому входу вось-

мрго элемента И, выход которого является выходом устройства, а выход второго элемента НЕ подключен к первым входам первого, второго и третьего элементов И и через третий элемент задержки - к второму входу первого элемента и первому входу четвертого элемента И, а выход преобразователя уровня подключен к второму входу пятого элемента И и первому входу седьмого элемента И и через второй элемент задержки - к вторым входам третьего и седьмого элементов И, выход первого детектора уровня подключен к первому входу шестого элемента И, к второму входу четвертого элемента И и через первый элемент задержки - к вторым входам второго и шестого элементов И, при этом выход первого элемента НЕ подключен к входу умножителя частоты, третьим входам первого, второго, третьего, четвертого, пятого, шестого и седьмого элементов И и к синхровходу шифратора, а выход третьего элемента НЕ подключен к тактовому входу последовательного регистра и к второму входу восьмого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь восьмипозиционного временного кода в двоичный код | 1990 |

|

SU1771070A1 |

| Устройство для уплотнения каналов связи | 1990 |

|

SU1809544A1 |

| Преобразователь двоичного кода в восьмипозиционный временной код | 1990 |

|

SU1730725A1 |

| Автокорреляционный измеритель параметров псевдослучайного фазоманипулированного сигнала | 1990 |

|

SU1823137A1 |

| Устройство для двухкратного уплотнения каналов связи | 1991 |

|

SU1775871A1 |

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1646068A1 |

| Устройство для анализа ритма сердца | 1986 |

|

SU1553049A1 |

| Устройство для автоматического контроля генератора случайных чисел | 1982 |

|

SU1038942A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ЧАСТОТЫ И ВРЕМЕННОЙ ЗАДЕРЖКИ РАДИОСИГНАЛА | 1992 |

|

RU2048683C1 |

Использование: в радиотехнике и вычислительной технике, в системах передачи дискретной информации различного .назначения; Сущность изобретения: устройство содержит на передающей стороне последовательный регистр, первый, второй, третий элементы запрета, генератор импульсов, первый, третий, четвертый, пятый, шестой элементы .задержки, первый, второй, третий двоичные счетчики, дешифратор, второй, третий элемент НЕ, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый элементы ИЛИ, первый, второй, третий; четвертый, пятый. шестой и седьмой элементы И, триггер, восьмой и девятый элементы И, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой блоки дифференцирования, первый, второй, третий, четвертый, пятый, шестой, седьмой восьмой детекторы импульсов, сумматор, преобразователь уровня, на приемной стороне - первый и второй детекторы уровня, выделитель тактовой частоты, преобразователь уровня, первый, второй, третий элементы задержки, первый, второй, третий элементы НЕ. первый элемент ИЛИ, умножитель частоты, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой элементы И, шифратор-, последовательный регистр. Устройство обеспечивает трехкратное сжатие полосы частот передаваемого сигнала путем преобразования двоичных сигналов в 8-ми позиционные, что достигается в результате трехкратного увеличения длительности формируемых импульсов и уменьшения частоты их следования. 4 ил., 2 табл.

Примечание: значком X обозначено произвольное состояние, соответствующее уровню логического О или логической 1.

Таблица 1

Таблица 2

О Ю. КО J «О «О .О CD (. И S Э o

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1646068A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1993-04-07—Публикация

1990-10-22—Подача