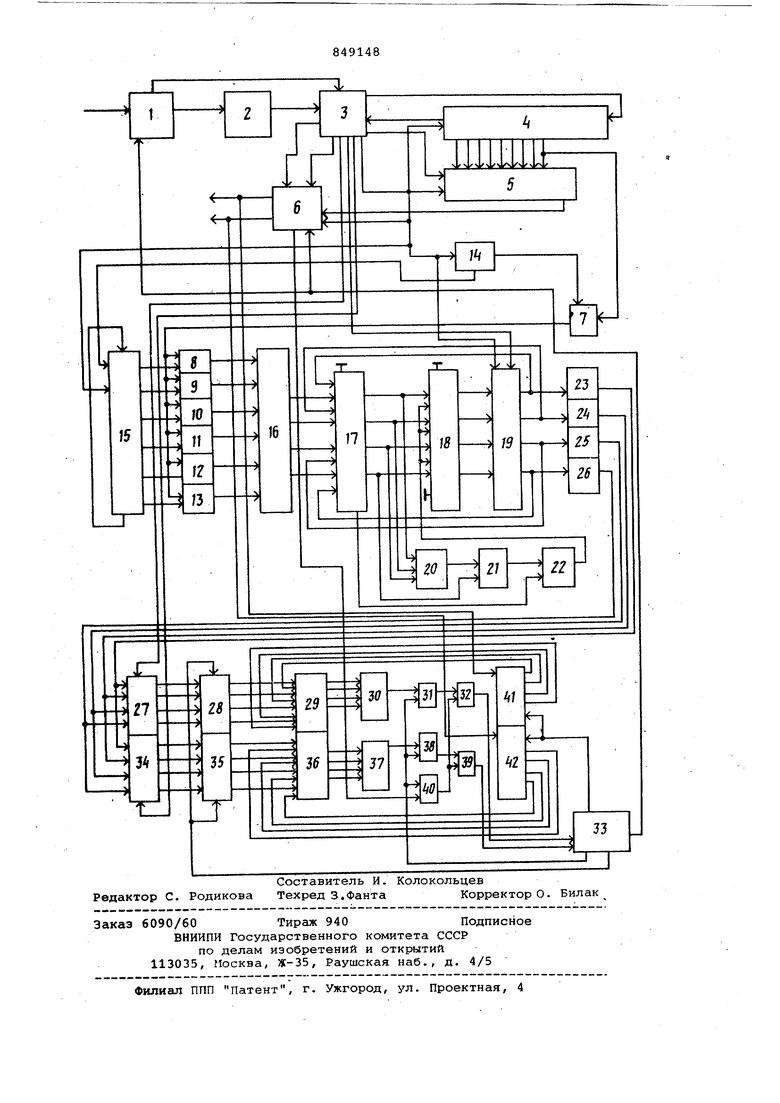

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах числового программного управления станками и другим технологическим оборудованием. Известно устройство для программно го управления, состоящее из перфоленты, читающего устройства, выходы KOTO роге присоединены к запоминающим устройствам координат и ко входам контрольного делителя и тактового генератора, выход которого подключен ко входу умножителя, параллельные выходы которого присоединены к выходам запоминающих устройств координат Х, X,. , Y , Y , а выход переполнения через делитель подключен ко.входу первого триггера, выход которого присоединен к первой группе выходных ключей координат, выходы которых через первый элемент ИЛИ присоединены ко второму входу контрольного делителя, выход которого подключен к первому входу индикатора ошибки, второй вход которого подключен к выходу второго элемента ИЛИ, выходы которого присоединены, к выходам второго триггера, счетный вход которого присоединен к выходу делителя, а вторая группа ключей присоединена к выходам запоминающих устройств координат, а их попарно объединенные выходы присоединены ко входам сглгикиваквдих делителей координат fl . Однако в таком устройстве для контроля правильности отработки перемещений на перфоленте необходимо задавать помимо основной информации дополнительные контрольные коды, что усложняет программирование и исключает возможность использования устройства в системах с коррекцией величин перемеядений, задаваемых внутри сясгемы, так как каждая коррекция требует изменения корректирующего кода. Кроме того, схема такого устройства достаточно сложна. Известно также устройство для контроля передачи информации в двоич«о-двсятичном коде между блоками цифровой вычислительной машины, содержащее ячейку памяти одного знака, входы которой являются входами устройства, блок формирования сигнала сшибки, выход которого является выходом устройства, триггер, входы которого являются входами устройства, а выход соединен с управляющим входом блока формирования ошибки, а также двоично-десятичный сумматор, сдвигающий двоично-десятичный регистр,при выходи ячейки памяти одного sliaка соединены с первой группой входов одноразрядного двоично-десятичного сумматора, выходы которого соединены со блока Формирования .сигнала ошибки и со входами младшего разряда сдвигающего двоично-десятичного регистра, выходы старшего разряда сдвигающего двоично-десятичного регистра соединены со второй г)руппой входов одноразрядного.десятично-двоичного сумматора, управляющий вход устройства и вход тактовых сигналов устройства соединены с соответствующими входами ячейки памяти одного зна ка и сдвигающего двоично-десятичного регистра fizj , Недостатком этого устройства является ограниченность его функциональных возможностей, так как оно способно контролировать только передачу дво ично-десятичной информации по цепям передачи, в которых не происходит преобразование, ее кодов и изменение ее значений, т.е. переработка. Вследствие этого невозможно использовать устройство в современных системах чис лового программного управления. Наиболее близким по технической сущности к предлагаемому является уст ройство для программного управления, состоящее из блока ввода программы, выходы которого соединены со входами счетчика строк, преобразователя кода и блока памяти, соединенного со входами блока отработки координатных пе ремещений и контрольного счётчика по модулю D, причем выход блока отработ ки координатных перемещений соединен со входом контрольного счетчика, входы элемента И соединены с выходами счетчика строк и преобразователя кода, вход дополнительного счетчика по модулю D соединен с выходом элемента И, а выход - с блоком памяти Гз1. Недостатком известного устройства является то, что контролируемая инфо мация хотя и может быть преобразована, но не может быть переработана (изменена) в контролируемом канапе устройства. Кроме того, оно может ра ботать только с двоично-десятичными кодами, что резко сужает функциональ ные ,врзможности устройства и область егр применения, поскольку в современ ных Системах ЧПУ информация програм|МЫ, водимая с перфоленты или другог носителя в двоично-десятичном коде, как правило, преобразуется, т.е. пер водится в двоичный код и изменяется на величины коррекций размеров инструмента, и выполняется преобразова ние координат. Поэтому использовать в современных системах ЧПУ данное устройство фактически невозможно без резкого снижения функциональных возможностей системы, глубины контроля его точности и, следовательно, таких эксплуатационных характеристик, как время поиска неисправностей. Цель изобретения - расширение области применения устройства за счет обеспечения условий автоматического введения различных по величине :коррекций скоростей подачи или оборотов шпинделя и повышение надежности и |Точности устройства за счет автоматического исключения превышения выходной частоты задающего устройства и максимальной частоты, воспринимаемой приводом. Поставленная цель достигается тем, что в устройство для задания программы, содержащее последовательно соединенные блок ввода информации, блок преобразователей кода, блок управления , первый сдвиговый регистр, второй сдвиговый регистр и интерполятор, второй вход блока управления подключен ко второглу выходу блока ввода информации, третий вход - ко второму выходу первого сдвигового регистра, вторые выходы - ко вторым входам интерполятора, третий вход - ко вторым входам первого и второго сдвиговых регистров и к третьему входу интерполятора, а четвертый выход - к третьему входу второго сдвигового регистра, и два канрша управления, каждый из которых состоит из контрольного счетчика, соединенного первым входом с первым выходом интерполятора и последовательно соединенных первого и второго регистров памяти, а первые входы первых регистров памяти подключены к четвертым выходам блока управления, введены третий сдвиговой регистр, первый элемент И блок формирования койанд и последовательно соединенные блок элементов задержки, коммутатор, группа ключей, шифратор, первый сумматор, первый элемент ИЛИ, второй элемент И, второй элемент ИЛИ, второй сумматор, третий регистр памяти, и группа инверторов, а в каждый канал управления - последовательно соединенные третий сумматор, третий элемент И, четвертый элемент И и пятый элемент И, выход которого подключен ко входу блока формирования команд, соединенного первым выходом со вторыми входами вторых регистров памяти, вторым выходом - со вторыми входами контрольных счетчиков, третьим выходом - со входом блока ввода информации и с третьим входом интерполятора, а четвертым выходом - со вторыми .входами четвертых элементов И и с первым входом первого элемента И, второй вход которого подключен ко второму выходу интерполятора, а выход - ко вторым входам пятых элементов И, первый вход третьего сдвигового регистра соединен со вторым выходом блока эле-.ментов задержки, выходы - со вторыми входами группы ключей, а второй вход со входом блока элементов задержки, со вторым входом третьего регистра памяти и с третьим выходом блока управления, подключенного пятым выходом к третьему входу третьего регист ра памяти, выходы которого соединены со вторыми входами первого сумматора подключенного одним из первых входов ко второму входу второго элемента И, вторым выходом - ко второму входу второго элемента ИЛИ, а первыми выходами - ко вторым входам второго сумматора, первые и вторыевходы третьего сумматора каждого кангша уп равления соединены соответственно с выходами второго регистра памяти и контрольного счетчика данного канала управления, выходы группы инверторов соединены со вторыми входами пер вых регистров памяти, а второй вход коммутатора подключен к одному из первых выходов первого сдвигового регистра. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит блок 1 ввода информации, блок 2 преобразователей кода, блок 3 управления, первый 4 и второй 5 сдвиговые регистры, интерпо лятор б, коммутатор 1, группу ключей 8-13, блок 14 элементов задержки, тр тий сдвиговый регистр 15, шифратор 16, первый 17 и второй 18 сумматоры, третий регистр 19 памяти, первый эле мент. ИЛИ 20, второй элемент И 21, ,второй элемент ИЛИ 22, группы инверторов 23-26, первый 27 и второй 28 регистры памяти, третий сумматор 29, третий 30, четвертый 31 и пятый 32 элементы И, блок 33 формирования команд, первый 34 и второй 35 регистры памяти, третий сумматор 36, третий 37, четвертый 38, пятый 39 и первый 40элементы И и контрольные счетчики 41и 42, Устройство работает следующим образом. Информация управлякядей программы с перфоленты или другого носителя поступает на вход блока 1, в котором осуществляется ее контроль на четкость и дешифрирование. После этого дешифрированная инфбрмация распределяется следующим образом. Информация о геометрических перемещениях через блок 2 поступает в блок 3, на другой вход которого пост пают дешифрированные адреса-геометрической информации , Y, К в подго товительные (G) функции, определяющи характер преобразования в блоке 3, например перевод абсолютных координа в относительные, корректирование гео метрической информации на величины коррекций размеров инструмента, формирование информации в виде, пригодном для интерполятора, т,е, в приращениях. Конечные результаты, поДлежшцие высылке в интерполятор 6 для дальнейшей обработки, записываются последовательно младшими разрядами вперед в двадцатишестиразрядный регистр 4. Причем l-24-e разряды этого регистра хранят цифровую информацию, а 25 и 26 отводятся для хранения модифицированного знака, т,е. 00 - плюс, 11 - минус, 0,1 и 10 - запрещенные комбинации. С параллельных выходов 1-24 разрядов регистра 3 информация переписывается в регистр 5, построенный таким образом, что в нем информация сдвигается старвиими разрядами вперед, что необходимо для выполнения операции нормализации, которая имеет место в интерполяторе 6,. Поэтому инфор-т мация о перемещениях д X, д Y переписы|вается из регистра 5 в промежуточную |память интерполятора 6 последовательно старшими разрядами вперед синхронно с тактами Т1-Т26. Такты Т1-И26, а также сигналы Запись X и Запись Z вырабатываются блоком 3 и поступают в интерполятор 6. По окончании отработки предыдущего кадра информация, записанная в промежуточной памяти интерполятора, начинает отрабатываться и в виде унитарных кодов появляется на его вых&де по каналам X и Z. Причем, если в интерполятор 6 были записаны величины приращений X и Z, то за время отработки кадра по кангшам X и Z должно пройти ДХ и д Z импульсов. Для контроля соответствия количества отработанных импульсов заданному количеству в момент высылки информации из блока 3 в регистр 4 осуществляется свертка по модулю 9 двоично-кодированной величины дх или AY. Эта свертка осуществляется следующим образом. Информация с выхода 24-го разряда регистра 4 через коммутатор 7 поступает на параллельно объединенные входы ключей 8-13, причем коммутатор 7 включается синхронно с тактом Т1-Т26, но с задержкой на два такта сигналом, поступающим на его управляющий вход с выхода блока 14. Со второго выхода этого блока сигнал поступает на управляющий вход регистра 15 и разрешает циркуляцию единицы в этом регистре с частотой тактов Т1-Т26. Поскольку в исходном состоянии единица находилась в младшем разряде регистра 15, а все остальные его разряды бь1ли в нулях, то при последовательном сдвиге единицы разрешающие потенциалы появляются поочередно на входах ключей 8-13. Причем за время записи в ререгистр 4 двадцатичвтырехразрядного числа единица в регистре 15 совершает четыре полных оборота. Работа схемы формирования контрольного кода дноичного числа по модулю 9 основана на 1 24 8 16 32 Число Остаток

Таким образом, в случае нгшичия единицы в соответствующем разряде необходимо в сумматор контрольного числа по модулю 9 добавить соответствующий этому разряду остаток, что реализуется следуюцим образом.

Единицы, двигаясь в регистре 15 поочередно, поступают на ключи 8-13. В случае, если на информационном входе этих ключей в это время также присутствует единица, сигнал появляется на выходе соответствующего ключа. При этом сигнал на выходе ключа 8 соответствует остатку 1, на выходе ключа 9 - Остатку 2, ключа 10 - остатку 4, ключа 11 - остатку 8, ключа 12 - остатку 7 и ключа 13 - остатку 5. Выходные сигналы ключей 8-13, поступая на соответствующие входы шифратора 16, вызывают появление на его выходе двоично-кодированных комбинаций, соответствующих числам 1, 2, 4, 8, 7, 5. Эти двоичные числа поступают на входы сумматора 17, на входы второго слагаемого - код остатка свертки по модулю 9, полученного в предыдущем суммировании с выходов регистра 19.. Поскольку суммирование необходимо осуществлять по модулю 9 в случае возникновения переноса из старшего разряда сумматора 17, а также в случае превьпиения выходной комбинацией этого сумматора числа 8, т.е. двоичной комбинацией 1000 откорректировать эту выходную комбинацию на величину поправки 0111 (т.е. 7).

Это достигается тем, что любая из единиц трех младших разрядов сумматора 17 проходит через элемент ИЛИ 21 на вход элемента И 21, на второй вход которой подается сигнал с выхода старшего разряда сумматора 17. Выходной сигнал элемента И 21 объединяется элементом ИЛИ 22 с выходным сигналом переполнения сумматора 17 и поступает на входы трех младших разрядов сумматора 18, на входе переноса млёщшего разряда и на входе старшего разряда вторюго слагаемого котофого запаян сигнал О, т.е. потежциал земли. Благодаря корректирующему действию цепи: элемент ИЛИ 20 - элемент И 21 - элемент ИЛИ 22 на выходе сумматора 18 всегда имеется остаток свертки по модулю 9 суммы числа, хранимого в регистре 19 и числа, сформированного на выходе шифратора 16, Каждый из тактовых импульсов Т1-Т26 своим задним фронтом записывает новый код в регистр 19,

что необходимо для надежного установления выходной комбинации на выходе сумматора 18. Для осуществления записи в регистр 19 по заднему фронту регистр построек триггерах. При отсутствии информации на выходах шифратора 16 кодовая комбинация, хранимая в регистре 19, просто подтверждается.

По окончании свертки величины ДХ она из регистра 4 переписывается в регистр 5 по сигналу, поступающему на синкровход параллельной записи регистра 5 с соответствующего выхода блока 3. Одновременно этот блок вырабатывает сигнал записи контроля координаты X, который через инверторы 23-26 переписывает контрольный код из регистра 19 в регистр 27 промежуточной памяти контрольного кода (Координаты X. После этого блок 3 вырабатывает сигнал перезаписи величины дХ из регистра 5 в промежуточную память интерполятора 6 и сигнал сброса регистра 19. Затем аналогично совершается цикл работы по определению и высылке в интерполятор 6 величины &2 и ее контрольного числа, котор9е записывается в регистр 34 промежуточно памяти кода контроля координаты д.

После этого по сигналу Пуск, поступаю ему из блока 33, величины ДХ и Д1 начинают отрабатываться интерполятором 6, одновременно блок 1 начинает вводить очередной кадр программы. По сигналу ИУ1, поступающему из блока 23, сбрасываются счетчики 41 и 42, а по сигналу ИУ , который также вырабатьавается .блоком 33, после сигнала Пуск контрольные коды приращений дХ и д Y переписываются в регистры pa6jO4eft памяти контрольных кодов регистров 28 и 35 соответственно. Выходные импульсы координатных приращений интерполятора 6 являются выходными сигналами устройства и одновременно поступают на счетные входы счетчиков 41 и 42, работающих по модулю 9. К концу отработки кадра в счетчиках оказываются числа, соответствующие по сверткам по модулю 9 количеству импульсов, отработанных соответствующей координатой.

Если введенная.в интерполятор 6 информация отработана верно, то остаток по модулю 9, записанный в регистре 28 и полученный в счетчике 41, а также остаток в регистре 35 и в счетчике 42 равны, но в регистрах 28 и 35 записаны инверсные коды остатков. периодической повторяемости остатков разрядов двоичных чисел. Ряд остатков по модулю 9 имеет вид: 641 1281 2561 512 Г1024 20481 4096

Следовательно, на выходах сумматоров 29 и 36 должны быть все единицы, так как сумма прямого и обратного.кодов одного и того же числа дает все единицы. При этом на выходах элементов И 30 и 37 имеются сигналы единиЦБ, которые поступают на входы элементов И 31 и 38. Элементы И 31, ,38 и- 40 в нормальном режиме работы по второму входу всегда открыты, и только в наладочном режиме на них с блока 33 заводится.нулевой сигнал Блокировка. Сигнал Окончание отработки кадра с выхода интерполятора 6 через элемент И 40 поступает на входы элементов И 32 и 39, на вторые входы которых поступают выходные сигналы элементов И 31 и 38.

Срабатывая, элемент И 32 формирует сигнал Координата X верно, а элемент И 39 - сигнал Координч1та Z верно . Если сформирован оба эти сигнала, то, поступая на блок 33, они запускают отработку следующего кадра программы. В противном случае следующий кадр запущен не будет, и будет включена соответствующая индикация.

Таким образом, предлагаемое устройство обеспечивает контроль отрабатываемых системой перемещений, несмотря на то, что вводимая информация была не только переведена из десятичной системы Влдвоичную, но и изменена в результате пересчета координа т и введения различных коррекций, что является основным преимуществом этого устройства, позволяющим использовать .его в сложных современных системах, в которых имеет место многоступенчатое преобразование информации.

Кроме того, использование предлагаемого устройства позволяет значительно улучшить надежность разработанных принципиальных схем в целом, а следовательно, сократить брак как при выпуске систем, так и при эксплуатации.

формула изобретения

Устройство для задания прогргиимы, содержащее последовательно соединенные блок ввода информации, блок преобразователей кода, блок управления, первый сдвиговый регистр, второй сдвиговый регистр и интерполятор, второй вход блока управления подключен ко второму выходу блока ввода информации, третий вход - ко второму выходу первого сдвигового регистра, вторые выходы - ко вторым входс1М интерполятора, третий вход - ко вторым входс1М первого и второго сдвиговых регистров и к третьему входу интерполятора, а четвертый выход - к третьему входу второго сдвигового регистра, и два канала управления, каждый из которых состоит из контрольного счетчика, соединенного первым входом с первым выходом интерполятора и последовательно соединенных первого и второго регистров памяти, а первые входы первых регистров памяти подключены к четвертым выходам блока управления, отличающееся тем, что, с целью расширения области применения и повышения надежности, устройства, в него введены третий сдвиговой регистр, первый элемент И, блок формирования команд и последовательно соединенные блок элементов задержки. Коммутатор, группа ключей, шиф0ратор, первый сумрлатор, первый элемент ИЛИ, второй элемент И, второй элемент ИЛИ, второй сумматор, третий регистр памяти, и группа инверторов , а в каждый канал управления 5последовательно соединенные третий сумматор, третий элемент И, четвертый элемент и и пятый элемент И, выход которого подключен ко входу блока формирования команд, соединенного

0 первым выходом со вторыми входами вторых регистров памяти, вторым выходом - со вторыми входами контрольных счетчиков, третьим выходом - со входом -блока ввода информации и с третьим входом интерполятора, а чет5вертым выходом - со вторыми входами четвертых элементов И и с первым входом первого элемента И, второй вход которого подключен ко второму выходу интерполятора, .а выход - ко

0 вторым входам пятых элементов И, первый вход третьего сдвигового регистра соединен со вторым выходом блока элементов задержки, выходы - со вторыми входами группы ключей, а второй

5 вход - со входом блока элементов задержки , со вторым входом,третьего регистра памяти и с третьим выходом блока управления, подключенного пятым выходом к третьему входу третьего ре0 . гистра , выходы.которого соединены со вторыми входами первого сумматора , подключенного одним из первых входов ко второму входу второго элемента И, вторым выходом - ко второму входу второго элемента ИЛИ, а первы5ми выходами - ко вторым входам второго сумматора, первые и вторые входы третьего сумматора каждого канала управления соединены соответственно с выходами второго регистра памяти и

O контрольного счетчика данного канала управления, выходы группы инверторов соединены со вторыми входами первых регистров памяти, а второй вход коммутатора подключен к одному из первых

5 выходов первого сдвигового регистра.

Источники информации, принятые во внимание при экспертизе

1.Вульфсон И.А, и др. Кодирование информации управляющих программ. М., Энергия, 1968, с, 76-77.

О

2.Авторское свидетельство СССР 581471, кл. G Об F 11/08, 1975.

3.Авторское свидетельство СССР 397891, кл. 6 05 В 19/14,-1971 (прототип).

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для задания программы | 1979 |

|

SU862118A1 |

| Устройство контроля для систем программного управления | 1990 |

|

SU1775716A1 |

| Линейно-круговой интерполятор | 1978 |

|

SU746431A1 |

| Цифровой интерполятор | 1986 |

|

SU1310778A1 |

| Линейно-круговой интерполятор | 1975 |

|

SU555381A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Программное задающее устройство | 1981 |

|

SU991376A1 |

| Линейно-круговой интерполятор | 1977 |

|

SU741234A1 |

| Устройство для программного управления | 1986 |

|

SU1397878A1 |

Авторы

Даты

1981-07-23—Публикация

1979-11-28—Подача