11297225

Изобретение относится к измерительной и вычислительной технике и преимущественно может быть использовано для аналого-цифрового преобразоватиш.

Цель изобретения - повьпиение бы- 5 стродействия аналого-11ифрового преобразования.

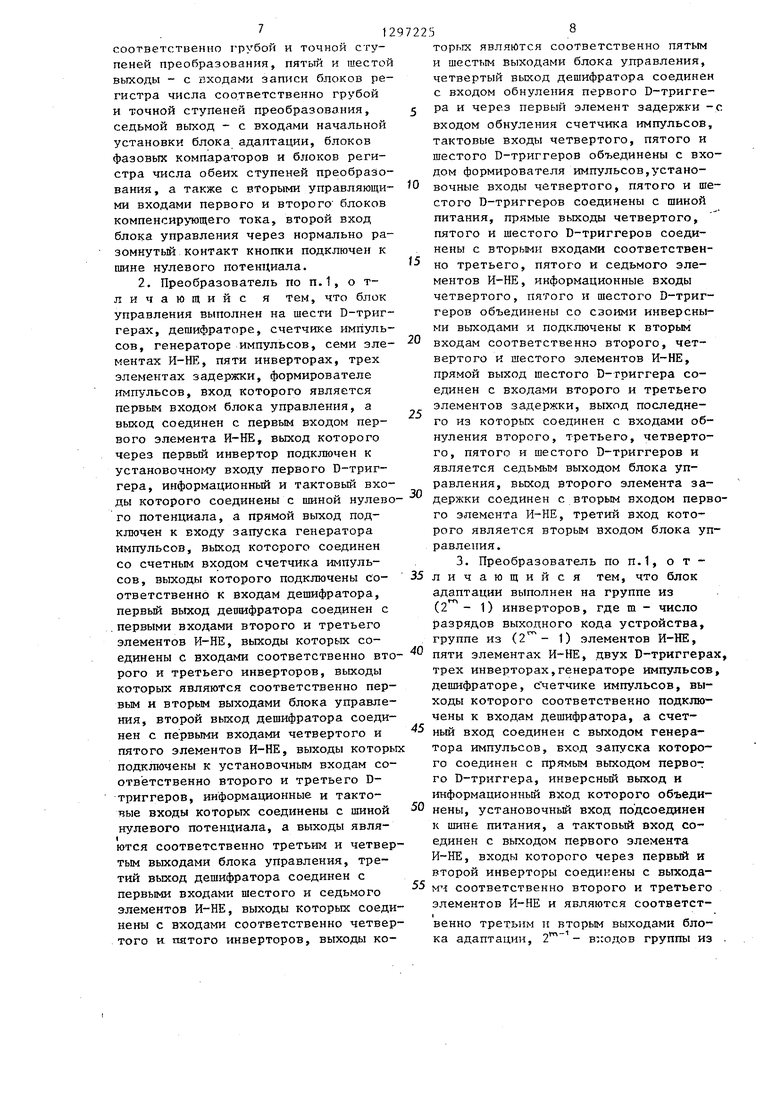

На фиг,1 представлена структурная схема аналого-цифрового преобразователя; на фиг,2 - функциональная схе- О ма блока управления; на фиг,3 - функциональная схема блока адаптации.

Аналого-цифровой преобразователь (фиг,1) содержит генератор 1 опорного напряжения, входной фазовращатель 2, блоки 3,4 фазовых компараторов, нифраторы 5, 6, блоки 7,8 регистров числа, дешифратор 9, блоки 10, 11 компенсирующего тока, ключ 12, фа

Ч/2 + ip/ ; Ч -f

лкс/i; мсхкс Xх i

ТО В течение первого такта преобразования сигнал С фазовым сдвигом Ч с выхода фазовращателя 2 поступает на вход грубой ступени преобразования, В зависимости от величины Ч в блоке 3 сработает соответству 5

ющее количество фазовых компараторов, после чего при помощи шифратора 5 формируются и заносятся в регистр 7 числа m двоичных разрядов выходного кода. Запись результатов преобразования в блоки 3, 5 и 7 осурдествля- ется по сигналам, поступающим соответ ственно с первого, третьего и пятого выходов блока 15 управления, С выхода регистра 7 код старших m разрядов поступает на выход устройства и

зовращатель 13 смещения, блок 14 одновременно на вход дешифратора 9.

птации и блок 15 управления.Код с выхода дешифратора 9 поступает

на информационный вход блока 14 адаптации, на втором выходе которого формируе-т-ся сигнал, включающий блок 10 компенсир лощего тока, под воздействием которого фаза выходного напряжения фазовращателя 2 уменьшается (сдвигается в направлении, противоположном тому, в котором она галась под воздействием преобразуемого сигнала), По окончании компенсации фаза выходного напряжения блока 2 удовлетворяет условию

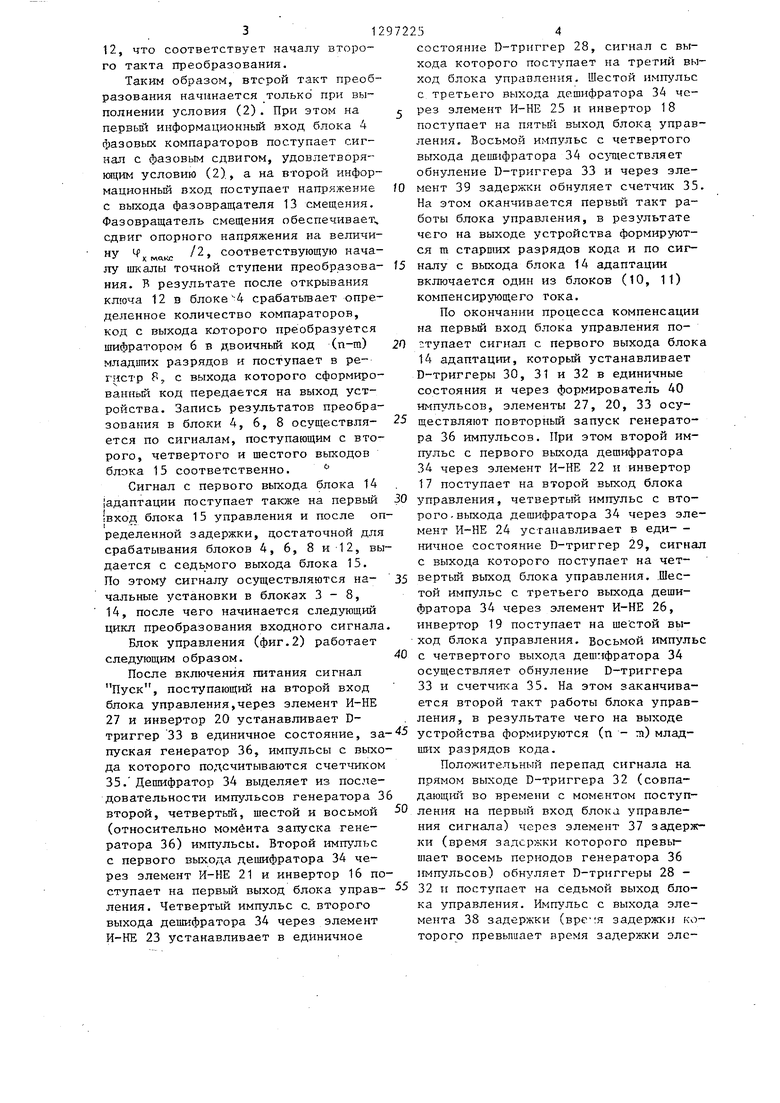

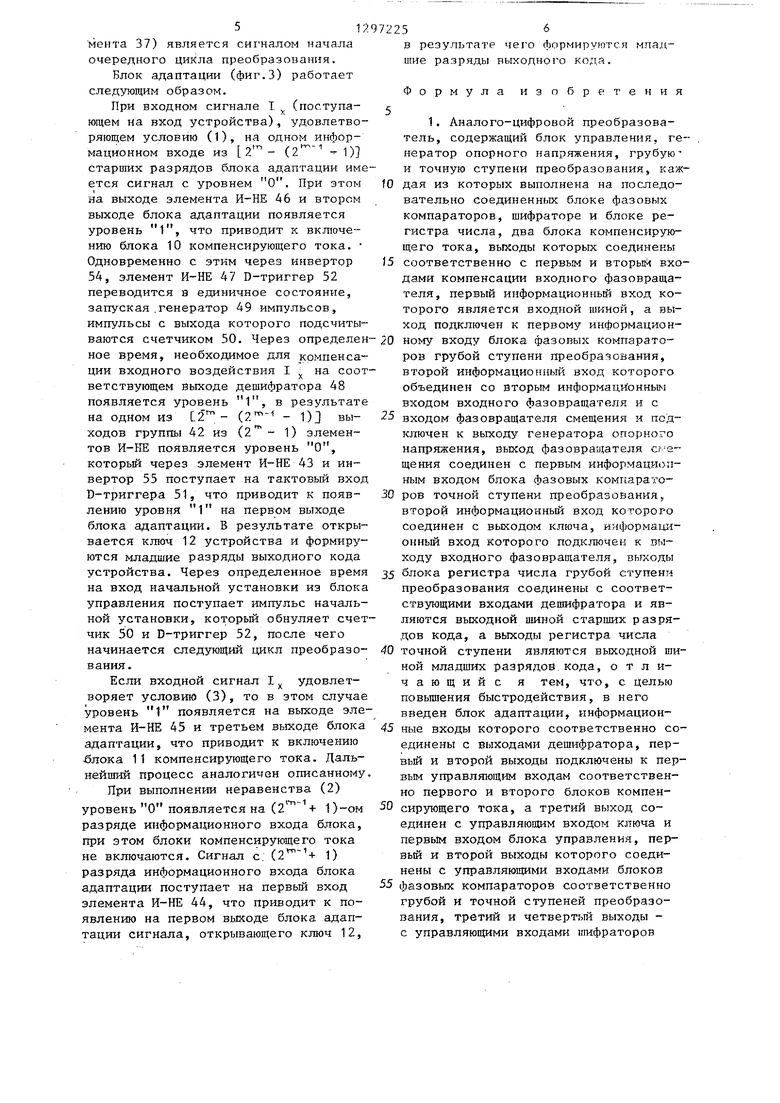

I Блок управления (фиг.2) содержит инверторы 16 - 20, элементы И-НЕ 21 - 27, D-триггеры 28 - 33, деигифратор ЗА, счетчик 35 импульсов, генератор 36 импульсов, элементы 37, 38, 39 задержки и формирователь 40 импульсов,

Влок адаптации (фиг,3) содержит ГРУЦПУ 41 из (2 - 1) инверторов, группу 42 из -( 1) элементов И-НЕ, элементы И-НЕ 43 - 47, дешифратор 48, генератор 49 импульсов, счетчик 50 импульсов, D-триггеры 51, 52 и инверторы 53, 54, 55,

Устройство (фиг,1) работает следующим образом.

После включения питания нажатием кнопки Пуск осуществляются начальные установки в блоках устройства, Входной сигнал 1, поступающий на информационный вход фазовращателя 2, преобразуется в фазовый сдвиг Ч опорного гармонического напряжения, которое подается на вход опорного сигнала фазовращателя 2 с генератора 1, В дальнейшем преобразованию подлежит не входной сигнал 1у,а величина фазового сдвига , однозначно-связанная со значением 1, Преобразование величины Ч осуществляется в два такта. На первом такте формируются m старших разрядов кода, на втором такте - (и - т) младших разрядов, В зависимости от величины Ч, возможны следующие три режима работы устройства.

Если преобразуемая величина W удовлетворяет соотношению

30

35

Ч Ч la (7

хмаксX хмакс хмоле

40

Если выполняется условие

.Kcl 3)

то В течение первого такта преобразования по сигналу с третьего выхода блока адаптации включается блок 11 компенсирующего тока, под воздей45 ствием которого фаза выходного напряжения блока 2 увеличивается (сдвигается в том ,же направлении, что и под воздействием преобразуемого сиг- няла), По окончании компенсации фа50 за выходного напряжения фазовращателя 2 также удовлетворяет соотношению (2) .

Если преобразуемая величина Ч удовлетворяет условию (2), то з

55 старпшй разряд регистра 7 записьша- ется 1, а в остальные разряды этого регистра - О. В результате на первом выходе блока адаптации фор- 1-даруется сигнгш, открывающий ключ

О

Ч/2 + ip/ ; Ч -f

лкс/i; мсхкс Xх i

ТО В течение первого такта преобразования сигнал С фазовым сдвигом Ч с выхода фазовращателя 2 поступает на вход грубой ступени преобразования, В зависимости от величины Ч в блоке 3 сработает соответству5

ющее количество фазовых компараторов, после чего при помощи шифратора 5 формируются и заносятся в регистр 7 числа m двоичных разрядов выходного кода. Запись результатов преобразования в блоки 3, 5 и 7 осурдествля- ется по сигналам, поступающим соответственно с первого, третьего и пятого выходов блока 15 управления, С выхода регистра 7 код старших m разрядов поступает на выход устройства и

одновременно на вход дешифратора 9.

35

Ч Ч la (7

хмаксX хмакс хмоле

Если выполняется условие

40

.Kcl 3)

то В течение первого такта преобразования по сигналу с третьего выхода блока адаптации включается блок 11 компенсирующего тока, под воздей45 ствием которого фаза выходного напряжения блока 2 увеличивается (сдвигается в том ,же направлении, что и под воздействием преобразуемого сиг- няла), По окончании компенсации фа50 за выходного напряжения фазовращателя 2 также удовлетворяет соотношению (2) .

Если преобразуемая величина Ч удовлетворяет условию (2), то з

55 старпшй разряд регистра 7 записьша- ется 1, а в остальные разряды этого регистра - О. В результате на первом выходе блока адаптации фор- 1-даруется сигнгш, открывающий ключ

12, что соответствует началу второго такта преобразования.

Таким образом, второй такт преобразования начинается только при выполнении условия (2). При этом на первый информационньй вход блока 4 фазовых компараторов поступает си1- нал с фазовым сдвигом, удовлетворя- Ю1циь5 условию (2), а на второй информационный вход поступает напряжение с выхода фазовращателя 13 смещения. Фазовращатель смещения обеспечивает, сдвиг опорного напряжения на величину хмакс соответствующую началу шкалы точной ступени преобразова- кия. В результате после открывания ключа 12 в блоке 4 срабатьшает определенное количество компараторов, код с выхода которого преобразуется шифратором 6 в двоичньй код (n-m) младших разрядов и поступает в регистр 8j с выхода которого сформированной код передается на выход устройства. Запись результатов преобразования в блоки 4, 6, 8 осуществля- ется по сигналам, поступающим с второго, четвертого и шестого выходов блока 15 соответственно.

Сигнал с первого выхода блока 14 |адаптации поступает также на первый вход блока 15 управления и после опI .....

ределенной задержки, достаточной для срабатывания блоков 4, 6, 8 и 12, выдается с седьмого выхода блока 15. По этому сигналу осуществляются на- чальные установки в блоках 3-8, 14, после чего начинается следующий цикл преобразования входного сигнала

Блок управления (фиг.2) работает следующим образом.

После включения питания сигнал Пуск, поступающий на второй вход блока управления,через элемент И-НЕ 27 и инвертор 20 устанавливает D- триггер 33 в единичное состояние, за пуская генератор 36, импульсы с выхода которого подсчитываются счетчиком 35. Дешифратор 34 выделяет из последовательности импульсов генератора 3 второй, четвертьй, шестой и восьмой (относительно момента запуска генератора 36) импульсы. Второй импульс с первого выхода дешифратора 34 через элемент И-НЕ 21 и инвертор 16 поступает на первьй выход блока управ- ления. Четвертый импульс с. второго выхода дешифратора 34 через элемент И-НЕ 23 устанавливает в единичное

состояние D-триггер 28, сигнал с выхода которого поступает на третий выход блока управления. Шестой импульс с третьего выхода дешифратора 34 через элемент И-НЕ 25 и инвертор 18 поступает на пятьй выход блока управления. Восьмой импульс с четвертого выхода дешифратора 34 ос тцествляет обнуление D-триггера 33 и через элемент 39 задержки обнуляет счетч -1к 35 На этом оканчивается nepBbtfi такт работы блока управления, в результате чего на выходе устройства формируются m старших разрядов кода и по сигналу с выхода блока 14 адаптации включается один из блоков (10, 11) компенсирующего тока.

По окончании процесса компенсации на первьй вход блока управления поступает сигнал с первого выхода блок 14 адаптации, которьй устанавливает D-триггеры 30, 31 и 32 в единичные состояния и через формирователь 40 импульсов, элементы 27, 20, 33 осуществляют повторный запуск генератора 36 импульсов. При этом второй импульс с первого выхода дешифратора 34 через элемент И-НЕ 22 и инвертор 17 поступает на второй выход блока управления, четвертый импульс с второго- выхода дешифратора 34 через элемент И-НЕ 24 устанавливает в еди

ничное состояние D-триггер 29, сигнал с выхода которого поступает на четвертьй выход блока управления. .Шестой импульс с третьего выхода дешифратора 34 через элемент И-НЕ 26, инвертор 19 поступает на ше стой выход блока управления. Восьмой импуль с четвертого выхода дешифратора 34 осуществляет обнуление D-триггера 33 и счетчика 35. На этом заканчивается второй такт работы блока управления, в результате чего на выходе устройства формируются (п - т) младших разрядов кода.

Положительный перепад сигнала на прямом выходе D-триггера 32 (совпа- дающга во времени с моментом поступления на первый вход блока управления сигнала) через элемент 37 задержки (время задержки которого превышает восемь периодов генератора 36 импульсов) обнуляет D-триггеры 28 - 32 и поступает на седьмой выход блока управления. Импульс с выхода элемента 38 задержки (вре ;я задержки которого превьпцает время задержки эле мента 37) является сигналом начала очередного цикла преобразования.

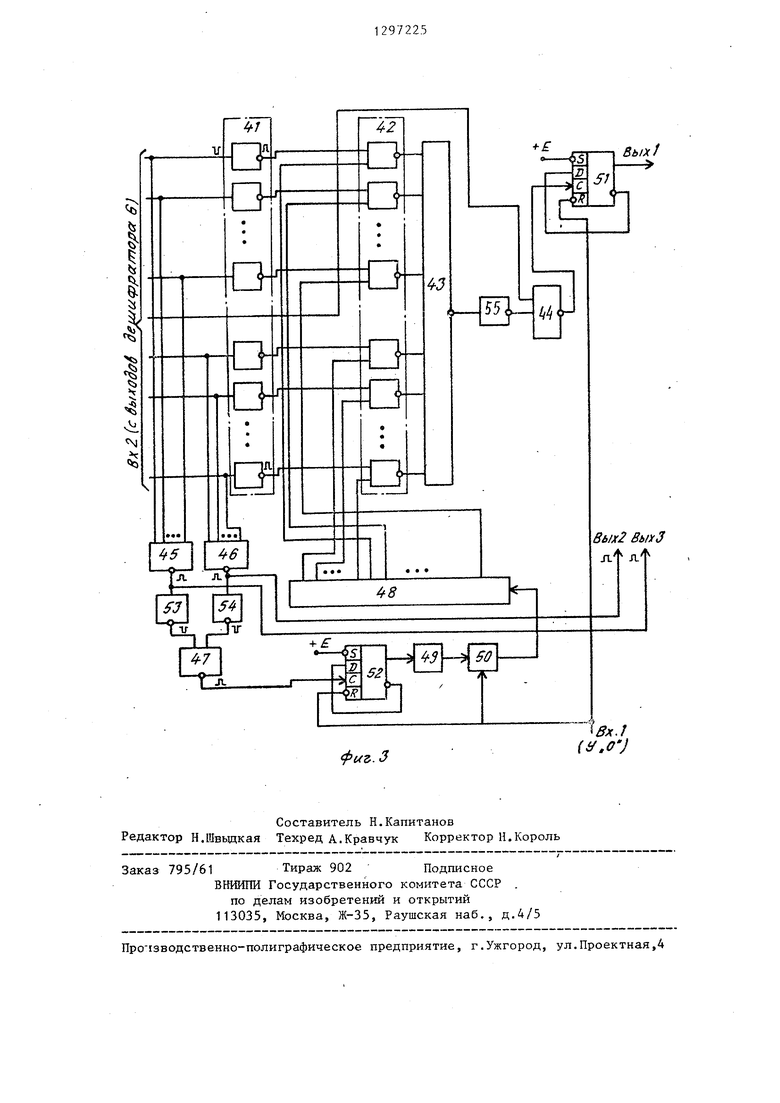

Блок адаптации (фиг.З) работает следующим образом.

При входном сигнале I (поступающем на вход устройства), удовлетворяющем условию (1), на одном информационном входе из 2 - (2 - 1) старших разрядов блока адаптации имеется сигнал с уровнем О. При этом на выходе элемента И-НЕ 46 и втором выходе блока адаптации появляется уровень 1, что приводит к включению блока 10 компенсирующего тока. Одновременно с этим через инвертор 54, элемент И-НЕ 47 D-триггер 52 переводится в единичное состояние, запуская .генератор 49 импульсов, импульсы с выхода которого подсчитываются счетчиком 50. Через определенное время, необходимое для компенсации входного воздействия I на соответствующем выходе дешифратора 48 появляется уровень 1, в результате на одном из Lf - ( - 1) выходов группы 42 из (2 - 1) элементов И-1Ш появляется уровень О, которьй через элемент И-НЕ 43 и инвертор 55 поступает на тактовый вход D-триггера 51, что приводит к появлению уровня 1 на первом выходе блока адаптации. В результате открывается ключ 12 устройства и формируются младшие разряды выходного кода устройства. Через определенное время на вход начальной установки из блока управления поступает импульс начальной установки, которьй обнуляет счетчик 50 и D-триггер 52, после чего начинается следующий цикл преобразо- в ания.

Если входной сигнал I удовлетворяет условии) (3), то в этом случае уровень 1 появляется на выходе элемента И-НЕ 45 и третьем выходе блока адаптации, что приводит к включению блока 11 компенсирующего тока. Дальнейший процесс аналогичен описанному. При выполнении неравенства (2)

уровень О появляется на (2 + 1)ом разряде информационного входа блока, при этом блоки компенсирующего тока не включаются. Сигнал с. ( 1) разряда информационного входа блока адаптации поступает на первый вход элемента И-НЕ 44, что приводит к появлению на первом выходе блока адаптации сигнала, открывающего ключ 12,

в результате чего формируются мла;д- шие разряды выходного кода.

Формула изобретени

5

1. Аналого-цифровой преобразователь, содержащий блок управления, генератор опорного напряжения, грубую и точную ступени преобразования, кажtO дая из которых выполнена на последовательно соединенных блоке фазовых компараторов, шифраторе и блоке регистра числа, два блока компенсирующего тока, выходы которых соединены

)5 соответственно с первьм и вторый входами компенсации входного фазовращателя, первый информационньЕй вход которого является входной шиной, а выход подключен к первому информацион20 ному входу блока фазовых компараторов грубой ступени преобразования, второй информационный вход которого объединен со вторым информационным входом входного фазовращателя и с

25 входом фазовращателя смещения и подключен к выходу генератора опорного напряжения, выход фазовращателя ск е- щения соединен с первым информационным входом блока фазовых комггарато30 ров точной ступени преобразования, второй информационньй вход которого соединен с выходом ключа, информатди- онньй вход которого подключен к выходу входного фазовращателя, выходы

35 блока регистра числа грубой ступени преобразования соединены с соответствующими входами дешифратора и являются выходной шиной старших разрядов кода, а выходы регистра числа

40 точной ступени являются выходной шиной младших разрядов кода, о т л и- чающийс я тем, что, с целью повышения быстродействия, в него введен блок адаптации, информацион45 ные входы которого соответственно соединены с выходами дешифратора, первый и второй выходы подключены к первым управляющим входам соответственно первого и второго блоков компенсирующего тока, а третий выход соединен с управляющим входом ключа и первым входом блока управления, первый и второй выходы которого соединены с управляющими входами блоков

55 фазовых компараторов соответственно грубой и точной ступеней преобразования, трети г1 и четвертый выходы - с управляю1ЦИ1 о1 входами шифраторов

50

1

соответственно т рубой и точной ступеней преобразования, пятый и шестой выходы - с входами записи блоков регистра числа соответственно грубой и точной ступеней преобразования, седьмой выход - с входами начальной установки блока адаптации, блоков фазовых компараторов и блоков регистра числа обеих ступеней преобразования, а также с вторыми управляющими входами первого и второго блоков компенсирующего тока, второй вход блока управления через нормально ра- зомнутый контакт кнопки подключен к шине нулевого потенциала.

2, Преобразователь по п.1, о т- личающийс я тем, что блок управления выполнен на шести D-триг- герах, дешифраторе, счетчике импульсов, генераторе импульсов, семи элементах И-НЕ, пяти инверторах, трех элементах задержки, формирователе импульсов, вход которого является первым входом блока управления, а выход соединен с первым входом первого элемента И-НЕ, выход которого через первый инвертор подключен к установочному входу первого D-триг- гера, информационный и тактовый входы которого соединены с пшной нулевого потенциала, а прямой выход подключен к входу запуска генератора импульсов, выход которого соединен со счетным входом счетчика импульсов, выходы которого подключены соответственно к входам дешифратора, первьй выход депифратора соединен с .первыми входами второго и третьего элементов И-НЕ, выходы которых соединены с входами соответственно второго и третьего инверторов, выходы которых являются соответственно первым и вторым выходами блока управления, второй выход дешифратора соединен с первыми входами четвертого и пятого элементов И-НЕ, выходы которы подключены к установочным входам соответственно второго и третьего D- триггеров, информационные и тактовые входы которых соединены с шиной нулевого потенциала, а выходы являются соответственно третьим и четвертым выходами блока управления, третий выход дешифратора соединен с первыми входами шестого и седьмого элементов И-НЕ, выходы которых соединены с входами соответственно четвертого и пятого инверторов, выходы ко5

TopF.rx ЯВЛЯЮТСЯ соответственно пятым и шестым выходами блока управления, четвертый выход дешифратора соединен с входом обнуления первого D-триггера и через первый элемент задержки -с входом обнуления счетчика импульсов, тактовые входы четвертого, пятого и шестого D-триггеров объединены с входом формирователя импульсов,установочные входы четвертого, пятого и шестого D-триггеров соединены с шиной питания, прямые выходы четвертого, пятого и шестого D-триггеров соединены с вторыми входами соответствен

но третьего, пятого и седьмого эле

ментов И-НЕ, информационные входы четвертого, пятого и шестого D-триггеров объединены со своими инверсными выходами и подключены к вторым входам соответственно второго, четвертого и шестого элементов И-НЕ, прямой выход шестого D-григгера соединен с входами второго и третьего элементов задержки, выход последнего из которых соединен с входами обнуления второго, третьего, четвертого, пятого и шестого D-триггеров и является седьмым выходом блока управления, выход второго элемента задержки соединен с вторым входом первого элемента И-НЕ, третий вход которого является вторым входом блока управления.

3. Преобразователь по п.1, о т личающийся тем, что блок адаптации выполнен на группе из ( 1) инверторов, где m - число разрядов выходного кода устройства, группе из ( 1) элементов И-НЕ, пяти элементах И-НЕ, двух D-триггерах, трех инверторах,генераторе импульсов, дешифраторе, с четчике импульсов, выходы которого соответственно подключены к входам дешифратора, а счетный вход соединен с выходом генератора импульсов, вход запуска которого соединен с прямым выходом первот го D-триггера, инверсный выход и 1шформационньгй вход которого объеди-

нены, установочный вход подсоединен к шине питания, а тактовый вход соединен с выходом первого элемента И-НЕ, входы которого через первый и второй инверторы соединены с выходамч соответственно второго и третьего элементов И-НЕ и являются соответственно третьим и вторым выходами блока адаптации, в::одов группы из .

( 1) инверторов соответственно объединены с входами второго элемента И- НЕ и являются информационными

входами младших разрядов блока адаптации, входы ( 1) группы из ( 1) инверторов сооответствен- но объединены с входами третьего элемента И-НЕ и являются информационными входами ( - 1) старших разрядов блока адаптации, выходы группы из ( 1) инверторов соответственно соединены с первыми входами группы из ( 1) элементов И-НЕ, вторые входы которой соответственно

.соединены с выходами дешифратора, а выходы соединены с входами четвертого элемента И-HF,, выход которого через третий инвертор соединен с первым входом пятого элемента И-ПЕ, второй вход которого является информационным входом (2 - - 1) разряда блока адаптации, а выход подключен к тактовому входу второго D-тригге- ра, информационный вход и инверсный выход которого объединены, установочньй вХод подсоединен к шине питания, а прямой выход является первым выходом блока адаптации, входы обнуления первого, второго D-триггеров и счетчика импульсов объединены и являются

входом начальной установки блока адаптации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное кодирующее устройство | 1983 |

|

SU1166308A1 |

| Быстродействующий аналого-цифровой преобразователь | 1985 |

|

SU1254584A1 |

| Адаптивный аналого-цифровой преобразователь | 1986 |

|

SU1311028A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Преобразователь угол-код | 1988 |

|

SU1596461A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Цифровое устройство измерения параметров гармонических сигналов | 1984 |

|

SU1182425A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1261116A1 |

| Оптоэлектронный модуль | 1987 |

|

SU1444940A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для преобразования аналоговых сигналов в цифровой код. Цель изобретения - повы шение быстродействия аналого-цифро- пого преобразования. Аналого-цифровой преобразователь с сокращенным циклом кодирования содержит генератор 1 опорного напряжения, входной фазовращатель 2, блоки 3 и 4 фазовых компараторов, шифраторы 5 и 6, регистры 7 и 8 числа, дешифратор 9, блоки 10 и 11 компенсирующего тока, ключ 12, фазовращатель 13 смещения, блок 14 адаптации и. блок 15 управления. Введенньй блок 15 адаптации и использование форсированного режима компенсации входного аналогового сигнала позволили повысить быстродействие аналого-цифрового преобразователя за счет фиксирования момента компенсации. 2 з.п. ф-лы, 3 ил. О. сл

, . ii X. i

23

Фе/г. Z

::$

N

фиг.З

Составитель H.Капитанов Редактор н.Швьщкая Техред А.Кравчук Корректор Н.Король

Заказ 795/61 Тираж 902 Подписное ВНИИТШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Прочзводственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Bx.J {if.O }

| Измерительная техника, 1972, № 11, с.8-11 | |||

| Аналого-цифровой преобразователь | 1976 |

|

SU588631A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-15—Публикация

1985-07-01—Подача