Изобретение относится к технике передачи изображения и может быть использовано в устройствах для приема цифровых факсимильных сигналов.

Цель изобретения - повышение качества изображения.

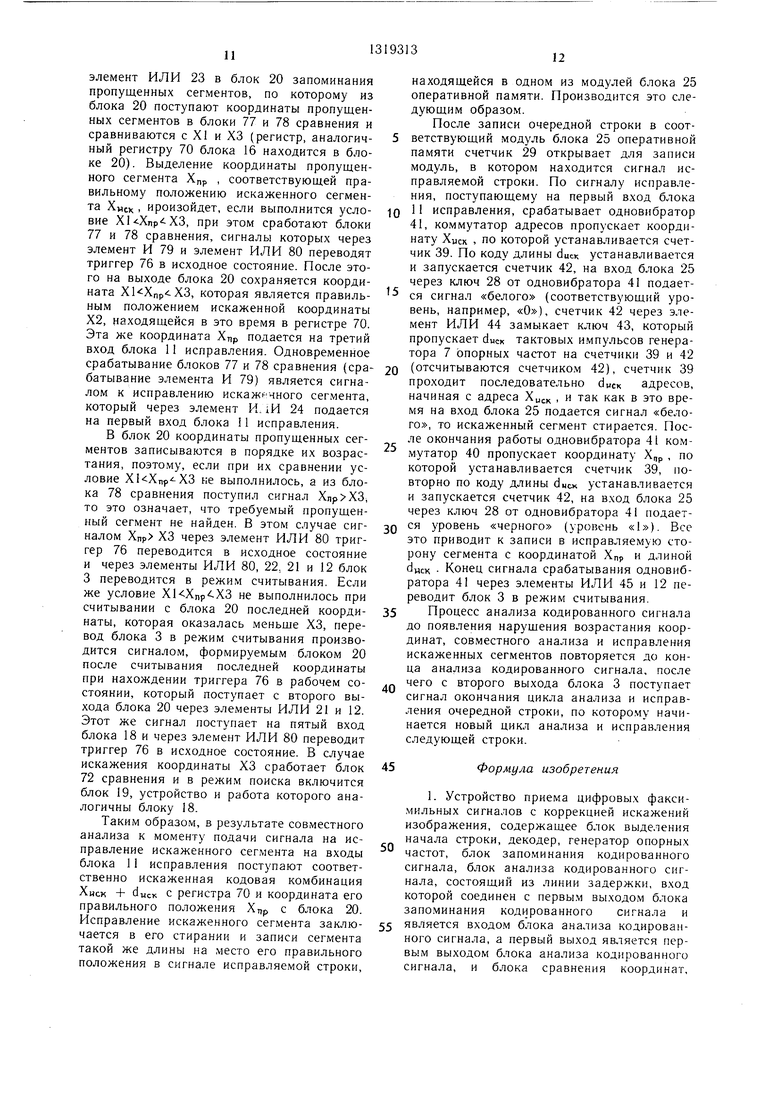

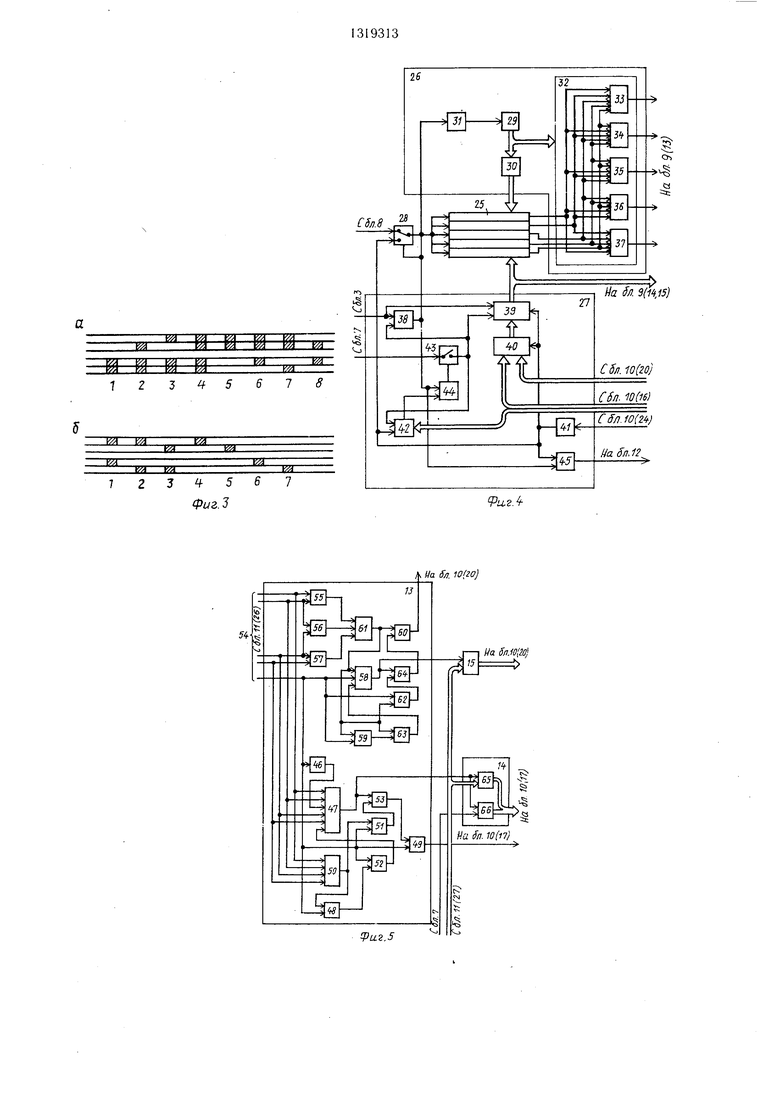

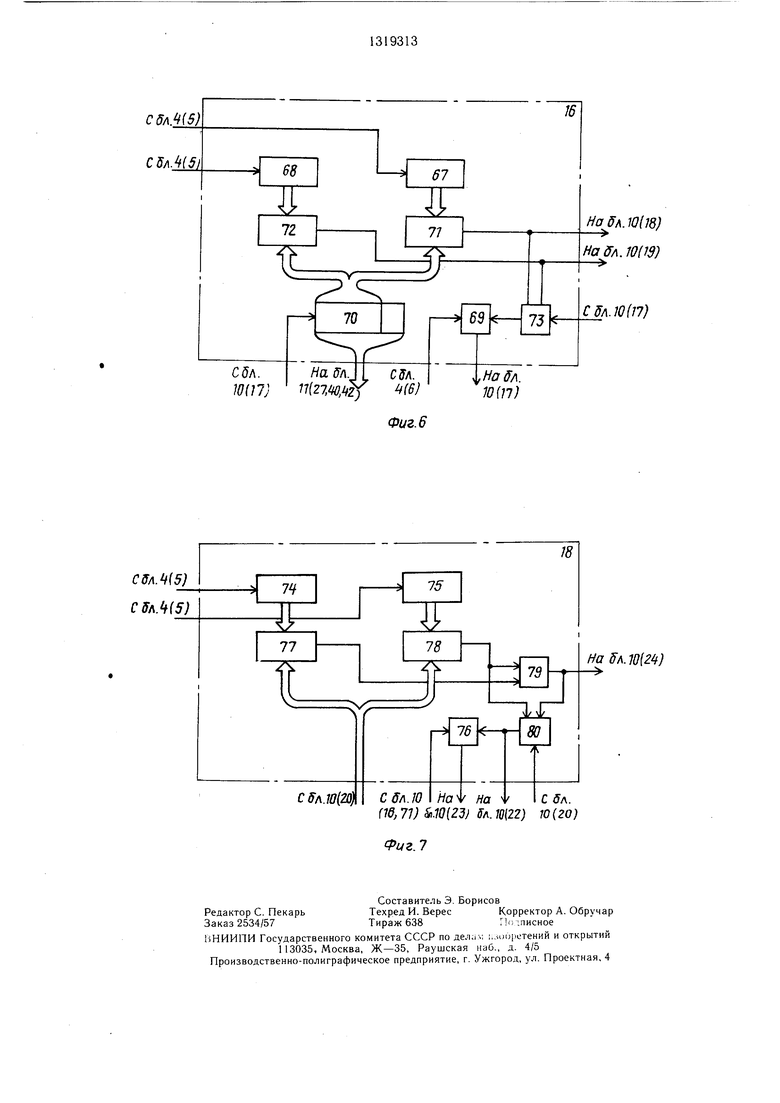

На фиг. 1 представлена электрическая структурная схема устройства приема цифровых факсимильных сигналов с коррекцией изображения; на фиг. 2 - расположение штрихов на участке изображения оригинала; на фиг. 3 - близкое к оптимальному распределение сегментов в штрихах; на фиг. 4 - схема блока исправления; на фиг. 5 - схема блока анализа декодированного сигнала; на фиг. 6 - схема блока определения искаженных координат; на фиг. 7 - схема блока определения пропущенных сегментов.

Устройство приема цифровых факсимильных сигналов с коррекцией изображений (фиг. 1) содержит блок 1 выделения начала строки, декодер 2, блок 3 запоминания кодированного сигнала, блок 4 анализа кодированного сигнала, состоящий из линии 5 задержки и блока 6 сравнения, генератор 7 опорных частот, блок 8 запоминания декодированного сигнала, блок 9 анализа декодированного сигнала, блок 10 совместного анализа, блок 11 исправления, элемент ИЛИ 12.

Блок 9 анализа декодированного сигнала (фиг. 1) содержит блок 13 выделения изолированных и пропущенных сегментов, блок 14 формирования кодовых комбинаций изолированных сегментов и блок 15 формирования координат пропущенных сегментов.

Блок 10 совместного анализа (фиг. 1) содержит блок 16 определения искаженных координат, блок 17 запоминания изолированных сегментов, первый и второй блоки 18 и 19 определения пропущенных сегментов, блок 20 запоминания пропущенных сегментов и с первого по четвертый элементы ИЛИ 21-24.

Блок И исправления (фиг. 1) содержит блок 25 оперативной памяти, блок 26 коммутации сигналов, блок 27 коммутации адресов, ключ 28.

Блок 11 исправления (фиг. 4) содержит счетчик 29, дешифратор 30, мультивибратор 31, блок 32 коммутации, состоящий из коммутаторов 33-37, счетчики 38 и 39, коммутатор 40, одновибратор 41, счетчик 42, ключ 43, элементы ИЛИ 44 и 45.

Блок 9 анализа декодированного сигнала (фиг. 5) содержит инвертор 46, элементы И 47-49, элементы ИЛИ 50 и 51, триггеры 52 и 53, группу входов 54, элементы И 55-60, элементы ИЛИ 61 и 62, триггеры 63 и 64, оперативное запоминающее устройство 65 и счетчик 66.

0

0

5

Блок 16 определения искаженных координат (фиг. 6) содержит регистры 67 и 68, триггер 69, регистр 70, блоки 71 и 72 сравнения, элемент ИЛИ 73.

Первый и второй блоки 18 и 19 определения пропущенных сегментов (фиг. 7) содержат регистры 74 и 75, триггер 76, блоки 77 и 78 сравнения, элемент И 79, элемент ИЛИ 80.

Устройство работает следующим образом.

Оно предназначено для приема факсимильного сигнала, кодированного коорди- натно-кодовым способом, состоящего из информационных кодовых комбинаций и сиг- 5 налов начала строки. Информационные кодовые комбинации, несущие информацию о положении и длине сегмента, содержат координату начала сегмента и код его длины. Сигналы начала строки, выделяемые блоком 1, предназначены для разделения общей последовательности сигнала на сигналы отдельных факсимильных строк. Характерной особенностью неискаженного сигнала является последовательное возрастание координат в пределах сигнала каждой отдельной факсимильной строки (фиг. 2,6).

Нарушение возрастания значения координат, выделяемое блоком 4 анализа кодированного сигнала, однозначно указывает на наличие искажений координат, но не дает количественной оценки искажения и неоднозначно указывает, какая координата искажена, так как искаженной может быть или координата, меньшая предыдущей (фиг. 2, а, координата Х5), или эта предыдущая (координата Х4).

Декодированный сигнал, запоминаемый блоком 8, - это сигнал, соответствующий неисправленному изображению копии (фиг. 2, е), и его анализ блоко.м 9 фактически является анализом изображения копии, для которого маловероятными являются случаи появления изолированных единичных черных сегментов на белом поле бланка и отсутствие единичных черных сегментов в штрихах изображения. Блок 9 анализа декодированного сигнала предназначен для выделения таких изолированных и пропущенных сегментов.

Сравнение результатов анализа кодированного и декодированного сигналов позволяет однозначно определить искаженные координаты и правильное положение соот- ветствующих им сегментов (фиг. 2, в, ). Например, при анализе кодированного сигнала определяется, что одна из координат Х4 или Х5 (пока неизвестно какая) искажена. Это означает, что правильное положение сегмента, соответствующего искаженной координате, находится между третьим и шестым сегментами. При анализе декодированного сигнала выявляется, что между тре0

5

0

5

5

тьим и шестым сегментами имеется один пропущенный пятый сегмент, на место которого должен быть смещен искаженный сегмент. Ааналогичным образом определяется второй искаженный сегмент и его правильное положение.

Таким образом, приведенное однозначное исправление положения второго и пятого сегментов возможно только при наличии результатов анализа как кодированного, так и некодированного сигналов и только при наличии предварительного запоминания кодированного и декодированного сигналов всего изображения или его части. Исследования показывают, что совместно с анализируемой строкой (средней на фиг. 2 е) достаточно анализировать две предыдущие и две последующие строки, так как дальнейщее увеличение числа анализируемых строк практически не увеличивает достоверность принимаемых решений. Близкое к оптимальному распределение сегментов в щтрихах представлено на фиг. 3 а, б.

Такой алгоритм приема и коррекции осуществляется следующим образом. Кодированный факсимильный сигнал поступает на вход блока 1 выделения сигнала начала строки, декодера 2 и блока 3 запоминания кодированного сигнала. Декодированный декодером 2 сигнал поступает на вход блока 8 запоминания декодированного сигнала. Блоки 3 и 8 запо.минают соответственно кодированный и декодированный сигналы построчно-построчное разделение сигналов обеспечивается блоком 1. После этого производится построчный анализ запомненных кодированного и декодированного сигналов блоками 4 и 9. Затем блоком Ю совместного анализа сравниваются результаты анализа кодированного и декодированного сиг- налов, что позволяет определить имеющиеся искажения и исправить положение искаженных сег.ментов блоком 11.

Анализ и исправление сигна.ча одной факсимильной строки производится следующим образом. Сначала производится анализ ее декодированного сигнала относительно сигналов двух предыдущих и двух последующих строк, записанных в блок 25 оперативной памяти блока 11 исправления. По сигналу окончания цикла анализа и исправления предыдущей строки, поступающему с второго выхода блока 3 запоминания кодированного сигнала, декодированный сигнал очередной строки с блока 8 через ключ 28 записывается в блок 25 оперативной памяти блока И. Блок 25 оперативной памяти представляет собой пять отдельных модулей, каждый емкостью на одну факсимильную строку декодированного сигнала. Объем сигнала декодированной строки постоянен и равен числу эле.ментарных площадок п, на которые разлагается факсимильная стро0

ка при анализе изображения. В зависимости от размеров бланка и требуемой разрешающей способности аппаратуры обычно значение тыс. При таком построении блока 25 легко обеспечить требуемый порядок записи и считывания информации. Текущий модуль блока 25 оперативной памяти, в который производится запись, определяют счетчик 29 и дещифратор 30, входящие в блок 26 коммутации сигналов. Де- Щифратор 30 устанавливает в состояние «Запись только один из пяти модулей в зависимости от состояния счетчика 29. Адрес (координата) с блока 27 коммутации адресов подается на все пять модулей бло5 ка 25 оперативной памяти одновременно. При этом производится запись в ячейку одного модуля, определяемого счетчиком 29, а с выходов всех пяти модулей памяти считывается одновременно информация (в том

, числе и только что записанная) со всех пяти ячеек, соответствующих адресу, и через блок 32 коммутации подается в блок 9 анализа декодированного сигнала. Блок 32 ко.ммутации тоже управляется счетчиком 29. В модули блока 25 оперативной памяти

5 записываются пять идущих подряд строк. Пусть очередной исправляемой строкой будет строка К, записанная в третий модуль. Только во второй и в первый модули будут записаны две предыдущие (К-1 и К-2) строки, в четвертый модуль - первая последующая (К+ I) строка, а в пятый модуль будет записываться очередная вторая последующая (К+2) строка вместо ранее записанной (К-3), которая была второй предыдущей при исправлении К-1 строки (предыдущий цикл). При записи в пятый модуль счетчик 29 находится в состоянии «5. В следующем цикле будет исправляться (К+1)-я строка, записанная в четвертый модуль. В третьем и четвертом модулях будут находиться две предыдущие по от- нощению к ней строки (К и К-1), в пятом модуле - первая последующая (К+2), а в первом модуле будет записана вторая последующая (К+3 вместо К-2) строка. Таким, образом, участвующие в анализе

5 декодированного сигнала строки с каждым последующим цикло.м сдвигаются на один модуль оперативной памяти и, следовательно, выходы модулей, содержащие исправляемую, предыдущие и последующие строки меняются от цикла к циклу. Блок 32 коммутации коммутирует выходы модч лей таки.м образо.м, чтобы к одному из его выходов постоянно был подключен выход модуля, содержащий исправляемую строку, к второму выходу - содержащий первую предыдущую строку и т.д. Выходы всех модулей блока 25 подключены к входам всех коммутаторов 33-37 блока 32 коммутации. Для следующего цикла (запись К+3, исправ0

5

0

0

5

ление Кч-1 строк, состояние «1 счетчика 29) первый коммутатор 33 пропускает сигнал с выхода второго модуля и т.д. Счетчик 29 изменяет свое состояние каждый раз на три значения тремя импульсами, сформированными запускаемым на время их формирования мультивибратором 31 от обоих фронтов сигнала, поступающего на его вход со счетчика 38 блока 27 коммутации адресов.

Блок 27 коммутации адресов работает следующим образом. Непосредственно формирование адресов, поступающих в блок 25. оперативной памяти, производится счетчиком 39, который может быть установлен в нулевое или любое другое начальное состояние. Обнуление счетчика 39 производится сигналом окончания цикла анализа и исправления строки, поступающим с блока 3, а его установка в любое состояние, определяемое состоянием выходов коммутатора 40, производится обоими фронтами сигнала одновибратора 41 (в начале и конце его срабатывания). На вход блока 11 исправления поступает кодовая комбинация (координата Хцск и код длины ducK ) искаженного сегмента и координата Хпр правильного положения этого сегмента. В коммутатор 40 поступают одновременно обе координаты XUCK и Х„р , являющиеся одно

вре.менно адресом оперативной памяти. Кодовые комбинации и координаты поступают параллельно. На выходе коммутатора 40 будет координата искаженного сегмента нск во вре.мя срабатывания одновибратора 41, которая записывается в качестве начального состояния счетчика 39 в начале срабатывания одновибратора 41, а после окончания его работы - координата правильного положения сегмента , которая тоже устанавливает счетчик 39 в начальное состояние окончанием срабатывания одно- вибратора 41 (задним фронтом его импульса). Также начала и окончание срабатывания одновибратора 41 устанавливает кодо.м длины искаженного сегмента в начальное состояние счетчик 42 и запускает его. Останавливается счетчик 42 после поступления на его вход числа импульсов, равного длине сегмента (задается кодом длины с1нск), поступающих с ключа 43 управляющего элементом ИЛИ 44. Ключ 43 замкнут во время работы счетчика 38 или счетчика 42. Сигналы конца срабатывания счетчика 38 (конец записи очередной строки в оперативную память) и конца срабатывания одно- вибратора 41 (заканчивается исправление очередного сегмента) через элемент И/1И 45 и элемент ИЛИ 12 подаются на третий вход блока 3, по которым начинается или продолжается анализ кодированного сигнала и совместный анализ сигнала исправляемой строки.

Сигналом окончания предыдущего и начала очередного цикла является сигнал, поступающий с второго выхода блока 3 за- поминания кодированного сигнала на первый вход блока 8 запоминания декодированного сигнала и на пятый вход блока 11 исправления, по которому блок 8 начинает считывать, а блок 11 записывать по условиям, приведенным ранее, (K-f 2)-ю строку, в пятый модуль блока 25 оперативной памяти. Этим сигналом запускается счетчик 38, началом срабатывания которого запускается мультивибратор 31, который переводит счетчик 29 в состояние «5. В результате открывается для записи пятый модуль блока 25. Кроме того, сработавший счетчик 38 переводит ключ 28 в положение,, при ко- торо.м вход блока 25 оперативной памяти подключается к выходу блока 8, и через элемент ИЛИ 44 замыкает ключ 43 на вре.мя прохождения с генератора 7 опорных частот п импульсов, которые поступают на входы счетчиков 38 и 39. Счетчик 39 формирует п последовательных адресов - производится запись п бит декодированного сигнала (К+2)-й строки в п ячеек пятого

модуля блока 25 оперативной памяти. Одновременно с последовательной записью сигнала в пятый модуль производится считывание сигналов во всех модулей блока 25 оперативной па.мяти (в том числе и К+2 строки), которые поступают .через блок 32 коммутации с выходов блока 11 в блок 9, который в процессе их поступления производит анализ декодированного сигнала К-й строки. После прохождения через ключ 43 п импульсов счетчик 38 прекращает работу, размыкает ключ 43, переводит ключ 28 в

положение, при котором вход блока 25 оперативной памяти подключается к выходу одновибратора 41, запускает мультивибратор 31, который переводит счетчик 29 в состояние «3.

После исправления К-й строки в начале следующего цикла при запуске счетчика 38 счетчик 29 будет переведен в состояние «1, следующая (К+3)-я строка запищется в первый модуль блока 25 оперативной памяти, а после прекращения работы счетчика 38 счетчик 29 перейдет в состояние «4. В результате откроется вход четвертого модуля блока 25 оперативной памяти для исправления записанного в него сигнала (К+ 1) -и строки.

Анализ декодированного сигнала очередной строки, выполняемый блоком 9, заключается в выделении изолированных (искаженных) сегментов и формировании соответствующих им кодовых комбинаций (ко- ординаты Хмск и кода длины ducKJ и выделении пропущенных сегментов (правильных положений искаженных сегментов) и формировании соответствующих им координат ХЛР .

Этот анализ осуществляется относительно двух предыдущих и двух последующих строк. С блока 11 исправления на входы блока 9 поступают поэлементно декодированные сигналы пяти строк - анализируемой, двух предыдущих и двух последующих. Причем все пять элементов, поступающих в любой момент на блок 9, имеют одну и ту же координату, которая поступает с блока 11 на вход блока 9. Будем считать, что сегмент изображения изолированный, если он имеется на анализируемой строке (фиг. 2, е) и на всем его протяжении на остальных строках отсутствуют элементы «черного. Пропущенным сегментом будем считать отсутствие элементов «черного на анализируе- .мой строке на всем протяжении щтриха.

Блок 9 работает следующим образом. Выделение изолированных сегментов производится схемой, содержащей инвертор 46, три элемента И 47-49, два элемента ИЛИ 50 и 51 и два триггера 52 и 53. Элемент И 47 срабатывает при поступлении на вход блока 13, по которому подается сигнал анализируемой строки сигнала «черного, а на все остальные входы - сигнала «белого, если триггер 52 находится в исходном состоянии. При срабатывании элемента И 47 подается сигнал на первый вход блока 14 формирования кодовой комбинации изолированного сегмента, по которому его оперативное запоминающее устройство 65 запоминает координату начала изолированного сегмента, и запускается счетчик 66 длины этого сегмента. Элемент ИЛИ 50 срабатывает, если хотя бы на одном из ее входов появится сигнал «черного. Элемент И 48 срабатывает, если сработали элемент ИЛИ 50 и в сигнале анализируемой строки имеется сигнал «черного. Элемент И 49 пропускает переход сигнала анализируемой строки от «черного к «белому (конец сегмента), если триггер 53 находится в рабочем состоянии. Этот переход является сигналом, по которому блок 17 запоминания изолированных сегментов записывает подготовленную блоком 14 кодовую комбинацию изолированного сегмента - координату из оперативного запоминающего устройства 65 и длину со счетчика 66.

С появлением в сигнале анализируемой строки изолированного сегмента срабатывает элемент И 47 н его координата запоминается оперативным запоминающим устройством 65. Начинается счет длины сегмента счетчиком 66 (счет импульсов генератора 7 опорных частот) и срабатывает триггер 53. Так как триггер 53 остается в рабочем состоянии, то в момент окончания сегмента (перехода сигнала от «черного к «белому) через элемент И 49 в блок 17 поступает сигнал на запись подготовленной блоком 14

0

5

0

5

0

5

0

5

0

5

кодовой комбинации, после чего сигналом «белого анализируемой строки вся схема выделения сегмента переводится и удерживается в исходном состоянии.

При прохождении неизолированного сегмента тоже могут быть ситуации, когда на остальных строках все элементы «белые. Если такая ситуация возникнет в начале сегмента, то сработают элемент И 47 и триггер 53 и начнется формирование кодовой комбинации блоком 14, но при появлении на каком-либо из остальных входов сигнала «черного сработает элемент ИЛИ 50, который через элемент ИЛИ 51 переведет триггер 53 в исходное состояние. Прохождение сигнала на запись кодовой комбинации в блок 17 прекратится. Если же в начале сегмента на остальных входах имеется сигнал «черного, то сработает элемент ИЛИ 50, элемент И 48 и триггер 52, который запретит срабатывание элемента И 47 при появлении указанной ситуации в конце сегмента. Емкость оперативного запоминающего устройства 65 на одну координату (10-12 бит) нужна для запоминания координаты только до момента ее записи в блок 17.

Схема, выделяющая пропущенные сег- .менты, включает щесть элементов И 55-60, два элемента ИЛИ 61 и 62 и два триггера

63и 64. При появлении пропущенного сегмента возникает одна из ситуаций, приведенных на фиг. 3 а, что приводит к срабатыванию не менее, чем одного из элементов И 55-57, элемента ИЛИ 61, элемента И 58 и триггера 64. Элемент И 58 срабатывает при срабатывании элемента -ИЛИ 61, сигнале «белого в анализируемой строке и нахождении триггера 63 в исходном состоянии. Его срабатывание является сигналом для запоминания координаты начала пропущенного сегмента блоком 15, который представляет собой такое же устройство, как и оперативное запоминающее устройство 65. Сигналом записи координаты Хпр в блок 20 запоминания пропущенных сегментов является конец срабатывания элемента ИЛИ 61. который проходит через элемент И 60, так как триггер 64 находится в рабочем состоянии. Этим же сигналом вся схема выделения пропущенных сегментов переводится в исходное состояние (триггеры 63 и 64). Срабатывание элемента ИЛИ 61 при наличии в анализируемой строке сигнала «белого может иметь место и в случае отсутствия пропуска сегмента - сегмент начался после начала или закончился раньще конца срабатывания элемента ИЛИ 61. Если сегмент начинается позже, то происходит срабатывание элемента ИЛИ 61, элемента И 58, триггера

64и блок 15 запоминает координату, но как только начнется сегмент, переведутся в исходное состояние элемент И 58 и тригrep 64 (через элемент ИЛИ 62) - координата в блок 20 не запишется. Если же в начале срабатывания элемента ИЛИ 61 уже имеется сегмент, то срабатывает элемент И 59 (срабатывание элемента ИЛИ 61 и наличие в анализируемой строке «черного) и сработает триггер 63, который не позволит сработать элементу И 58, если сегмент закончится раньше конца срабатывания элемента ИЛИ 61.

Сигналом окончания анализа декодированного сигнала очередной строки является окончание работы счетчика 38 блока 11, который через элементы ИЛИ 45 и 12 поступает на четвертый вход блока 3, по которому он начинает поочередно считывать кодовые комбинации анализируемой строки в том же порядке, в котором они поступали с канала связи. С этого момента начинается анализ кодированного сигнала, выполняемый блоком 4, который определяет наличие в сигнале кодовых комбинаций с искаженными координатами. С конечного и промежуточных выходов, а также с входа линии 5 задержки выделяются сигналы со сдвигом на одну кодовую комбинацию («длина линии задержки на три кодовые комбинации), т.е. в этих точках выделяются одновременно четыре следующие друг за другом кодовые комбинации, которые поступают на блок 10 совместного анализа. Обозначим их значения в порядке поступления в блок 4 XI, Х2, ХЗ и Х4 (XI с выхода линии 5 задержки; а Х4 - с ее входа). При отсутствии искажений . Координаты Х2 и ХЗ, выделяемые на промежуточных выходах линии задержки, сравниваются блоком 6, который при нарушении возрастания координат (при ) формирует сигнал, свидетельствующий о том, что по крайней мере одна из двух сравниваемых координат (пока неизвестно какая) искажена. Этот сигнал также поступает на блок 10. Считывание кодовых комбинаций с блока 3 производится непрерывно до тех пор, пока не появится нарушение возрастания координат. При этом сигнал с выхода блока 6 сравнения координат поступает на третий вход блока 3, по которому считывание кодовых комбинаций прекращается. С этого момента начинается совместный анализ кодированного и декодированного сигналов, выполняемый блоком 10, который определяет, какая из координат Х2 или ХЗ искажена и какой пропущенный сегмент соответствует ее правильному положению. Производится это следующим образом.

Координаты Х2 и ХЗ с промежуточных выходов линии 5 задержки все время записываются соответственно в регистры 67 и 68. При нарушении возрастания координат по сигналу с блока 6 прекращается по

10

15

20

25

30

35

40

45

50

55

10

дача кодовых комбинаций с блока 3 и, следовательно, прекращается их продвижение через линию 5 задержки и регистры 67 и

68- в регистрах 67 и 68 остаются кодовые комбинации с координатами Х2 и ХЗ, одна из которых искажена. Кроме того, сигнал с блока 6 переводит триггер 69 в рабочее состояние, при котором с его выхода поступает сигнал на блок 17 запоминания кодовых комбинаций изолированных сегментов. По этому сигналу с блока 17 начинают поочередно поступать кодовые комбинации изолированных сегментов в регистр 70, а их координаты , сравниваться с Х2 и ХЗ блоками 71 и 72 сравнения. При совпадении значения одной из координат, поступающих с блока 17, со значением Х2 из блока 71 сравнения они поступают на третий вход блока 18, а при совпадении со значениями ХЗ - из блока 72 сравнения на третий вход блока 19. Кроме того, срабатывание одного из блоков 71 или 72 сравнения терез элемент ИЛИ 73 переводит триггер

69в исходное состояние. Подача кодовых комбинаций с блока 17 прекращается, на регистре 70 остается кодовая комбинация искаженного сегмента, которая поступает также в коммутатор 40 (координата) и счетчик 42 (код длины) блока 11 исправления.

Если все координаты, запомненные блоком 17, пройдут через регистр 70 и ни один из блоков 71 и 72 сравнения не сработает, это означает, что искаженный сегмент не определен и исправление не производится. В этом случае после выхода кодовой ком- .бинации с блока 17 при рабочем состоянии триггера 69 с блока 17 поступает сигнал в элемент ИЛИ 73, по которому триггер 69 переводится в исходное состояние. Этот же сигнал через элементы ИЛИ 21 и 12 поступает на блок 3 и переводит его в режим считывания кодированного сигнала, т.е. к продолжению анализа кодированного сигнала.

Срабатывание одного из блоков 71 или 72 сравнения является сигналом к поиску пропущенного сегмента, соответствующего правильному положению искаженного сегмента, кодовая комбинация которого находится в регистре 70. Этot поиск выполняется одним из блоков 18 или 19 определения пропущенных сегментов. Срабатывание блока 71 означает, что искаженной координатой является координата Х2, неискаженное значение которой находится между значениями предыдущей XI и последующей ХЗ координатами, которые в это время находятся соответственно в регистрах 74 и 75 блока I8.

Сигнал из блока 71 устанавливает в режим поиска блок 18. Этот сигнал переводит триггер 76 в рабочее состояние, при котором с его выхода поступает сигнал через

элемент ИЛИ 23 в блок 20 запоминания пропущенных сегментов, по которому из блока 20 поступают координаты пропущенных сегментов в блоки 77 и 78 сравнения и сравниваются с XI и ХЗ (регистр, аналогичный регистру 70 блока 16 находится в блоке 20). Выделение координаты пропущенного сегмента Хпр , соответствующей правильному положению искаженного сегмента Хмсх I ироизойдет, если выполнится условие Xl-iXnp X3, при этом сработают блоки 77 и 78 сравнения, сигналы которых через элемент И 79 и элемент ИЛИ 80 переводят триггер 76 в исходное состояние. После этого на выходе блока 20 сохраняется координата ХиХпр ХЗ, которая является правильным положением искаженной координаты Х2, находящейся в это время в регистре 70. Эта же координата подается на третий вход блока 11 исправления. Одновременное срабатывание блоков 77 и 78 сравнения (срабатывание элемента И 79) является сигналом к исправлению искаженного сегмента, который через элемент И. хИ 24 подается на первый вход блока 11 исправления.

В блок 20 координаты пропущенных сегментов записываются в порядке их возрастания, поэтому, если при их сравнении условие не выполнилось, а из блока 78 сравнения поступил сигнал , то это означает, что требуемый пропущенный сегмент не найден. В этом случае сигналом ХПР ХЗ через элемент ИЛИ 80 триггер 76 переводится в исходное состояние и через элементы ИЛИ 80, 22, 21 и 12 блок 3 переводится в режим считывания. Если же условие ХКХпр ХЗ не выполнилось при считывании с блока 20 последней координаты, которая оказалась меньше ХЗ, перевод блока 3 в режим считывания производится сигналом, формируемым блоком 20 после считывания последней координаты при нахождении триггера 76 в рабочем состоянии, который поступает с второго выхода блока 20 через элементы ИЛИ 21 и 12. Этот же сигнал поступает на пятый вход блока 18 и через элемент ИЛИ 80 переводит триггер 76 в исходное состояние. В случае искажения координаты ХЗ сработает блок 72 сравнения и в режим поиска включится блок 19, устройство и работа которого аналогичны блоку 18.

Таким образом, в результате совместного анализа к моменту подачи сигнала на исправление искаженного сегмента на входы блока 11 исправления поступают соответственно искаженная кодовая комбинация Хнск + diicK с регистра 70 и координата его правильного положения Хпр с блока 20. Исправление искаженного сегмента заключается в его стирании и записи сегмента такой же длины на место его правильного положения в сигнале исправляемой строки.

находящейся в одном из модулей блока 25 оперативной памяти. Производится это следующим образо.м.

После записи очередной строки в соответствующий модуль блока 25 оперативной памяти счетчик 29 открывает для записи модуль, в котором находится сигнал исправляемой строки. По сигналу исправления, поступающему на первый вход блока

0 11 исправления, срабатывает одновибратор 41, коммутатор адресов пропускает координату XUCK , по которой устанавливается счетчик 39. По коду длины ducx устанавливается и запускается счетчик 42, на вход блока 25 через ключ 28 от одновибратора 41 подает5 ся сигнал «белого (соответствующий уровень, например, «О), счетчик 42 через элемент ИЛИ 44 замыкает ключ 43, который пропускает ducK тактовых и.мпульсов генератора 7 опорных частот на счетчики 39 и 42

0 (отсчитываются счетчиком 42), счетчик 39 проходит последовательно dwcK адресов, начиная с адреса Хуск . так как в это время на вход блока 25 подается сигнал «белого, то искаженный сегмент стирается. После окончания работы одновибратора 41 ком мутатор 40 пропускает координату Х„р , по которой устанавливается счетчик 39, повторно по коду длины ducK устанавливается и запускается счетчик 42, на вход блока 25 через ключ 28 от одновибратора 41 подаетQ ся уровень «черного (уровень «1). Все это приводит к записи в исправляемую сторону сегмента с координатой Хпр и длиной dwcK Конец сигнала срабатывания одновибратора 41 через элементы ИЛИ 45 и 12 переводит блок 3 в режим считывания.

5 Процесс анализа кодированного сигнала до появления нарушения возрастания координат, совместного анализа и исправления искаженных сегментов повторяется до конца анализа кодированного сигнала, после

чего с второго выхода блока 3 поступает сигнал окончания цикла анализа и исправления очередной строки, по которо.му начинается новый цикл анализа и исправления следующей строки.

45

Формула изобретения

1. Устройство приема цифровых факсимильных сигналов с коррекцией искажений изображения, содержащее блок выделения начала строки, декодер, генератор опорных частот, блок запоминания кодированного сигнала, блок анализа кодированного сигнала, состоящий из линии задержки, вход которой соединен с первым выходом блока запоминания кодированного сигнала и является входо.м блока анализа кодированного сигнала, а первый выход является первым выходом блока анализа кодированного сигнала, и блока сравнения координат.

выход которого является вторым выходом блока анализа кодированного сигнала, а первый и второй входы являются третьим и четвертым выходами блока анализа кодированного сигнала и соединены соответственно с вторым и третьим выходами линии задержки, при этом первый вход блока запоминания кодированного сигнала и входы блока выделения начала строки и декодера объединены и являются входом устройства, выход блока выделения начала строки соединен с вторым входом блока запоминания кодированного сигнала, третий вход которого соединен с вторым выходом блока анализа кодированного сигнала, отличающееся тем, что, с целью повышения качества изображения, введены блок анализа декодированного сигнала, блок исправления, блок совместного анализа, элемент ИЛИ и блок запоминания декодированного сигнала, при этом первый, второй, третий и четвертый входы блока совместного анализа соединены соответственно с первым, третьим, четвертым и вторым выходами блока анализа кодированного сигнала, пятый вход соединен с первым выходом блока запоминания кодированного сигнала, шестой, седьмой, восьмой и девятый входы соединены соответственно с первым, вторым, третьим и четвертым выходами блока анализа декодированного сигнала, первый выход соединен с первым входом элемента ИЛИ, а второй, третий и четвертый выходы соединены соответственно с первым вторым и третьим входами блока исправления, первый выход которого соединен с вторым входом элемента ИЛИ, выход которого соединен с четвертым входом блока запоминания кодированного сигнала, первый и второй входы блока анализа декодированного сигнала соединены соответственно с выходом генератора опорных частот и с вторым выходом блока исправления, четвертый, пятый и шестой входы которого соединены соответственно с выходом генератора опорных частот, с вторым выходом блока запоминания кодированного сигнала и с выходом блока запоминания декодированного сигнала, первый, второй, третий входы которого соединены соответственно с вторым выходом бло,ка запоминания кодированного сигнала, выходом блока выделения сигнала начала строки и выходом декодера, а группа выходов блока исправления соединена с группой входов блока анализа декодированного сигнала.

2. Устройство по п. 1, отличающееся тем, что блок анализа декодированного сигнала содержит блок выделения изолированных и пропущенных сегментов, первый и второй выходы которого являются первым и третьим выходами блока анализа декодированного сигнала, а группа входов является

0

5

0

5

0

5

0

5

0

5

группой входов блока анализа декодированного сигнала, блок формирования координат пропущенных сегментов, первый вход которого соединен с третьим выходом блока выделения изолированных и пропущенных сегментов, а выход является четвертым выходом блока анализа декодированного сигнала, и блок формирования кодовых комбинаций изолированных сегментов, первый вход которого соединен с четвертым выходом блока выделения изолированных и пропущенных сегментов, второй вход является первым входом блока анализа декодированного сигнала, третий вход объединен с вторым входом блока формирования координат пропущенных сегментов и является вторым входом блока анализе декодированного сигнала, а выход является вторым выходом блока анализа декодированного сигнала. Блок совместного анализа содержит блок определения искаженных координат, первый, второй и третий входы которого являются соответственно вторым, третьим и четвертым входами блока совместного анализа, блок запоминания изолированных сегментов, первый вход которого соединен с первым выходом блока определения искаженных координат, второй и третий входы являются шестым и седьмым входами блока совместного анализа, а первый и второй выходы соединены соответственно с четвертым и пятым входами блока определения искаженных координат, первый блок определения пропущенных сегментов, первый и второй входы которого являются соответственно первым и третьим входами блока совместного анализа, а третий вход соединен с вторым выходом блока определения искаженных координат, второй блок определения пропущенных сегментов, первый вход которого объединен с первым входом блока определения искаженных координат, второй вход является пятым входом блока совместного анализа, а третий вход соединен с третьим выходом блока определения искаженных координат, блок запоминания пропущенных сегментов, первый и второй входы которого являются восьмым и девятым входами блока совместного анализа, а первый выход соединен с четвертыми входами первого и второго блоков определения пропущенных сегментов и является четвертым выходом блока совместного анализа, первый элемент ИЛИ, первый и второй входы которого соединены соответственно с вторым выходом блока запоминания изолированных сегментов и с вторым выходом блока запоминания пропущенных сегментов, объединенного с пятыми входами первого и второго блоков определения пропущенных сегментов, второй элемент ИЛИ, первый и второй входы которого соединены с первыми выходами соответственно первого

и второго блоков определения пропущенных сегментов, а выход соединен с третьим входом первого элемента ИЛИ, выход которого является первым выходом блока совместного анализа, третий элемент ИЛИ, первый и второй входы которого соединены с вторыми выходами соответственно первого и второ- го блоков определения пропущенных сегментов, а выход соединен с третьим входом блока запоминания пропущенных сегментов, и четвертый элемент ИЛИ, первый и второй входы которого соединены с третьими выходами соответственно первого и второго блоков определения пропущенных сегментов, а выход является вторым выходом блока совместного анализа, четвертый выход блока определения искаженных координат является третьим выходом блока совместного анализа.

3. Устройство по п. 1, отличающееся тем, что блок исправления содержит ключ, первый вход которого является щестым входом блока исправления, блок коммутации сигналов, группа выходов которого является группой выходов блока исправления, блок оперативной памяти, группа выходов которого соединена с группой входов блока коммутации сигналов, первый вход блока оперативной памяти соединен с выходом, ключа, а второй вход соединен с выходом блока коммутации сигналов, и блок коммутации адресов, первый, второй, третий, четвертый и пятый ходы которого являются первым, вторым третьим, четвертым и пятым входами блока исправления, первый выход является первым выходом блока исправления, второй выход соединен с третьим входом блока оперативной памяти и является вторым выходом блока исправления, третий выход соединен с вторым входом ключа, а четвертый выход соединен с третьим входом ключа и с входом блока коммутации сигналов.

/

/

, ,.-1/Л/|/ OI J

. nymi, развертывающего элемента

1 { f f r r r

Ь .y...,./ .,-. .X. .7 xa f9

//ЛУ//ЛУ/7ЛУ//ЛУ/7АУ//А 7/-ЛУ/Л // У//Л У//Л lIiIII

I I I I I I I I

Канал связи. II I I I I I I

г ..A...У...t...........f...t...,.. t ..

Y//A V/M Y//A У//Л У//Л У//Л У//Л V// У//Л У7/Л V//X }

М г ХЗ Х4 Х5 ХВ Х7 ХВ Х9 } -} --Ь// / :-/ -- - -Г:

/ I

Пут раз5ертиваю14его э емент

I I

Пут раз5ертиваю14его э емент

а

Фиг.З

9и,г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ приема координатно-кодово кодированных цифровых факсимильных сигналов | 1982 |

|

SU1172070A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Устройство для кодирования и декодирования цифрового телевизионного сигнала | 1988 |

|

SU1566485A1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОГО СООБЩЕНИЯ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2179365C1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ДЛЯ ПРЕОБРАЗОВАНИЯ СЖАТЫХ ДАННЫХ, ПРЕДСТАВЛЯЮЩИХ ИЗОБРАЖЕНИЯ И РАЗМЕЩЕННЫХ В БЛОКАХ, В НЕСЖАТЫЕ ДАННЫЕ И СИСТЕМА ДЛЯ ОБРАБОТКИ СЖАТЫХ ВИДЕОДАННЫХ, ПЕРЕДАВАЕМЫХ В ВИДЕ БЛОКОВ | 1992 |

|

RU2119269C1 |

| Устройство передачи и приема сигнала изображения | 1986 |

|

SU1438020A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ ВИДЕОСИГНАЛА, ПРЕДСТАВЛЯЮЩЕГО ИЗОБРАЖЕНИЯ, ПРИЕМНИК ТЕЛЕВИЗИОННОГО СИГНАЛА, ВКЛЮЧАЮЩЕГО ДАННЫЕ ЗАГОЛОВКОВ И ПОЛЕЗНЫЕ ДАННЫЕ В ВИДЕ СЖАТЫХ ВИДЕОДАННЫХ | 1992 |

|

RU2128405C1 |

| Способ передачи факсимильных изображений с распознаванием символов | 1989 |

|

SU1695510A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для исправления ошибок при итеративном кодировании | 1977 |

|

SU680061A2 |

Изобретение относится к те.хнике передачи изображения и повышает качество изображения. Устр-во содержит блок 1 выделения начала строки, декодер 2, блок 3 запо.минания кодированного сигнала, блок 4 анализа кодированного сигнала, состоящий из линии задержки 5 и блока 6 сравнения, г-р 7 опорных частот. Вновь введены блок 8 запоминания декодированного сигнала, блок 9 анализа декодированного сигнала, блок 10 совместного анализа, блок 11 исправления, эл-т ИЛИ 12. 2 з.п. ф-лы, 7 ил. П . (Л со QO со со

k На 5л. 10(20)

VLLZ.S

Составитель Э. Борисов Техред И. ВересКорректор А. Обручар

,Тираж 638Г :. шисное

ВНИШ1Й государственного комитета СССР по деж.;., 1,,«,о1)етений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Редактор С. Пекарь Заказ 2534/57

(16,71) Sr.10i23} Ил. W{22) ю(го) Фиг.7

| Система передачи штриховых изображений с обнаружением и исправлением ошибок | 1980 |

|

SU907867A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство приема сигналов изображения | 1980 |

|

SU944157A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-23—Публикация

1985-10-10—Подача