ел

ОЭ

о

4 00

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования и обработки широкополосных сигналов | 2018 |

|

RU2691733C1 |

| Кодер сигнала изображения | 1990 |

|

SU1730724A1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| Кодер видеосигнала | 1987 |

|

SU1506554A1 |

| Устройство для телевизионной игры | 1977 |

|

SU736992A1 |

| Устройство для кодирования и декодирования телевизионного сигнала | 1988 |

|

SU1649674A1 |

| Система передачи цифровой информации | 1990 |

|

SU1786679A1 |

| Запоминающее устройство для телевизионного изображения | 1985 |

|

SU1265785A1 |

| Устройство для сжатия и передачи телеметрической информации | 1987 |

|

SU1640729A1 |

| Кодек блочного кода | 1985 |

|

SU1358098A1 |

Изобретение относится к технике связи и вычислительной технике. Его использование в цифровых телевизионных системах с передачей или видеозаписью сигналов методом импульсно-кодовой модуляции позволяет повысить информативность устройства без снижения помехоустойчивости кодированного сигнала и без потери качества передаваемого изображения. Устройство содержит в кодере аналого-цифровой преобразователь 1, преобразователь 2 последовательного кода в параллельный, блок 3 суммирования по модулю два и преобразователь 7 параллельного кода в последовательный, в декодере - входной регистр, мультиплексор, блок сумирования по модулю два, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и цифроаналоговый преобразователь. Благодаря введению в кодер блока 4 мультиплексирования, генератора 5 псевдослучайной последовательности и дешифратора 6, а в декодер- генератора псевдослучайной последовательности, мультиплексора, триггера и узла задержки обеспечивается размещение бита контроля четности на месте одного из младших разрядов по псевдослучайному закону. 1 з.п. ф-лы, 3 ил.

Фиг. Г

Изобретение относится к технике связи и вычислительной технике и может быть использовано в цифровых телевизионных системах с передачей или видеозаписью сигналов методом импульс но-кодовой модуляции (ИКМ).

Целью изобрети -ия является повышение информативности устройства без снижения помехоустойчивости кодированного сигнала и без потери качества передаваемого изображения.

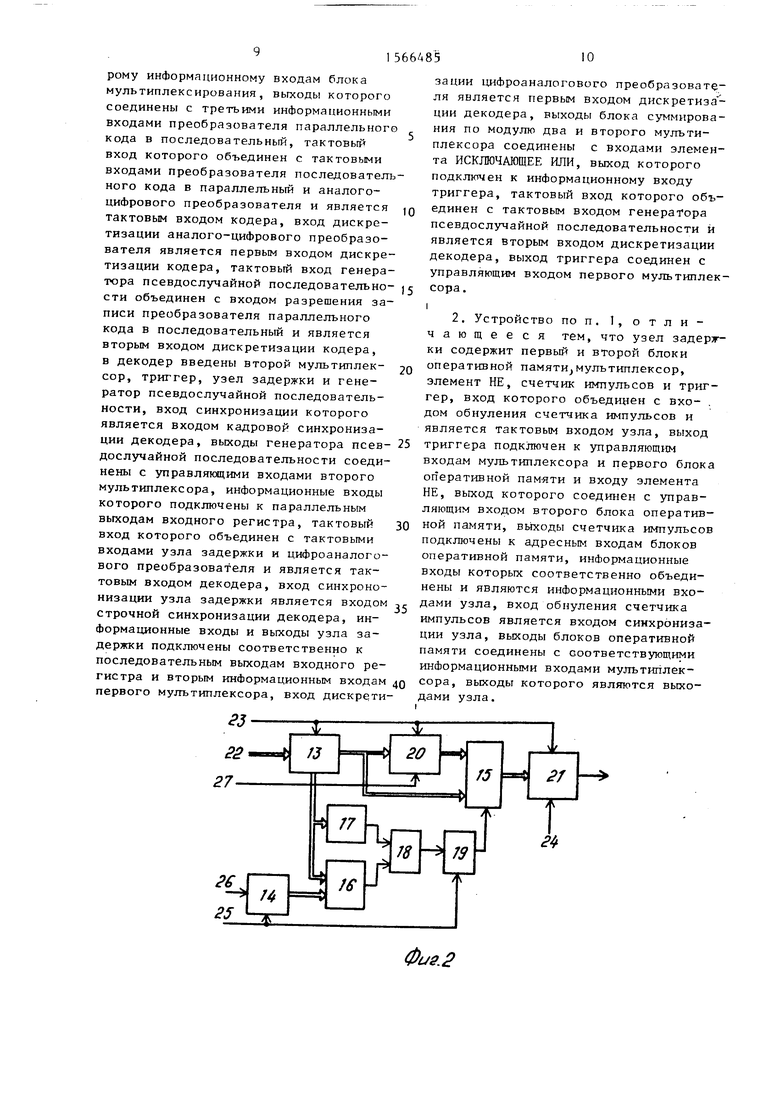

На фиг. 1 и 2 приведены функциональные схемы соответственно кодера и декодера устройства; на фиг. 3 - Функциональная схема узла задержки.

Кодер устройства содержит аналого- цифровой преобразователь (АЦП) 1, преобразователь 2 последовательного кода в параллельный, блок 3 суммирования по модулю два, блок 4 мультиплексирования, генератор 5 псевдослучайной последовательности, дешифратор 6 и преобразователь 7 параллельного кода в последовательный. На фиг. 1 обозначены информационный вход 8, первый вход 9 дискретизации, тактовый вход 10, второй вход 11 дискретизации и вход 12 кадровой синхронизации.

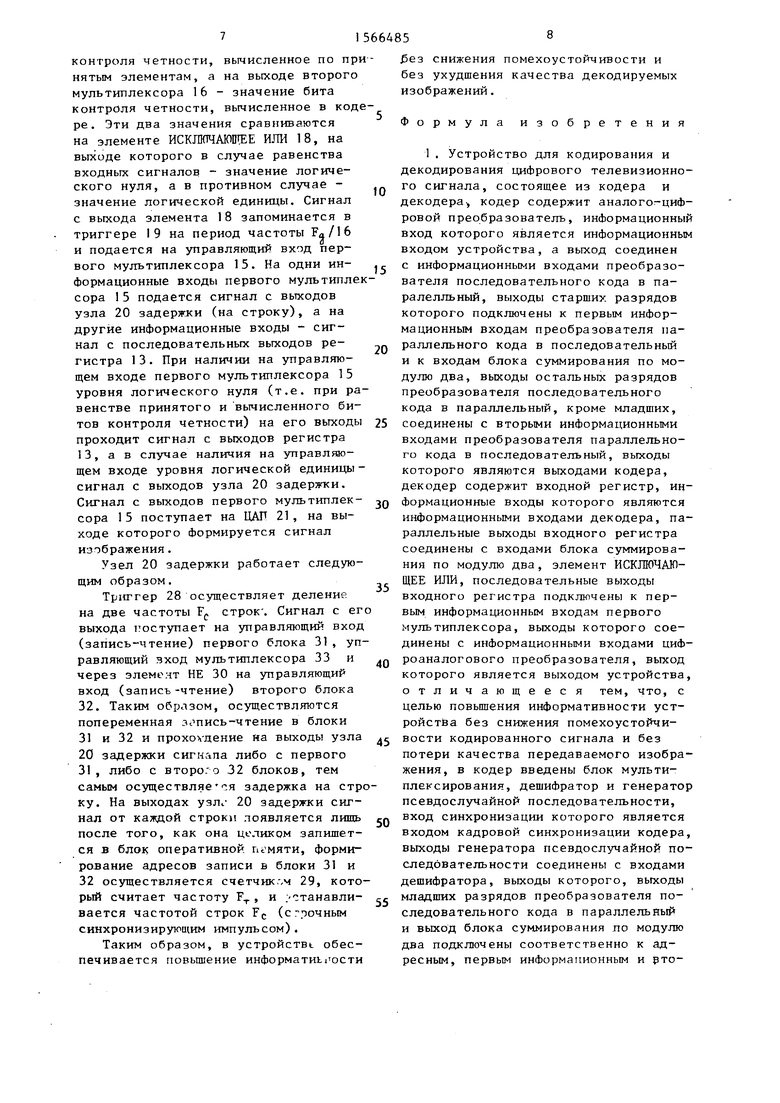

Дек.одер устройства (фиг.2) содержит входной регистр 13, генератор 14 псевдослучайной последовательности, первый 15 и второй 16 мультиплексоры, блок 17 суммирования по модулю двл, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18, триггер 19, узел 20 задержки и цифроаналото- вый преобразователь (ЦАП) 21. На фиг. 2 обозначены информационный 22 и тактовый 23 входы, первый 24 и второй 25 входы дискретизации, входы кадровой 26 и строчной 27 синхронизации. АЦП 1 и ЦАП 21 могут быть, например, восьмиразрядными.

Преобразователи 2 и 7 представляют собой регистры сдвига с числом разрядов, необходимым для кодирования яркости группы элементов А, В, С,..., передаваемого изображения. Число элементов А, В, С,... в группе равно 16, число двоичных разрядов для кодирования яркости одного элемента п 8. Поэтому число разрядов регистров (преобразователей) 2 и 7 равно 128.

Блок 4 мультиплексирования представляет собой К () двух- входовых мультиплексоров, первые информационные и управляющие входы которых являются одноименными входами

0

5

0

5

0

5

0

5

0

5

блока, а вторые информационные входы всех двухвходовых мультиплексоров объединены и являются вторым информационным входом блока.

Генераторы 5 и 14 псевдослучайной последовательности (ПСП) содержат счетчик импульсов, счетный вход и вход обнуления которого являются соответственно тактовым входом и входом кадровой синхронизациии генератора, а выходы счетчика соединены с входами преобразователя кодов, выполненном на ППЗУ, выходы которого являются выходами генератора. ППЗУ в обоих генераторах 5 и 14 запрограммированы одинаково и обеспечивают на своих выходах Формирование случайной последовательности чисел, например 1-16.

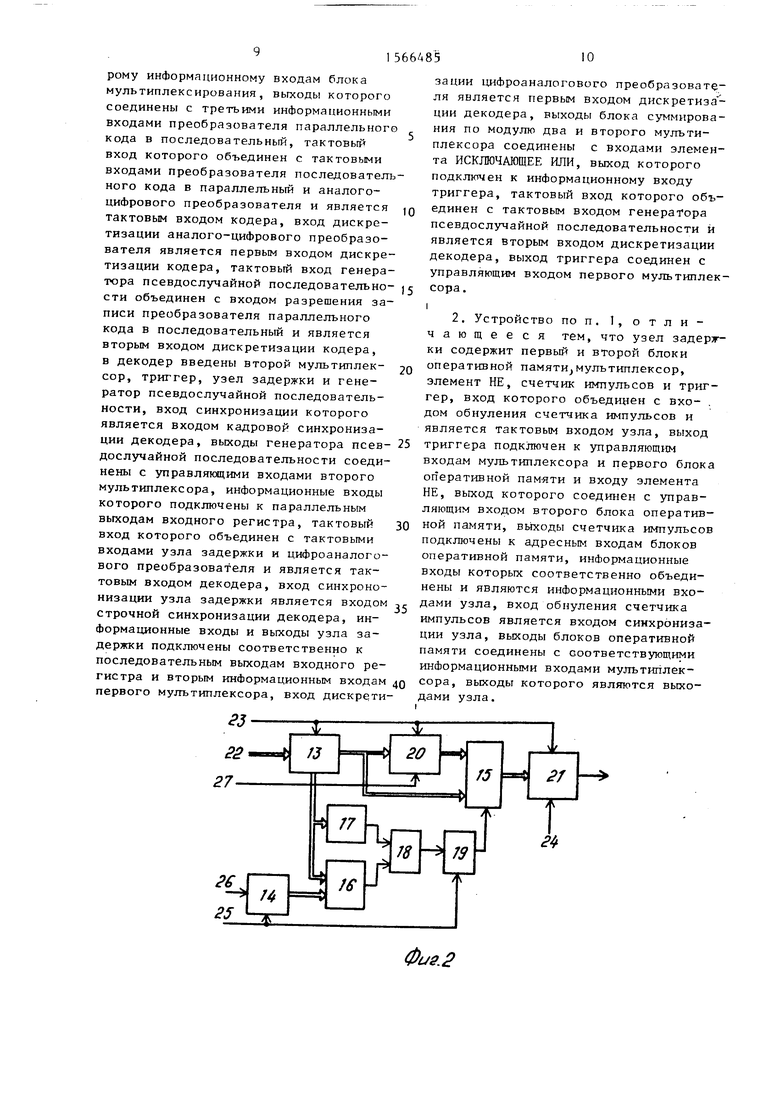

Узел 20 задержки (фиг.З) содержит триггер 28, счетчик 29 импульсов, элемент НЕ 30, первый 31 и второй 32 блоки оперативной памяти и мульти- |Плексор 33. На Фиг. 3 обозначены информационный 34 и тактовый 35 входы и вход 36 синхронизации.

В устройстве реализуется следующий алгоритм работы.

В кодере цифровой поток с выхода АЦП разбивается на группы кодовых слов, соответствующих отсчетам видеосигнала изображения. Эти отсчеты называются элементами А,В.С,... группы. Поскольку интервал межэлементной корреляции составляет 16 элементов, группа содержит именно 16 элементов, чтобы свести к минимуму отличие соседних участков изображения.

За-тем по каждой группе элементов А.В,С,... вычисляется бит контроля четности путем суммирования по модулю два старших разрядов всех элементов группы (количество защищаемых разрядов зависит от требований к качеству декодированных изображений). Значение вычисленного бита контроля четности присваивается младшему разряду одного из элементов группы, номер которого определяется состоянием генератора псевдослучайной последовательности, т.е. бит контроля четности не добавляется к цифровому потоку, а размещается на месте одного из психофизиологически избыточных младших разрядов, выбираемых случайно.

В декодере по.принятым значениям А,В,С,... вычисляется бит контроля четности также путем гуммирования

по модулю два старших разрядов всех элементов группы. Вычисленное значение бита контроля четности сравнивается с принятым значением. Если они не равны, т.е. группа элементов поражена помехой, то происходит замена искаженной группы на соответствующую группу из предьщущей строки. Правильный выбор принимаемого бита контроля четности обеспечивается полной идентичностью и жесткой синхронизацией генераторов псевдослучайной последовательности кодера и декодера.

Устройство работает следующим образом .

В кодере видеосигнал в цифровом виде в последовательном коде с выхода АЦП 1 поступает на преобразователь 2, в который вписывается тактовой частотой FT. Выходы разрядов преобразователя 2, соответствующие определенному числу старших разрядов элементов А,В,С,... (число защищаемых разрядов определяется исходя из требований к субъективному качеству декодированных изображений), поступают на входы блока 3 суммирования по модулю два, вычисляющего значения бита контроля четности. Выходы разрядов преобразователя 2, соответствующие младшим разрядам элементов А,В, С,..., поступают на первые входы блока 4 мультиплексирования. Кроме того, выходы всех разрядов преобразователя 2, за исключением самых младших разрядов, поступают на соответствующие входы преобразователя 7.

Когда в преобразователь 2 целиком вписана очередная группа элементов А,В,С,..., на выходе блока 3 - значение бита контроля четности, вычисленное для данной группы элементов, Это значение поступит на второй вход блока 4, где произойдет присваивание младшему разряду одного из элементов А,В,С,... значения бита контроля четности. Остальные младшие разряды пройдут на выходы блока 4 без изменений.

Замешивание бита контроля четности на место одного из младших разрядов осуществляется следующим образом. Выходы генератора 5 псевдослучайной последовательности соединены с входом дешифратора 6. При значении двоичного числа на входах дешифратора 6, соответствующего значению десятичного числа К (1 ё К si 1 6) , на К-м выходе

0

5

0

5

дешифратора 6 появится уровень логической единицы. Этот уровень переклю - чит К-й двухвходовой мультиплексор блока 4 так, что на его выход поступит сигнал с блока 3 суммирования по модулю два, т.е. бит контроля четности, который запишется в соответствующий разряд преобразователя 7 вместо младшего разряда соответствующего элемента А,В,С,... группы.

Таким образом, значения младших разрядов всех элементов А,В,С,... проходят с выходов преобразователя 2 на входы преобразователя 7 без изменений, за исключением младшего разряда того элемента, номер которого в группе А,В,С,... определяется генератором 5 псевдослучайной последовательности. Для того, чтобы на изображении не оказалось возможности появления ложных контуров в виде сплошных или прерывистых вертикальных ний на равнояркостных участках, период счета счетчика в генераторе 5 не должен быть равен периоду частоты строк телевизионной развертки и не кратен ему. Поскольку для правильной работы устройства необходима точная синхронизация генераторов 5 и 14, ее можно осуществить, устанавливая счетчики этих генераторов в исходное состояние кадровым синхронизирующим импульсом с входов 2 и 26.

Вписывание информации в преобразователь 7 осуществляется с входа 11 частотой дискретизации F, поделенной на J6, т.е. частотой следования группы А,В,С,.... Вывод информации из преобразователя 7 осуществляется тактовой частотой FT.

В декодере входной цифровой поток поступает на регистр J3, который представляет собой сдвиговый регистр с 5 числом разрядов J28. Выходы разрядов регистра J3, соответствующие защищаемым разрядам группы элементов, подаются на входы блока 17 суммирования по модулю два, который осуществляет вычисление бита контроля четности.

Выходы регистра 13, соответствующие младшим разрядам элементов А,В, С,... , поступают на входы второго мультиплексора 16, на управляющие входы которого подаются сигналы с выходов генератора 14 псевдослучайной последо- . вательности. В момент, когда в регистр 13 целиком впишется группа А,В,С,... на выходе блока 17 - значение бита

0

5

0

0

5

контроля четности, вычисленное по принятым элементам, а на выходе второго мультиплексора 16 - значение бита контроля четности, вычисленное в кодере. Эти два значения сравниваются на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 18, на выходе которого в случае равенства входных сигналов - значение логического нуля, а в противном случае - значение логической единицы. Сигнал с выхода элемента 18 запоминается в триггере 19 на период частоты Fa/16 и подается на управляющий вход первого мультиплексора 15. На одни ин- формационные входы первого мультиплексора 15 подается сигнал с выходов узла 20 задержки (на строку), а на другие информационные входы - сигнал с последовательных выходов ре- гистра 13. При наличии на управляющем входе первого мультиплексора 15 уровня логического нуля (т.е. при равенстве принятого и вычисленного битов контроля четности) на его выходы проходит сигнал с выходов регистра 13, а в случае наличия на управляющем входе уровня логической единицы - сигнал с выходов узла 20 задержки. Сигнал с выходов первого мультиплек- сора 15 поступает на ЦАП 21 , на выходе которого формируется сигнал изображения.

Узел 20 задержки работает следующим образом.

Триггер 28 осуществляет деление на две частоты Fc строк . Сигнал с ег выхода поступает на управляющий вход (запись-чтение) первого блока 31 , управляющий зход мультиплексора 33 и через элемент НЕ 30 на управляющий вход (запись-чтение) второго блока 32. Таким образом, осуществляются попеременная запись-чтение в блоки 31 и 32 и прохох-дение на выходы узла 20 задержки сигнала либо с первого

31, либо с второ. о 32 блоков, тем самым осуществляв я задержка на стрку. На выходах узл 20 задержки сигнал от каждой строки появляется лишь после того, как она целиком запишется в оперативной памяти, формирование адресов записи в блоки 31 и

32осуществляется счетчикг-м 29, который считает частоту FT , и .-станавли- вается частотой строк Fc (с рочным синхронизирующим импульсом).

Таким образом, в ycTpoftcTBt обеспечивается повышение информативности

п 5 Q

Q 5

п

5

5

.без снижения помехоустойчивости и без ухудшения качества декодируемых изображений.

Формула изобретения

35

строчной синхронизации декодера, информационные входы и выходы узла задержки подключены соответственно к последовательным выходам входного регистра и вторым информационным входам 40 первого мультиплексора, вход дискретиQо 5 0

5

0

зации цифроаналогового преобразователя является первым входом дискретиэа - ции декодера, выходы блока суммирования по модулю два и второго мультиплексора соединены с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к информационному входу триггера, тактовый вход которого объединен с тактовым входом генератора псевдослучайной последовательности и является вторым входом дискретизации декодера, выход триггера соединен с управляющим входом первого мультиплексора .

i

Фи0.2

фие.З

| Цифровое телевидение./Под ред | |||

| М.И.Кривошеева.-М.: Связь, 1980, с | |||

| Способ получения бензидиновых оснований | 1921 |

|

SU116A1 |

| Устройство для определения физико-механических характеристик материалов | 1988 |

|

SU1516842A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Патент ФРГ № 3334934, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-05-23—Публикация

1988-01-13—Подача