1

Изобретение относится к области запоминающих устройств.

Одно из известных устройств содержит блок хранения информации, блок исправления ошибок для кода, записанного по строкам, подключенный ко входам сумматора по модулю два всех строк кода и перемножителя к другому входу которого подсоединен выход сигнала вектора ошибки блока исправления ошибок, а выход перемножителя соединен через блок сравн.ения с блоком номеров, разрешающим запись в этот блок номера строки из.блока управления.

При этом выхо,ц импульсов кодовой комбинации блока исправления ошибок соединен со входом полусумматора, другой вход которого через ключ, подсоединенный к выходу блока номеров, связан с выходом сумматора 1

Недостатками этого устройства являются большие аппаратурные затраты и невысокая надежность.

Из известных устройств наиболее близким техническим решением к данному изобретению является устройство для исправления сяиибок при итеративном кодировании по авт. св. 364032, содержащее блок хранения

информации с дешифратором адреса, сумматор по модулю два, регистры, ключи и элементы Отрицание равнозначности , при этом выходы блока хранения информации соединены с соответствующими входами сумматора по модулю два, регистра со счетными входами и с первыми входами элементов Отрицание равнозначности ,

0 выходы регистра со счетными входами соединены с первыми входами ключей переписи информации, другие входы; которых соединены с выходом дешифратора адреса, а выходы ключей соеди5нены с соответствующими входами регистра запоминания ошибок, выходы которого соединены с первыми входами ключей переписи информации, другие входы к.точей соединены с выхо-0дом сумматора по модулю два, а выходы ключей соединены со вторыми входами элементов Отрицание равнозначности 2 .

Однако, это устройство не позво5ляет обнаружить ошибки четной кратности в строке. При наличии же слиибой нечетной кратности, находящихся в разных строках, происходит их неправильное исправление, что снижает

0 надежность устройства.

Целью настоящего изобретения является повышение надежности устройства за счет обнаружения ошибок четной кратности в строке и нечетной кратности в разных строках и предотвращение неправильного исправления последних .

Поставленная цель достигается тем, что устройство содержит элементы И и ИЛИ и счетчик, первый выход которого подключен к одному из входов первого элемента И, другой вход которого подключен к выходу сумматора по модулю два, выход первого элемента И соединен с одним из входов ключей переписи информации и со входом счетчика, второй выход счетчика подключен к одному из входов первого элемента ИЛИ, другой вход которого соединен с выходом второго элемента И, Bxojbpi второго элемента И соединены соответственно с первым и третьим выходами счетчика и выходами второго элемента ИЛИ, входы которого подключены к выходам регистра запоминания ошибок.

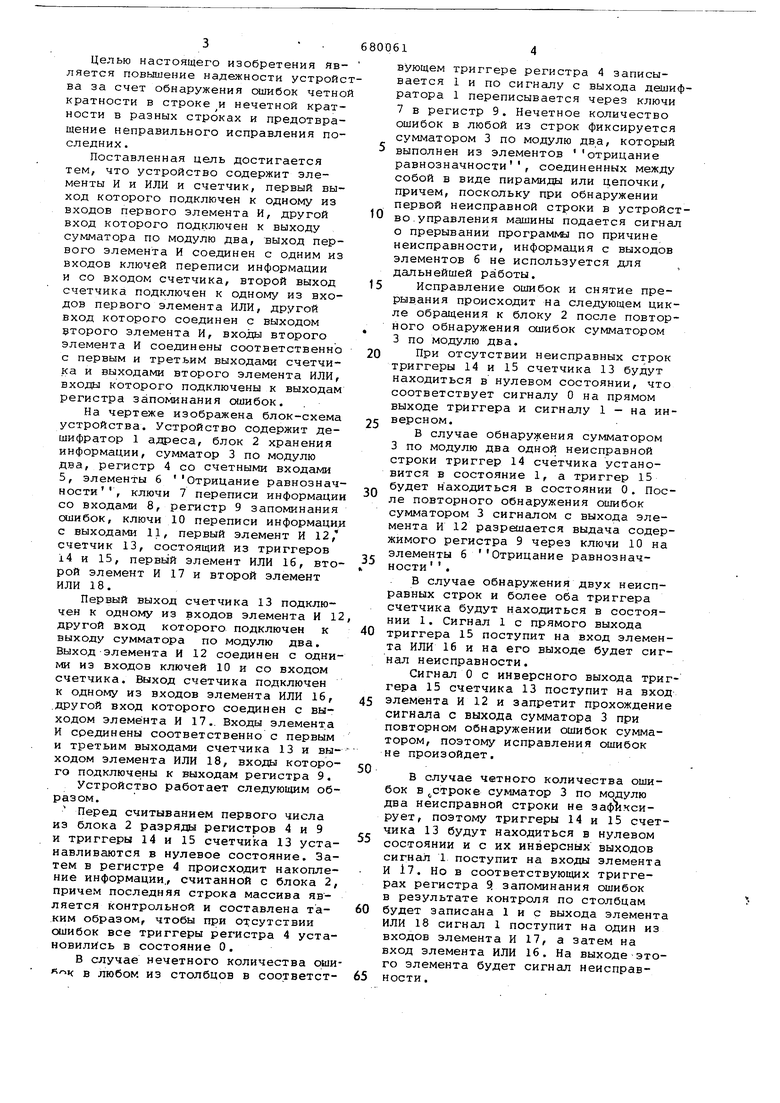

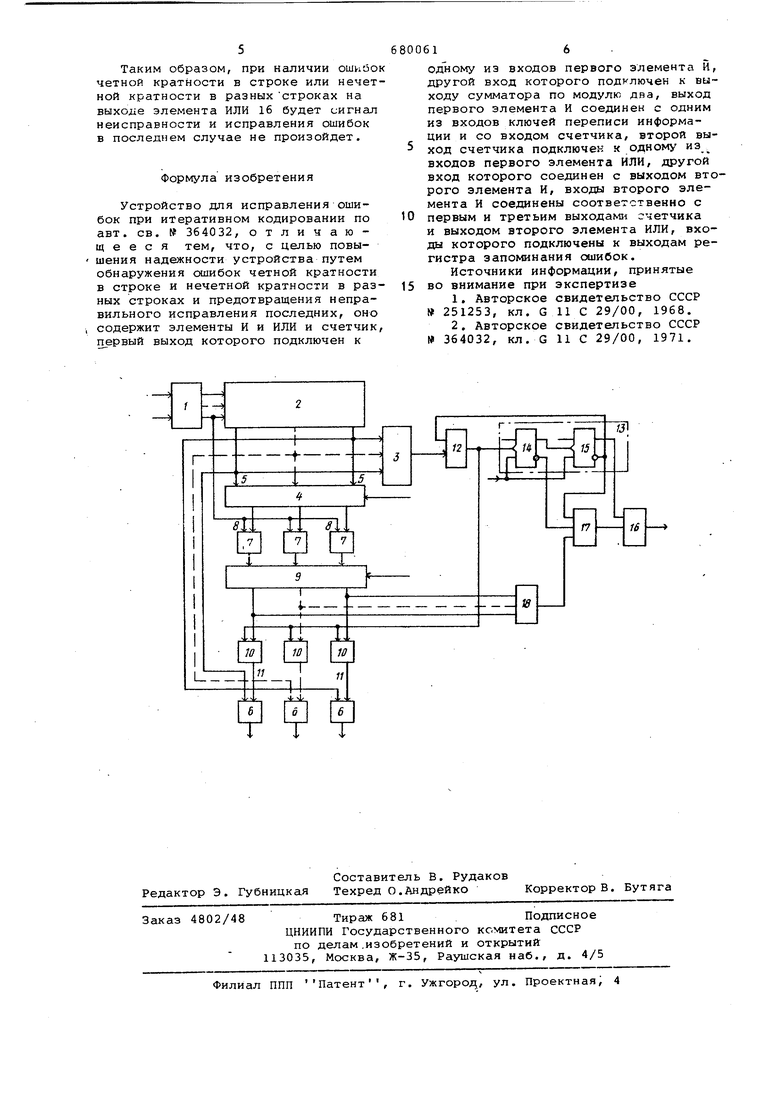

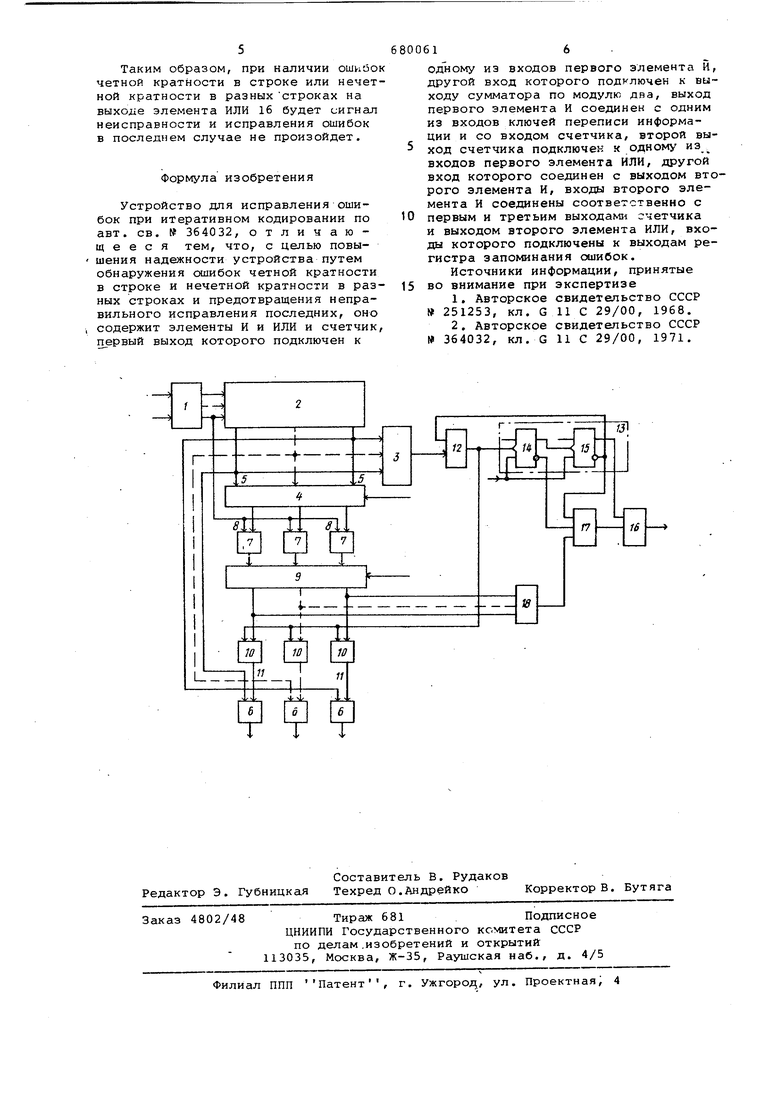

На чертеже изображена блок-схема устройства. Устройство содержит дешифратор 1 адреса, блок 2 хранения информации, сумматор 3 по модулю два, регистр 4 со счетными входами 5, элементы 6 Отрицание равнозначности, ключи 7 переписи информации со входами 8, регистр 9 запоминания сшибок, ключи 10 переписи информации с выходами 11, первый элемент И 12, счетчик 13, состоящий из триггеров 14 и 15, первьай элемент ИЛИ 16, второй элемент И 17 и второй элемент или 18.

Первый выход счетчика 13 подключен к одному из входов элемента И 12 другой вход которого подключен к выходу сумматора по модулю два. Выход элемента И 12 соединен с одними из входов ключей 10 и со входом счетчика. Выход счетчика подключен к одному из входов элемента ИЛИ 16, .другой вход которого соединен с выходом элемента И 17.. Входы элемента И соединены соответственно с первым и третьим выходами счетчика 13 и выходом элемента ИЛИ 18, входы которого подключены к выходам регистра 9.

Устройство работает следующим образом.

Перед считыванием первого числа из блока 2 разряды регистров 4 и 9 и триггеры 14 и 15 счетчика 13 устанавливаются в нулевое состояние. Затем в регистре 4 происходит накопление информации., считанной с блока 2, причем последняя строка массива является контрольной и составлена таким образом, чтобы при отсутствии сяиибок все триггеры регистра 4 установились в состояние 0.

В случае нечетного количества в л:юбом из столбцов в соответствующем триггере регистра 4 записывается 1 и по сигналу с выхода дешифратора 1 переписывается через ключи 7 в регистр 9. Нечетное количество ошибок в любой из строк фиксируется сумматором 3 по модулю два, который выполнен из элементов отрицание равнозначности , соединенных между собой в виде пирамиды или цепочки, причем, поскольку при обнаружении первой неисправной строки в устройство .управления машины подается сигнал о прерывании програмлфл по причине неисправности, информация с выходов элементов 6 не используется для дальнейшей работы.

Исправление ошибок и снятие прерывания происходит на следующем цикле обращения к блоку 2 после повторного обнаружения ошибок сумматором 3 по модулю два.

При отсутствии неисправных строк триггеры 14 и 15 счетчика 13 будут находиться в нулевом состоянии, что соответствует сигналу О на прямом выходе триггера и сигналу 1 - на инверсном.

В случае обнаружения сумматором 3 по модулю два одной неисправной строки триггер 14 счетчика установится в состояние 1, а триггер 15 будет находиться в состоянии 0. После повторного обнаружения ошибок сумматором 3 сигналом с выхода элемента И 12 разрешается выдача содержимого регистра 9 через ключи 10 на элементы 6 Отрицание равнозначности .

В случае обнаружения двух неисправных строк и более оба триггера счетчика будут находиться в состоянии 1. Сигнал 1 с прямого выхода триггера 15 поступит на вход элемента ИЛИ 16 и на его выходе будет сигнал неисправности.

Сигнал О с инверсного выхода триггера 15 счетчика 13 поступит на вход элемента И 12 и запретит прохождение сигнала с выхода сумматора 3 при повторном обнаружении ошибок сумматором, поэтому исправления ошибок не произойдет,

В случае четного количества ошибок в строке сумматор 3 по модулю два неисправной строки не зафиксирует, поэтому триггеры 14 и 15 счетчика 13 будут находиться в нулевом состоянии и с их инверсных выходов сигнал 1 поступит на входы элемента И 17. Но в соответствующих триггерах регистра 9 запоминания ошибок в результате контроля по столбцам будет записана 1 и с выхода элемента ИЛИ 18 сигнал 1 поступит на один из входов элемента И 17, а затем на вход элемента ИЛИ 16. На выходе-этого элемента будет сигнал неисправности.

Таким образом, при наличии ошибок четной кратности в строке или нечетной кратности в разных строках на выходе элемента ИЛИ 16 будет сигнал неисправности и исправления ошибок в последнем случае не произойдет.

Формула изобретения

Устройство для исправления ошибок при итеративном кодировании по авт. св. № 364032, отличающееся тем, что, с целью повышения надежности устройства путем обнаружения ошибок четной кратности в строке и нечетной кратности в разных строках и предотвращения неправильного исправления последних, оно

содержит элементы И и ИЛИ и счетчик, первый выход которого подключен к

одному из входов первого элемента И, другой вход которого подключен к выходу сумматора по модулю два, выход первого элемента И соединен с одним из входов ключей переписи информации и со входом счетчика, второй выход счетчика подключен к одному из входов первого элемента ИЛИ, другой вход которого соединен с выходом второго элемента И, входы второго элемента И соединены соответственно с первым и третьим выхода т счетчика и выходом второго элемента ИЛИ, входы которого подключены к выходам регистра запоминания ошибок.

Источники информации, принятые

5 во внимание при экспертизе

1,Авторское свидетельство СССР 251253, кл. G 11 С 29/00, 1968.

2.Авторское свидетельство СССР 364032, кл. G 11 С 29/00, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК ПРИ ИТЕРАТИВНОМ КОДИРОВАНИИ | 1973 |

|

SU364032A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Динамическое запоминающее устройство | 1977 |

|

SU701354A1 |

| Запоминающее устройство с исправлением ошибок | 1989 |

|

SU1667156A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1061275A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942164A1 |

| УСТРОЙСТВО для КОНТРОЛЯ ИНФОРМАЦИОННОГО ТРАКТА «ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО КОМАНД — ПРОЦЕССОР» | 1973 |

|

SU408309A1 |

Г Г i

Авторы

Даты

1979-08-15—Публикация

1977-06-03—Подача