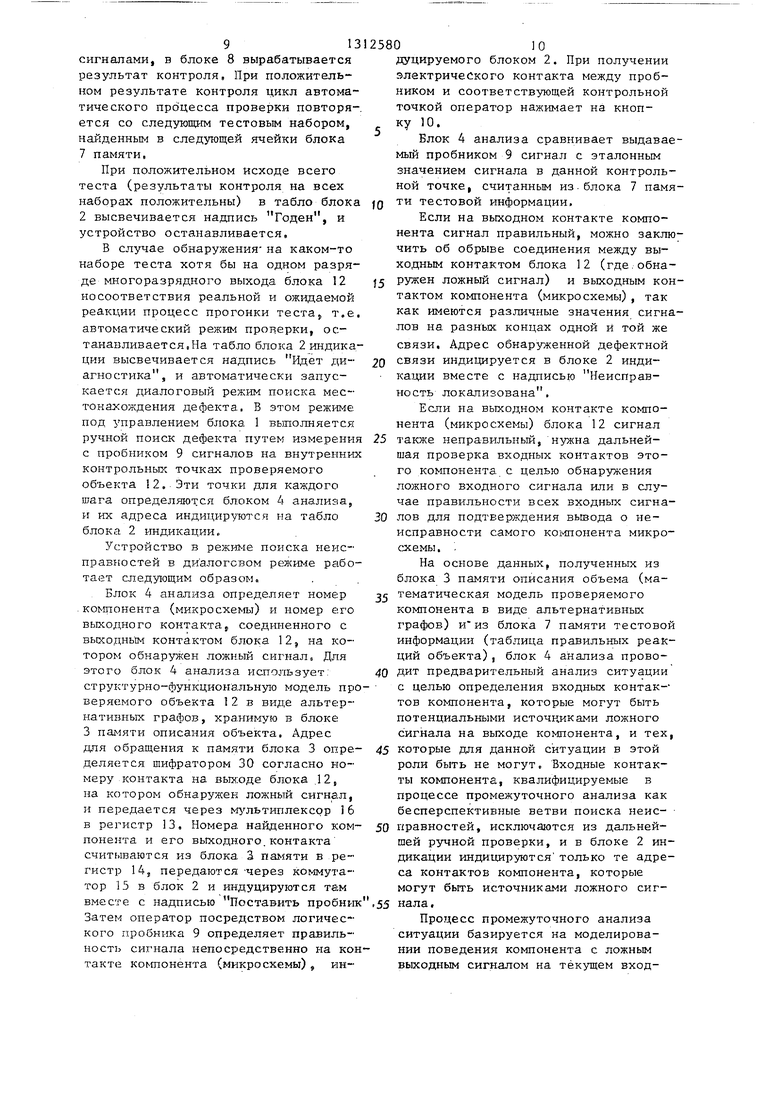

проверяемый объект 12, блок 1 управления, блок 7 памяти тестовой информации, блок 2 индикации, логический пробник 9, вход 5 исходной установки устройства, счетчик 6 адресов,, вход 10 пуска процесса поиска неисправности в диалоговом режиме, вход 11 пуска автоматического процесса контроля, блок 3 памяти модели объекта и блок 4 анализа. Блок 1 управления работает на основе заданной микропрограммы и обеспечивает взаимодействие всех остальных блоков В процессе автоматической проверки блок управления обеспечивает подачу

J

Изобретение относится к вычислительной технике, конкретнее к средствам автоматического контроля цифровых объектов, и может быть применено для проверки интегрсшьных схем, а также собранных на базе их узлов и блоков злектронных вычислительных машин и других средств цифровой автоматики как в производственных условиях , так и при проведении опытно конструкторских работ. В связи с возрастанием сложности блоков вычислительной техники увеличивается объем контрольных операций, необходимых Для оценки качества этих блоков, поэтому автоматизация диагностических операций, как одного из более трудоемкого этапа в процессе изготовления блоков ЭВМ и других объектов цифровой техники, значительно повышает производительность труда.

Цель изобретения - повышение производительности за счет сокращения объема ручных операций.

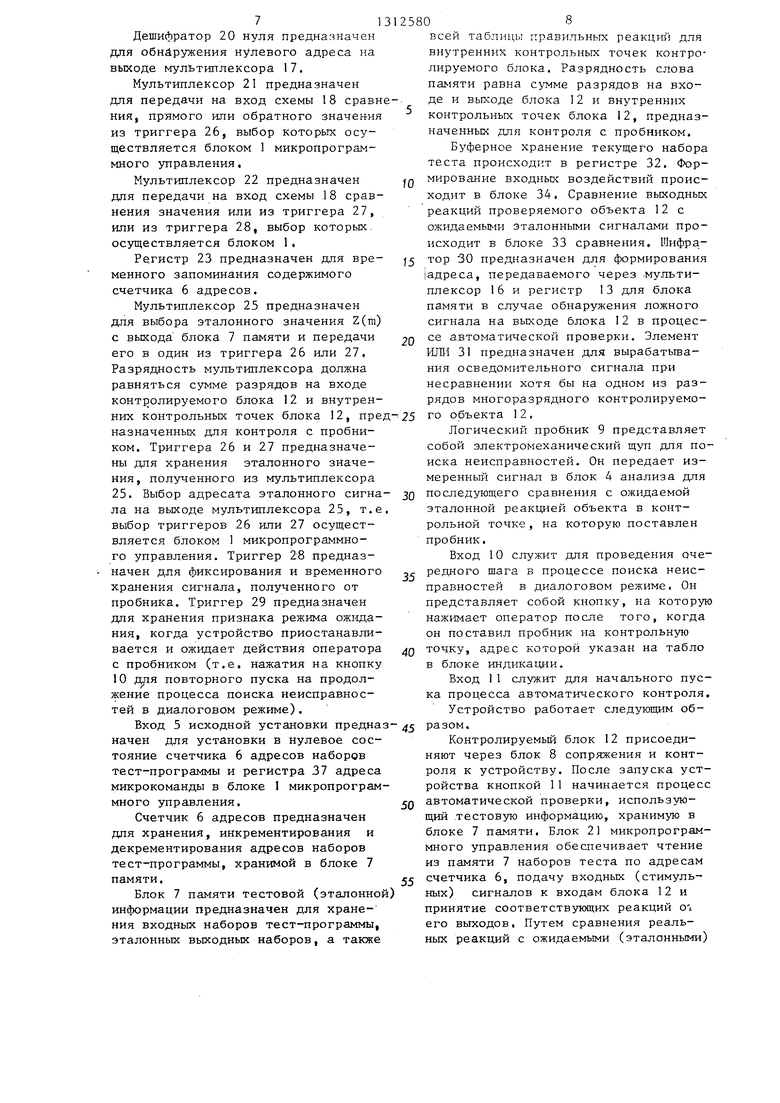

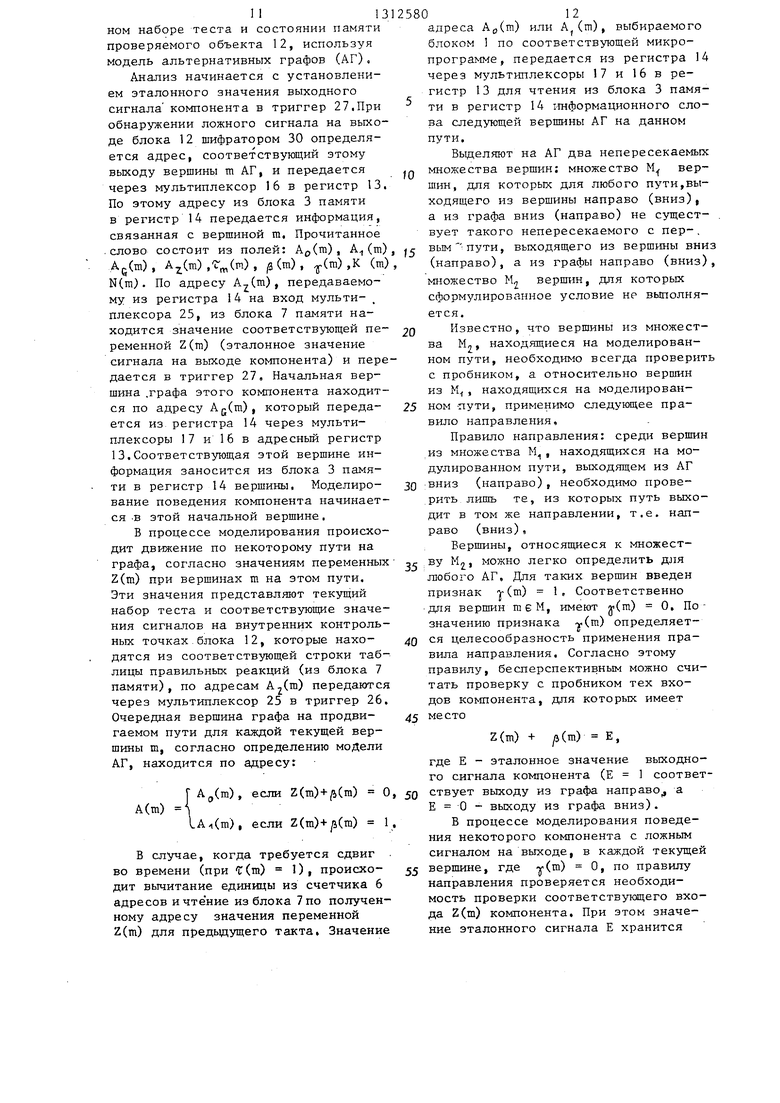

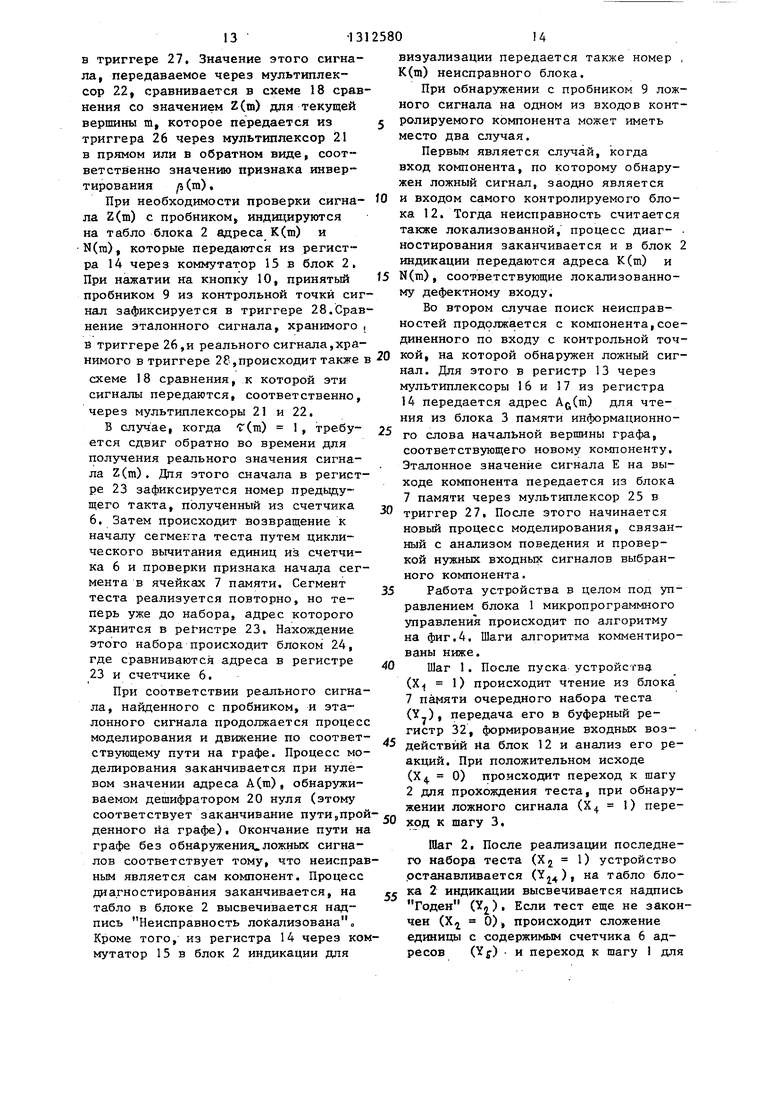

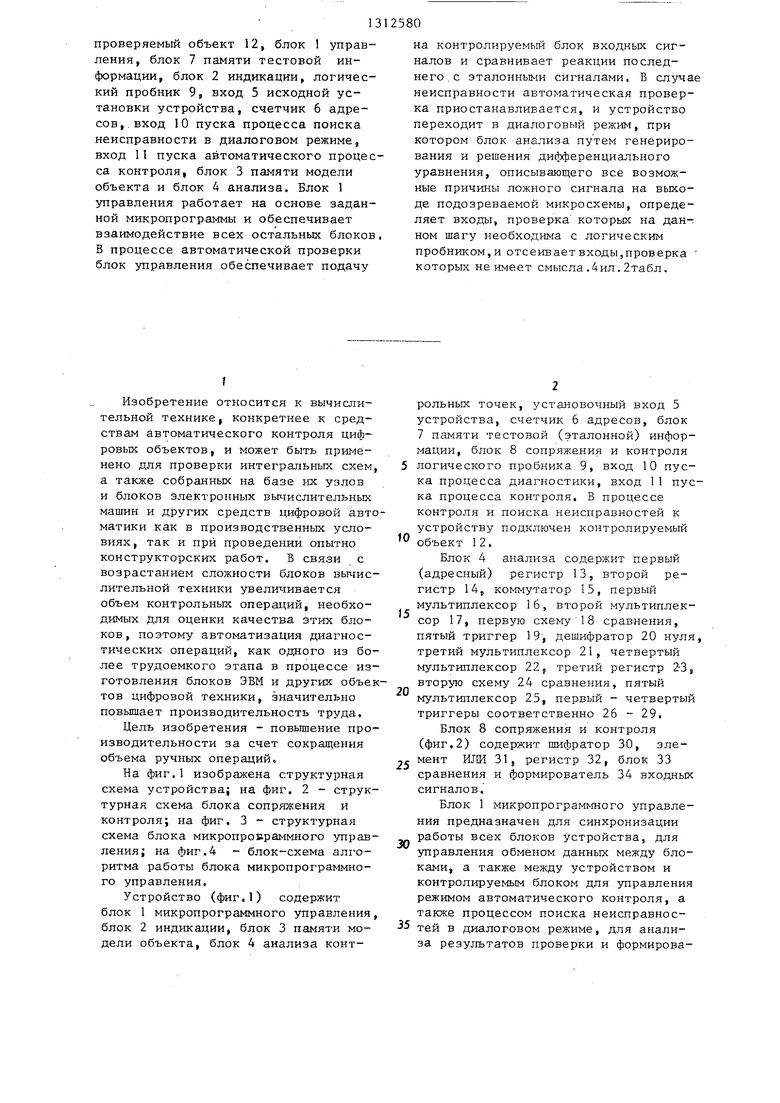

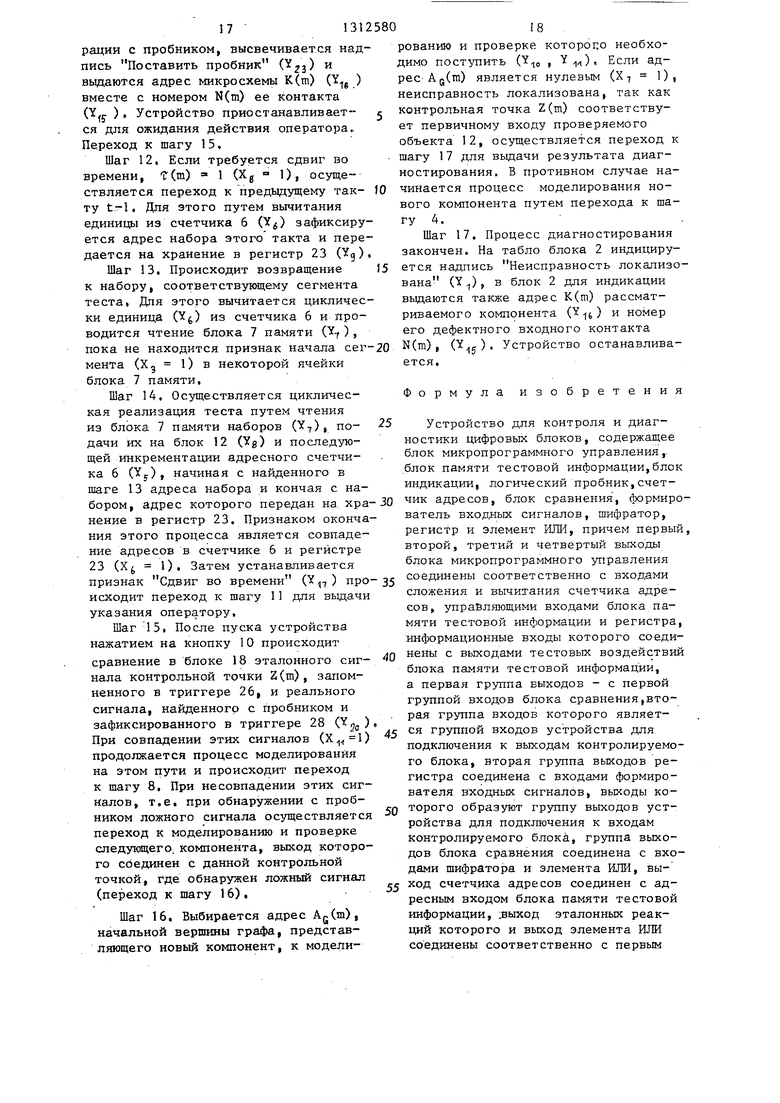

На фиг.1 изображена структурная схема устройства; на фиг. 2 - структурная схема блока сопряокения и контроля; на фиг, 3 - структурная схема блока микропровраммного управления; на фиг.4 - блок-схема алгоритма работы блока микропрограммного управления.

Устройство (фиг«1) содержит блок 1 микропрограммного управления блок 2 индикации, блок 3 памяти модели объекта, блок 4 анализа контна контролируемый блок входньк сигналов и сравнивает реакции последнего , с эталонными сигналами, В случа неисправности автоматическая проверка приостанавливается, и устройство переходит в диалоговый режим, при котором блок анализа путем генерирования и решения дифференциального уравнения, описывающего все возможные причины ложного сигнала на выходе подозреваемой микросхемы, определяет входы, проверка которых на данном шагу необходима с логическим пробником,и отсеиваетвходы,проверка которых не :имеет смысла.4ил. 2табл.

рольных точек, установочный вход 5 устройства, счетчик 6 адресов, блок 7 памяти тестовой (эталонной) информации, блок 8 сопряжения и контроля

огического пробника 9, вход 10 пуска процесса диагностики, вход 11 пуска процесса контроля, В процессе контроля и поиска неисправностей к устройству подключен контролируемый

объект 12.

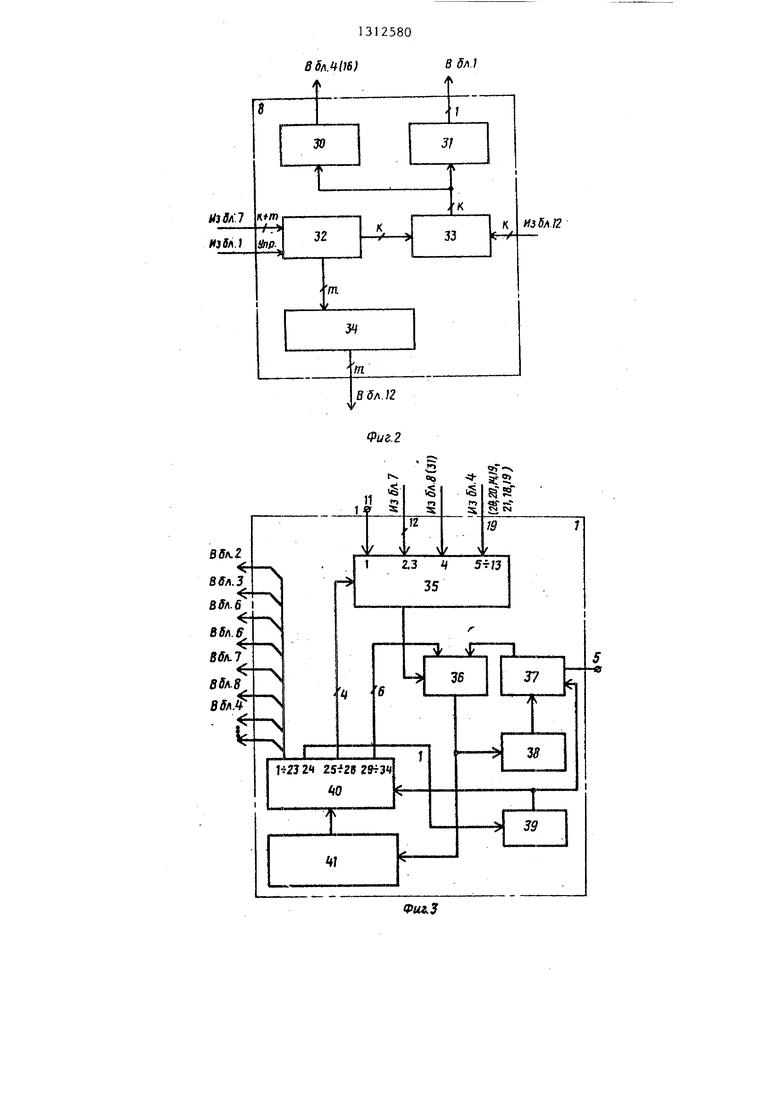

Блок 4 анализа содержит первый (адресный) регистр 13, второй регистр 14, коммутатор 15, первый мультиплексор 16, второй мультиплексор 17, первую схему 18 сравнения, пятый триггер 19, дешифратор 20 нуля, третий мультиплексор 21, четвертый мультиплексор 22j третий регистр 23, вторую схему 24 сравнения, пятый мультиплексор 25, первый - четвертый триггеры соответственно 26 - 29, Блок 8 сопряжения и контроля (фиг,2) содержит шифратор 30, элемент ИЛИ 31, регистр 32, блок 33 сравнения и формирователь 34 входных сигналов.

Блок 1 микропрограммного управления предназначен для синхронизации работы всех блоков устройства, для управления обменом данных между блоками, а также между устройством и контролируемым блоком для управления режимом автоматического контроля, а также процессом поиска неисправностей в диалоговом режиме, для анализа результатов проверки и формирова

313

ния сообщений для визуализации в блоке 2 индикации.

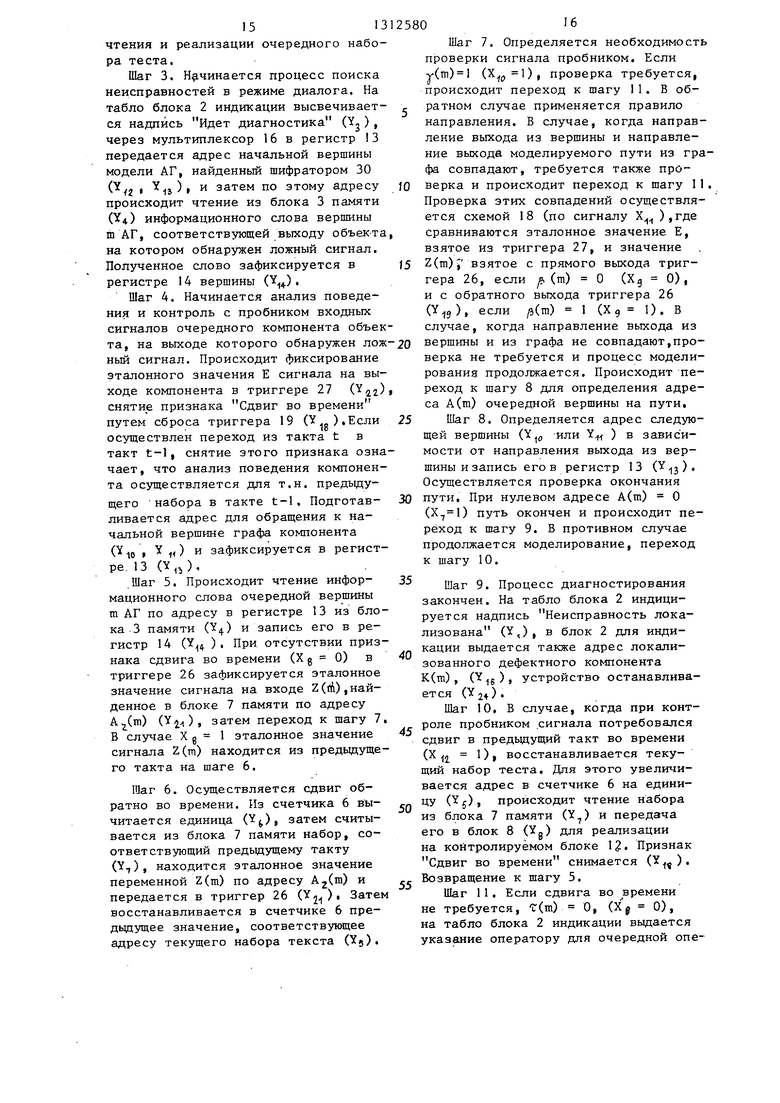

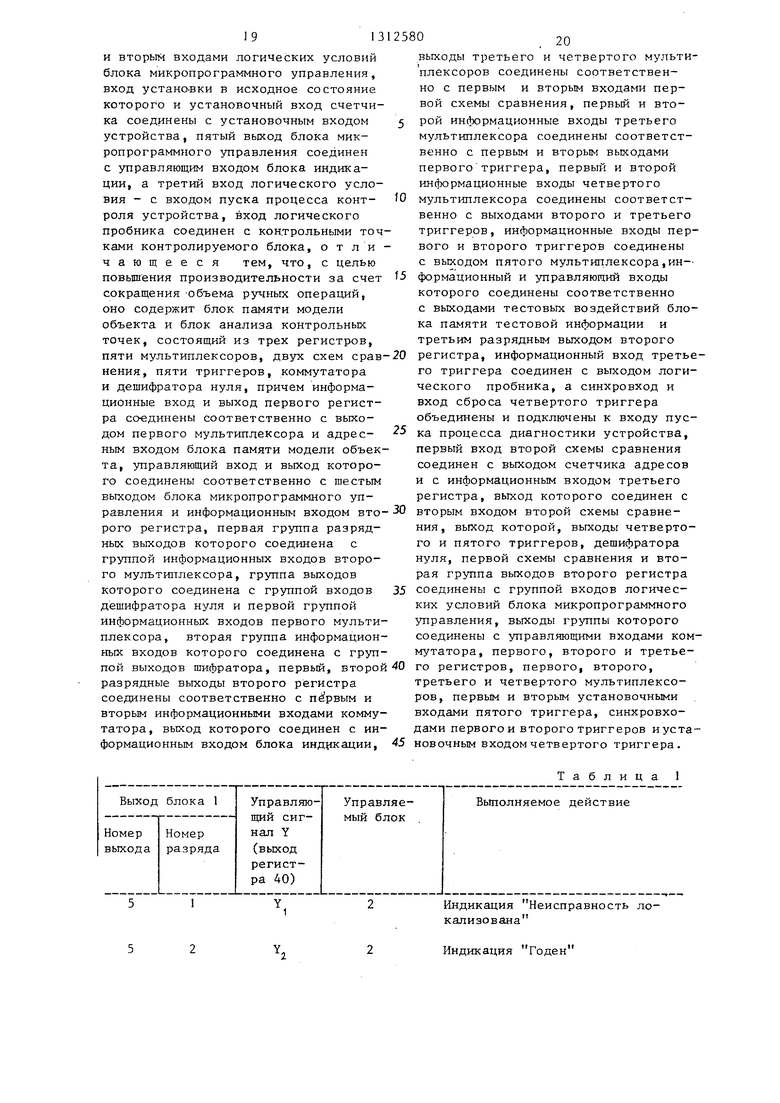

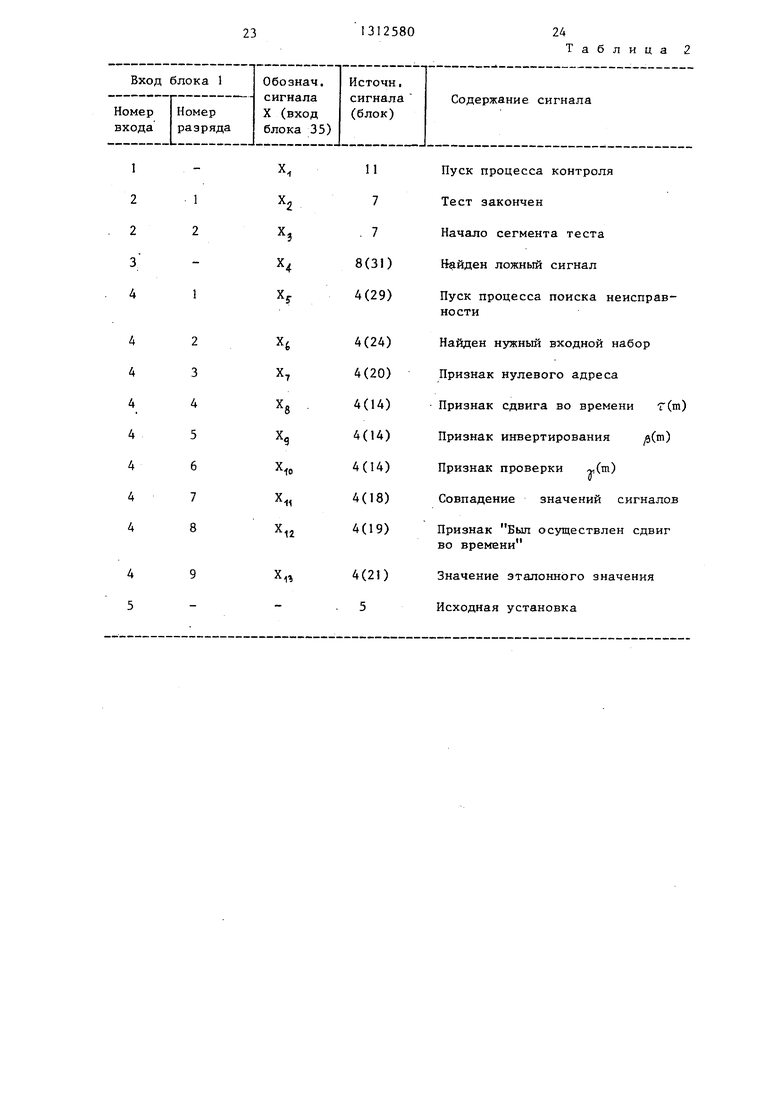

Блок 1 обеспечивает взаимодейст- вие всех блоков устройства путем выработки соответствующих управляющих сигналов в соответствии со значениями осведомительных сигналов, поступающих на входы логических условий блока. Алгоритм работы блока 1 управления приведен в виде блок- схемы на фиг.4. Управляющие сигналы У;(1 1т-24), заданные в операторных вершинах алгоритма, представляющие микрокоманды описаны в табл.1, где каждому сигналу сопоставлен номер и разряд выхода блока 1, являющегося источником этого сигнала, номер блока, которым этот сигнал управляет, а так же выполняемое под управлением этого сигнала действие. Осведомительные сигналы, представляющие условия X; в условных верпш- нах алгоритма, описаны в табл.2,где каждому сигналу Х- сопоставлен номер и разряд входа блока 1, номер блока, являющегося источником этого сигнала, и характеристика логического условияр представленного этим сигналом.

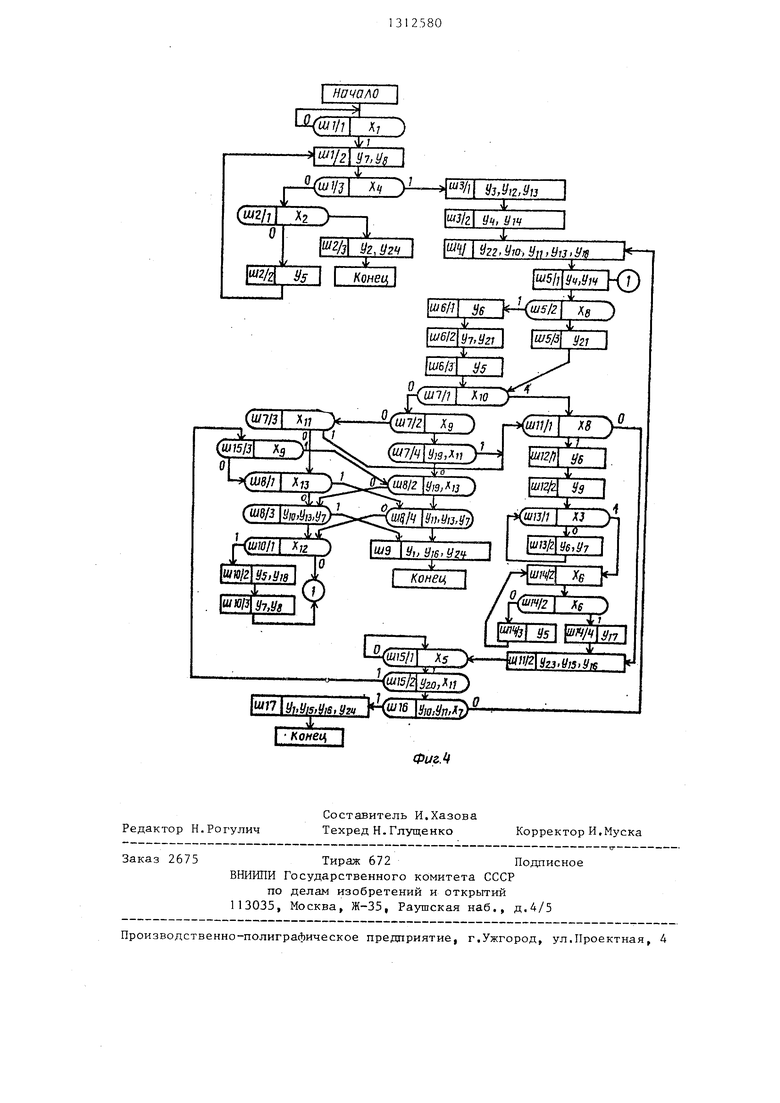

Блок 1 микропрограммного управления (фиг.З) содержит мультиплексор 35,.мультиплексор 36, регистр 37, инкрементор 38, тактовый генератор 39, регистр 40 микрокоманды, блок 41 ПЗУ микропрограмм. Мультиплексор 35 предназначен для коммутации логических условий, мультиплексор 36 - для выбора адреса следующей микрокоманды, регистр 37 - для хранения адреса микрокоманды, блок 38 инкременто- ра - для прибавления единицы к адресу текущей микрокоманды, тактовый генератор 39 - для синхронизации работы блока 1, регистр 40 - для хранения микрокоманды, а блок 41 ПЗУ - дпя хранения микрокоманды алгоритма. Ячейки ПЗУ 41 и регистр 40 микрокоманды содержат 34 разряда. Разряды 1-24 регистра 40 микрокоманды соответствуют 24-м управляющим сигналам Y. , i 1-24, из них разряды 1-3 и

23 образуют пятьй четырехразрядный вы; :од блока 1 , разряды 4-8 обра- зуют, соответственно, шестой, первый второй, третий, четвертый одноразрядные выходы блока 1 и разряды 9/23 образуют 15-разрядную группу выходов блока 1 (табл,1), разряд 24 подклю04

чей к входу тактового генератора 39, выход которого соединен с травляю- щими входами регистров 37 и 40, разряды 25-28 соединены с управляющими входами мультиплексора 35 и разряды 29-34, предназначенные для задания адресов перехода к микропрограмме, подключены к первому информационному входу мультиплексора 36.

Н}1формациочные входы одноразрядного мультиплексора 35 вместе с входом 5 исходной установки, который подключен к входу сброса регистра 37, образуют входы блока 1 (табл.2),

а выход мультиплексора 35 соединен с управляющим входом мульт1тлексора 36 определяет какое из логических условий X;, j 1-13, передается на выход мультиплексора. Коду 0000 соответствует передача нуля (соответствующий вход мультиплексора заземлен), кодам 0001 - 1101 соответствуют передачи сигналов хХ 1 соответственно, а коду 1111 соответствует .передача единицы (соответствующий информационный вход мультиплексора 35 соединен с источником питания) .

Myльт шлeкcop 36 предназначен для

передачи очередного следующего, адреса микрокоманды к адресному входу блока 41 ПЗУ микрокоманды.

При коде 0000 на тгравляющих входах мультиплексора 35 реализуется естественный переход в микропрогра:-ше (переход в микрокоманде в следующей ячейке), при коде 1111 реализуется безусловный переход по адресу в разрядах 29-34 регистра 40 микрокоманды, а при остальных кодах 0001-1101 реализуется условный переход, соответственно сигналам условий Х - Х .

Блок 2 индикации предназначен для визуализации результатов контроля и поиска неисправностей, а также сообщений оператору для продолжения процесса поиска. Блок 2 содержит табло, где могут засвечиваться надписи Годен, Идет диагностика, Поставить пробник, Неисправность локализована и два адреса - адрес компонента (элемента проверяемого устройства на уровне микросхем) и адрес его контакта. Надпись Годен появляется при положительном исходе процесса автоматического контроля. Надпись Идет диагностика является индикацией о том, что в режиме авто513

матического контроля обнаружен ложный сигнал и запущен режим поиска неисправностей в диалоговом режимеi Надпись Поставить пробник является указанием оператору, что для продолжения процесса поиска дефекта,требуется измерение с пробником сигна-- ла в контрольной точке, местонахождение которой задано индикацией адресов микросхемы и ее контакта. Надпись Неисправность локализована появляется при завершении процесса поиска неисправностей. Засвечиваемые, при этом адреса компонента и его контакта указьтают на локализованное местонахождение дефекта. Если засвечиваются оба адреса, дефект локализован на указанном контакте компонента, Если засвечивается только адрес компонента, дефектным является сам компонент,

Блок 2 управляется: со стороны блока . Каждой из четырех надписей и каждому из двух индицируемых адресов соответствует свой управляющий сигнал, Еьщаваемый в нужный момент из блока .(таб.п,).

Блок 3 памяти модели объекта предназначен для хранения математической модели контролируемого блока в виде альтернативных . Для каждого ког-шонента контролируемого .блока с выходом Z сопоставлен некоторьш альтернативный граф G(2)( веришны которого in3G(Z) взвешены переменнь1ми Z(m)s представляющими сигналы на входе компонента и состояние его памяти. Весовые переменные снабжены признаками Г (т) и (ш), единичные значения которых означают, что значение Z(m) относится к предыдущему относительно текущего набора такту (при задании функции схем с памятью) и что значение Z(m) необходимо взять с инверсией. В каждо.й ячейке 3 пшу1яти хранится слово, описывающее о,цну, вершину альтернативного графа (АГ). Слово состоит из следую1(их полей: адрес А(т) нижнего последователя вершины т, адрес А.,(т) правого последователя, вершины т, адрес Agj(m) д/1к перехода в другой граф G (Z(m)), представляющий некоторый другой Компонент контролируемого блока 12 с выходом Z(m), адрес А(ш) значения переменной Z(m) для обращения к разрядам ячеек 7 памяти где хранится таблица правильных реакций контролируемого блока 12, признак сдвига во вре25806

мени L(m), признак инвертирования jb(ja) , специальный признак проверки

2(т), адрес К(т) компонента в контролируемом блоке 12, выдаваемый

5 через регистр 14 и коммутатор 15 в блок 2 для индикации очередного шага подсоединения пробника или местона- хождения локашизованный неисправности, адрес N(m) контакта компонен 0 та, вьщаваемый также через блоки . 14 и 15 в блок 2 для.индикации,

Блок 4 анализа предназначен для отсеивания бесперспективных вариан- тов поиска неисправности и определе15

НИН тех входов компонентов, на выходе которого обнаружен ложный сигнал, которые в дальнейшем должны быть проверены вручную при помощи логического пробника. Блок 4 не работа- 0 ет при режиме автоматического контроля и участвует только в диалоговом режиме поиска неисправностей.

Регистр 13 в блоке 4 предназначен для хранения адресов для обраще- ния к блоку 3 памяти, в ячейках которой хранится описание модели объекта в виде альтернативных графов , Выход регистра 13 соединен с адресным входом блока 3 памяти, управ ляющий вход (вход чтения) которого соединен с вторым вьгходрм блока .1 микропрограммного управления. Регистр 14 предназначен для принятия из блока 3 пгшяти слова, описывающе5 го текущую вершину ш альтернативного графа.- Информационный вход регистра 14 соейинен с выходом блока 3, а управляющий вход подключен к шестому разряду группы выходов бло.ка 1.

0 Регистр 14 содержит 9 подрегистров,- предназначенных для принятия .кодов, соответственно А(т), А(т), Ад(т), AjCm),, ТСт),, 1Ь(т), r(m), K(m), N(m),

5 Коммутатор 15 предназначен для передачи адресов К(т) и N(m) в блок 2 индикации для визуализации.

Мультиплексор 16 предназначен для передачи адресов, соответствен0 но, из блока 8 сопряжения или из мультиплексора 17 в регистр 13,

Мультиплексор 17 предназначен для передачи одного из адресов ), 5 - (ш) или А j(tn) из регистра 14 на входы мультиплексора 16 и дешифратора 20 нуля.

Триггер 9 предназначен для хранения признака Сдвиг во времени.

71

Дешифратор 20 нуля предназначен для обнйружения нулевого адреса на выходе мультиплексора 17.

Мультиплексор 21 предназначен для передачи на вход схемы 18 сравнния, прямого или обратного значения из триггера 26, выбор которых осуществляется блоком 1 микропрограммного управления.

Мультиплексор 22 предназначен для передачи на вход схемы 18 сравнения значения или из триггера 27, или из триггера 28, выбор которых осуществляется блоком 1.

Регистр 23 предназначен для временного запоминания содержимого счетчика 6 адресов.

Мультиплексор 25 предназначен для выбора эталонного значения Z(m) с выхода блока 7 памяти и передачи его в один из триггера 26 или 27, Разрядность мультиплексора должна равняться сумме разрядов на входе контролируемого блока 12 и внутренних контрольных точек блока 12, преназначенных для контроля с пробником. Триггера 26 и 27 предназначены для хранения эталонного значения, полученного из мультиплексора 25. Выбор адресата эталонного сигнала на выходе мультиплексора 25, т,е выбор триггеров 26 или 27 осуществляется блоком 1 микропрограммного управления. Триггер 28 предназначен для фиксирования и временного хранения сигнала, полученного от пробника. Триггер 29 предназначен для хранения признака режима ожидания, когда устройство приостанавливается и ожидает действия оператора с пробником (т.е, нажатия на кнопку 10 повторного пуска на продолжение процесса поиска неисправностей в диалоговом режиме),

Вход 5 исходной установки преднаначен для установки в нулевое состояние счетчика 6 адресов наборов тест-программы и регистра 37 адреса микрокоманды в блоке 1 микропрограммного управления.

Счетчик 6 адресов предназначен для хранения, инкрементирования и декрементирования адресов наборов тест-программы, хранимой в блоке 7 памяти.

Блок 7 памяти тестовой (эталонно информации предназначен для хранения входных наборов тест-программы, эталонных выходных наборов, а также

5808

всей таблицы правильных реакций для внутренних контрольных точек контролируемого блока. Разрядность слова памяти равна сумме разрядов на входе и выходе блока 12 и внутренних контрольных точек блока 12, предназначенных для контроля с пробником.

Буферное хранение текущего набора теста происходит в регистре 32. ФорQ мирование входных воздействий происходит в блоке 34, Сравнение выходных реакций проверяемого объекта 12 с ожидаемыми эталонными сигнала1ми происходит в блоке 33 сравнения, Шифра5 тор 30 предназначен для формирования {адреса, передаваемого через -мультиплексор 16 и регистр 13 для блока памяти в случае обнаружения ложного сигнала на выходе блока 12 в процесQ се автоматической проверки. Элемент HIM 31 предназначен для вырабатьша- ния осведомительного сигнала при несравнении хотя бы на одном из разрядов многоразрядного контролируемо5 го обьекта 12,

Логический пробник 9 представляет собой электромеханический щуп для поиска неисправностей. Он передает измеренный сигнал в блок 4 анализа для

Q последующего сравнения с ожидаемой эталонной реакцией объекта в контрольной точке, на которую поставлен пробник.

Вход 10 служит для проведения очеc редного шага в процессе поиска неисправностей в диалоговом режиме, Он представляет собой кнопку, на которую нажимает оператор после того, когда он поставил пробник на контрольную

Q точку, адрес которой указан на табло в блоке индикации.

Вход 11 служит для начального пуска процесса автоматического контроля. Устройство работает следующим об5 разом.

Контролируемый блок I2 присоединяют через блок 8 сопряжения и контроля к устройству. После запуска устройства кнопкой 11 начинается процесс

П автоматической проверки, использующий тестовую информацию, хранимую в блоке 7 памяти. Блок 21 микропрограммного управления обеспечивает чтение из памяти 7 наборов теста по адресам

5 счетчика 6, подачу входных (стимуль- ных) сигналов к входам блока 12 и принятие соответствующих реакций oi его выходов. Путем сравнения реальных реакций с ожидаемыми (эталонными)

сигналами, в блоке 8 вырабатывается результат контроля. При положительном результате контроля цикл автоматического процесса проверки повтори-, ется со следуюпр-гм тестовым набором, найденным в следующей ячейки блока 7 памяти,

При положительном исходе всего теста (результаты контроля на всех наборах положительны) в табло блока 2 высвечивается надпись Годен, и устройство останавливается,

В случае обнаружения- на каком-то наборе теста хотя бы на одном разряде многоразрядного выхода блока 12 носоответствия реальной и ожидаемой реакции процесс прогонки теста т.е, автоматический режим проверки, останавливается,На табло блока 2 индикации высвечивается надпись Идет диагностика, и автоматически запускается диалоговый режим поиска М€;с- тонахождения дефекта, В этом режиме под управлением блока 1 выполняется ручной поиск дефекта путем измерения с пробником 9 сигналов на внутренних контрольных точках проверяемого объекта 12, Эти точки для каждого шага определяются блоком 4 анализа, и их адреса индицирук тся на табло блока 2 индикации.

Устройство в режиме поиска неисправностей в диалоговом режиме работает следующим образом.

Блок 4 анализа опр)еделяет номер .компонента (микросхемы) и номер его выходного контакта( соединенного с выходнь м контактом блока 12, на котором обнаружен ложный сигнал, Для этого блок 4 анализа использует, структурно-функциональную модель проверяемого объекта 12 в виде альтернативных графов, хранимую в блоке 3 памяти описания объекта. Адрес для обращения к памяти блока 3 определяется шифратором 30 согласно номеру контакта на вькоде блока 12, на котором обнаружен ложный сигнал, и передается через К5 льтиплексор 1 6 в регистр 13, Номера найденного компонента и его выходного, контакта считываются из блока S памяти в регистр 14, передаются -через коммутатор 15 в блок 2 и индуцируются там вместе с надписью Поставить пробник Затем оператор посредством логического пробника 9 определяет правильность сигнала непосредственно на контакте KONfflOHeHTa (микросхемы), инfO

20

25

131258010

дуцируемого блоком 2. При получении электрического контакта между пробником и соответствующей контрольной точкой оператор нажимает на кнопку 10,

Блок 4 анализа сравнивает выдаваемый пробником 9 сигнал с эталонным значением сигнала в данной контрольной точке, считанным из.блока 7 памяти тестовой информации.

Если на выходном контакте компонента сигнал правильный, можно заключить об обрыве соединения между выходным контактом блока 12 (где.обна- J5 ружен ложньй сигнал) и выходным контактом компонента (микросхемы), так как имеются различные значения сигналов на разных; концах одной и той же связи. Адрес обнаруженной дефектной связи индицируется в блоке 2 индикации вместе с надписью Неисправность локализована.

Если на выходном контакте компонента (микросхемы) блока 12 сигнал также неправильный, нужна дальнейшая проверка входных контактов этого компонента, с целью обнаружения ложного входного сигнала или в случае правильности всех входных сигналов для подтверждения вывода о неисправности самого ко1чпонента микросхемы , .

На основе данных, полученных из блока 3 памяти описания объема (математическая модель проверяемого компонента в виде альтернативных графов) и из блока 7 памяти тестовой информации (таблица правильных реакций объекта), блок 4 анализа проводит предварительный анализ ситуации с целью определения входных контак- тов компонента, которые могут быть потенциальными источниками ложного сигнала на выходе компонента, и тех, 45 которые для данной ситуации в этой роли быть не могут, Входные контакты компонента, квалифицируемые в процессе промежуточного анализа как бесперспективные ветви поиска неис- 50 правностей, исключаются из дальнейшей ручной проверки, и в блоке 2 индикации индицируются только те адреса контактов компонента, которые могут быть источниками ложного сиг- 55 нала,

Процесс промежуточного анализа ситуации базируется на моделировании поведения компонента с ложным выходным сигналом на текущем вход30

35

40

1113

ном наборе теста и состоянии памяти проверяемого объекта 12, используя модель альтернативных графов (АГ).

Анализ начинается с установлением эталонного значения выходного сигнала компонента в триггер 27.При обнаружении ложного сигнала на выходе блока 12 шифратором 30 определяется адрес, соответствующий этому выходу вершины m АГ, и передается через мультиплексор 16 в регистр 13. По этому адресу из блока 3 памяти в регистр 14 передается информация, связанная с вершиной га. Прочитанное слово состоит из полей: А{,(т), А (т) Ag(m) , A.j(m) , t n,(in) , ,3 (m) , (m) ,K (m) N(m). По адресу ), передаваемому из регистра 14 на вход мультиплексора 25, из блока 7 памяти находится значение соответствующей переменной Z(m) (эталонное значение сигнала на выходе компонента) и передается в триггер 27, Начальная вершина .графа этого компонента находится по адресу Ац(т), который передается из регистра 14 через мультиплексоры 17 и 16 в адресный регистр 13,Соответствующая этой вершине информация заносится из блока 3 памяти в регистр 14 вершины. Моделирование поведения компонента начинается .3 этой начальной вершине.

В процессе моделирования происходит движение по некоторому пути на графа, согласно значениям переменных Z(m) при вершинах m на этом пути. Эти значения представляют текущий набор теста и соответствуюш;ие значения сигналов на внутренних контрольных точках блока 12, которые находятся из соответствующей строки таблицы правильных реакций (из блока 7 памяти), по адресам ) передаются через мультиплексор 25 в триггер 26. Очередная вершина графа на продвигаемом пути для каждой текущей вершины т, согласно определению модели АГ, находится по адресу:

А(т)

Ag(m), если Z(m) + /i(m) О, .A.i(m), если Z(m)(m) 1,

В случае, когда требуется сдвиг во времени (при Т(го) 1), происходит вычитание единицы из счетчика 6 адресов ичте ние из блока 7 по полученному адресу значения переменной Z(m) для предыдущего такта. Значение

012

адреса А,(т) или А (т), выбираемого блоком I по соответствующей микропрограмме, передается из регистра 14 через мультиплексоры 17 и 16 в регистр 13 для чтения из блока 3 памяти в регистр 14 :1нформационного слова следующей вершины АГ на данном пути.

Выделяют на АГ два непересекаемых

множества вершин: множество М вершин, для которых для любого пути,выходящего из вершины направо (вниз), а из графа вниз (направо) не сущест- . вует такого непересекаемого с пер-,

вым пути, выходящего из вершины вниз (направо), а из графы направо (вниз), множество Mj вершин, для которых сформулированное условие не выполняется.

Известно, что вершины из множества Mj, находящиеся на моделированном пути, необходимо всегда проверить с пробником, а относительно вершин из М, находящихся на моделированном -пути, применимо следующее правило направления.

Правило направления: среди вершин из множества М, находящихся на модулированном пути, выходящем из АГ

вниз (направо), необходимо проверить лишь те, из которых путь выходит в том же направлении, т.е. направо (вниз),

Вершины, относяшиеся к множеству М, можно легко определить для любого АГ, Для таких вершин введен признак j-(m) 1, Соответственно для вершин тем, имеют у(т) О, По- значению признака -уСи) определяется целесообразность применения правила направления. Согласно этому правилу, беслерспективным можно считать проверку с пробником тех входов компонента, для которых имеет

место

Z(m) + /i(m) Е,

где Е - эталонное значение выходного сигнала компонента (Е 1 соответствует выходу из графа направо а Е О - выходу из графа вниз).

В процессе моделирования поведения некоторого компонента с ложнв 1М сигналом на выходе, в каждой текущей

вершине, где у(т) О, по правилу направления проверяется необходимость проверки соответствугацего входа Z(m) компонента. При этом значение эталонного сигнала Е хранится

в триггере 27, Значение этого сигнала, передаваемое через мультиплек10

сор 22, сравнивается в схеме 18 сравнения со значением 2(ш) для текущей вершины т, которое передается из триггера 26 через мультиплексор 21 в прямом или в обратном виде, соответственно значению признака инвертирования р, (га),

При необходимости проверки сигнала Z(ni) с пробником, индицируются на табло блока 2 адреса К(т) и N(m), которые передаются из регистра 14 через коммутатор 15 в блок 2, При нажатии на кнопку 10, принятый пробником 9 из контрольной точки сигнал зафиксируется в триггере 28,Сравнение эталонного сигнала, хранимого , в триггере 26,и реального сигнала,хранимого в триггере 28,происходит также в 20 схеме 18 сравнения, к которой эти сигналы передаются, соответственно, через мультиплексоры 21 и 22,

В случае, когда Т(т) 1, требуется сдвиг обратно во времени для получения реального значения сигнала Z(m) . Для этого сначала в регистре 23 зафиксируется номер предыдущего такта, полученный из счетчика 6, Затем происходит возвращение к началу сегмента теста путем циклического вычитания единиц из счетчика 6 и проверки признака начала сегмента в ячейках 7 памяти. Сегмент теста реализуется повторно, но теперь уже до набора, адрес которого хранится в pet HCTpe 23, Нахождение этого набора происходит блоком 24, где сравниваются адреса в регистре 23 и счетчике 6,

При соответствии реального сигнала, найденного с пробником, и эталонного сигнала продолжается процесс

визуализации передается также номер , К(т) неисправного блока.

При обнаружении с пробником 9 ложного сигнала на одном из входов контролируемого компонента может иметь место два случая.

Первым является случай, когда вход компонента, по которому обнаружен ложный сигнал, заодно является и входом самого контролируемого блока 12, Тогда неисправность считается также локализованной, процесс диаг- ностирования заканчивается и в блок 2 индикации передаются адреса К(т) и 15 N(m), соответствующие локализованному дефектному входу.

Во втором случае поиск неисправностей продолжается с компонента,соединенного по входу с контрольной точ30

кой, на которой обнаружен ложный сигнал. Для этого в регистр 13 через мультиплексоры 16 и 17 из регистра 14 передается адрес Ag(m) для чтения из блока 3 памяти информационно- 5 го слова начальной вершины графа, соответствующего новому компоненту, Эталонное значение сигнала Е на выходе компонента передается из блока 7 памяти через мультиплексор 25 в триггер 27, После этого начинается новый процесс моделирования, связанный с анализом поведения и проверкой нужных входньк сигналов выбранного компонента.

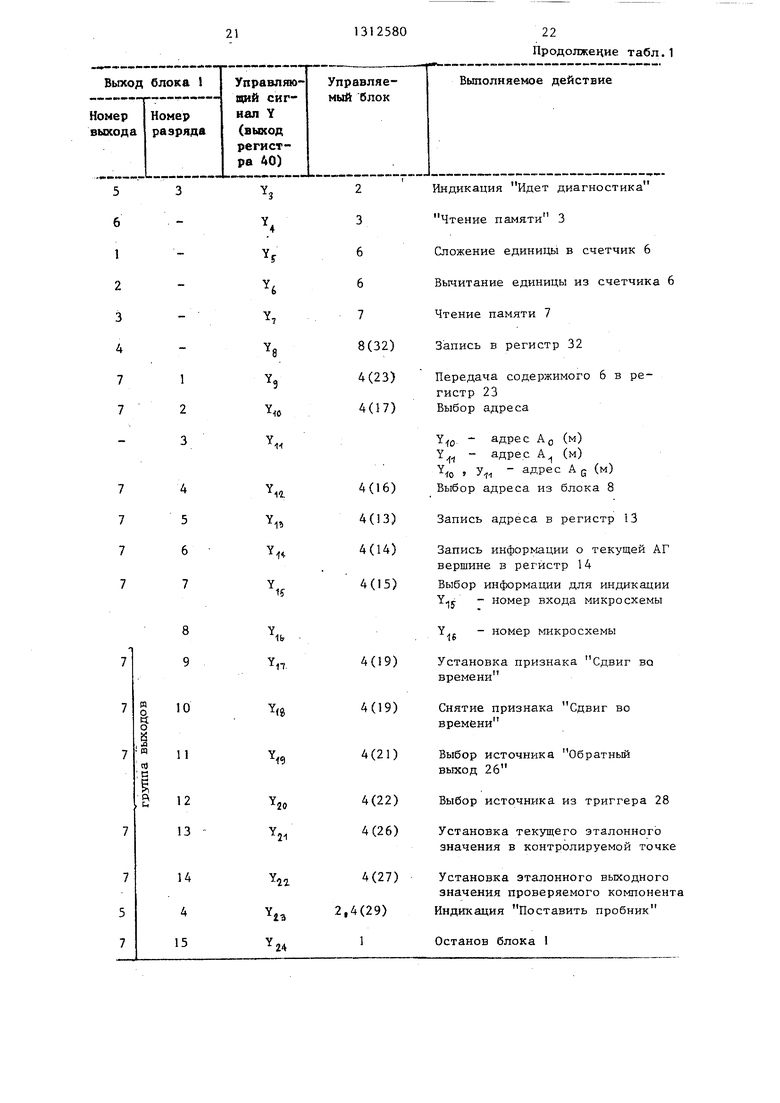

Работа устройства в целом под управлением блока 1 микропрограммного управления происходит по алгоритму на фиг,4, Шаги алгоритма комментированы ниже.

Шаг 1, После пуска устройства (Х 1) происходит чтение из блока 7 памяти очередного набора теста

35

40

(Y), передача его в буферный регистр 32, формирование входных воз- моделирования и двилсение по соответ- л, „.:, ,«

45 действий rta блок 12 и анализ его реакций. При положительном исходе

ствующему пути на графе. Процесс моделирования заканчивается при нулевом значении адреса А(т) , обнаруживаемом дешифратором 20 нуля (этому соответствует заканчивание пути„прой- п денного rta графе). Окончание пути на графе без обнаружение.ложных сигналов соответствует тому, что неисправным является сам компонент. Процесс диагностирования заканчивается, на табло в блоке 2 высвечивается надпись Неисправность локализована о Кроме того, из регистра 14 через коммутатор 15 в блок 2 индикации для

(Х4. 0) происходит переход к шагу 2 для прохоящения теста, при обнаружении ложного сигнала (Х О переход к шагу 3,

Шаг 2, После реализации последнего набора теста (Xj 1) устройство останавливается (Y), на табло блока 2 индикации высвечивается надпись Годен (Yj), Если тест еще не закончен (Х 0), происходит сложение единицы с содержимым счетчика 6 адресов (Yf) . и переход к шагу 1 для

визуализации передается также номер , К(т) неисправного блока.

При обнаружении с пробником 9 ложного сигнала на одном из входов контролируемого компонента может иметь место два случая.

Первым является случай, когда вход компонента, по которому обнаружен ложный сигнал, заодно является и входом самого контролируемого блока 12, Тогда неисправность считается также локализованной, процесс диаг- ностирования заканчивается и в блок 2 индикации передаются адреса К(т) и N(m), соответствующие локализованному дефектному входу.

Во втором случае поиск неисправностей продолжается с компонента,соединенного по входу с контрольной точ

кой, на которой обнаружен ложный сигнал. Для этого в регистр 13 через мультиплексоры 16 и 17 из регистра 14 передается адрес Ag(m) для чтения из блока 3 памяти информационно- го слова начальной вершины графа, соответствующего новому компоненту, Эталонное значение сигнала Е на выходе компонента передается из блока 7 памяти через мультиплексор 25 в триггер 27, После этого начинается новый процесс моделирования, связанный с анализом поведения и проверкой нужных входньк сигналов выбранного компонента.

Работа устройства в целом под управлением блока 1 микропрограммного управления происходит по алгоритму на фиг,4, Шаги алгоритма комментированы ниже.

Шаг 1, После пуска устройства (Х 1) происходит чтение из блока 7 памяти очередного набора теста

(Х4. 0) происходит переход к шагу 2 для прохоящения теста, при обнаружении ложного сигнала (Х О переход к шагу 3,

Шаг 2, После реализации последнего набора теста (Xj 1) устройство останавливается (Y), на табло блока 2 индикации высвечивается надпись Годен (Yj), Если тест еще не закончен (Х 0), происходит сложение единицы с содержимым счетчика 6 адресов (Yf) . и переход к шагу 1 для

151

чтения и реализации очередного набора теста.

Шаг 3. Начинается процесс поиска неисправностей в режиме диалога. На табло блока 2 индикации высвечивается надпись Идет диагностика (Yj), через мультиплексор 16 в регистр 13 передается адрес начальной вершины модели АГ, найденный шифратором 30 ( t ij) и затем по этому адресу происходит чтение из блока 3 памяти (Y) информационного слова вершины m АГ, соответствующей выходу объек-та на котором обнаружен ложный сигнал. Полученное слово зафиксируется в регистре 14 вершины (-

Шаг 4. Начинается анализ поведения и контроль с пробником входных сигналов очередного компонента объекта, на выходе которого обнаружен ложный сигнал. Происходит фиксирование эталонного значения Е сигнала на выходе компонента в триггере 27 (г.) снятие признака Сдвиг во времени путем сброса триггера 19 (Y ),Если осуществлен переход из такта t в такт t-1, снятие этого признака означает , что анализ поведения компонента осуществляется для т.н. предыдущего набора в такте t-. Подготавливается адрес для обращения к начальной вершине графа компонента (10 ц) и зафиксируется в регистре. 13 (Y,,

Шаг 5. Происходит чтение информационного слова очередной вершины m АГ по адресу в регистре 13 из блока 3 памяти (4) и запись его в регистр 14 (Y ), При отсутствии признака сдвига во времени (X g 0) в триггере 26 зафиксируется эталонное значение сигнала на входе Z(А),найденное в блоке 7 памяти по адресу ) (Yj), затем переход к шагу 7, В случае X g 1 эталонное значение сигнала Z(m) находится из предыдущего такта на шаге 6.

Шаг 6. Осуществляется сдвиг обратно во времени. Из счетчика 6 вычитается единица (Y), затем считывается из блока 7 памяти набор, соответствующий предьздущему такту (Y,), находится эталонное значение переменной Z(m) по адресу ) и передается в триггер 26 (2)« Затем восстанавливается в счетчике 6 пре- дьщущее значение, соответствующее адресу текущего набора текста (Yj).

58016

Шаг 7. Определяется необходимость проверки сигнала пробником. Если у(тп) 1 (Х(,1), проверка требуется, происходит переход к шагу 11. В об- , ратном случае применяется правило направления. В случае, когда направление выхода из вершины и направление выхода моделируемого пути из графа совпадают, требуется также проO верка и происходит переход к шагу 11. Проверка этих совпадений осуществляется схемой 18 (по сигналу Х ),где сравниваются эталонное значение Е, взятое из триггера 27, и значение

5 Z(m)i взятое с прямого вькода триггера 26, если jb (га) О (Хд 0), и с обратного выхода триггера 26 (), если (т) 1 (X g 1). В случае, когда направление выхода из

0 вершины и из графа не совпадают,проверка не требуется и процесс моделирования продолжается. Происходит переход к шагу 8 для определения адреса А(т) очередной вершины на пути,

5 Шаг 8. Определяется адрес следующей вершины (Y,o или Y ) в зависимости от направления выхода из вершины и запись его в регистр 13 (), Осуществляется проверка окончания

0 пути. При нулевом адресе А(т) О () путь окончен и происходит переход к шагу 9. В противном случае продолжается моделирование, переход к шагу 10.

Шаг 9. Процесс диагностирования закончен. На табло блока 2 индицируется надпись Неисправность локализована (Y,), в блок 2 для индикации выдается также адрес локализованного дефектного компонента К(т) , (), устройство останавливается (Yj) ,

Шаг 10, В случае, когда при контроле пробником сигнала потребовался сдвиг в предьщущий такт во времени (X 2 1), восстанавливается текущий набор теста. Для этого увеличивается адрес в счетчике 6 на единицу (5 происходит чтение набора из блока 7 памяти (Y) и передача его в блок 8 (Yg) для реализации на контролируемом блоке 12. Признак Сдвиг во времени снимается (Y),

0

5

Возвращение к шагу 5.

Шаг 11. Если сдвига во времени не требуется, тСт) О, (Хр 0), на табло блока 2 индикации выдается указание оператору для очередной oneрации с пробником, высвечивается надпись Поставить пробник (з вьщаются адрес микросхемы К(т) (Y ) вместе с номером N(m) ее контакта (. ) , Устройство приостанавливает- 5 ся для ожидания действия оператора. Переход к шагу 15,

Шаг 12. Если требуется сдвиг во времени, Т(т) 1 (Xg 1), осуществляется переход к предыдущему так- 10 ту t.-l, Для этого путем вычитания единицы из счетчика 6 (V) зафиксируется адрес набора этого такта и передается на хранение в регистр 23 (Yg)

Шаг 13, Происходит возвращение 15 к набору, соответствующему сегмента теста, Для этого вычитается циклически единица (Y) из счетчика 6 и проводится чтение блока 7 памяти (Y ) ,

рованию и проверке которог.о необходимо поступить ( , Y), Если адрес-А д(га) является нулевым (Х7 l)i неисправность локализована, так как контрольная точка Z(m) соответствует первичному входу проверяемого объекта 12, осуществляется переход к шагу 17 для вьщачи результата диагностирования, В противном случае начинается процесс моделирования нового компонента путем перехода к шагу 4,

Шаг 17, Процесс диагностирования закончен. Па табло блока 2 индицируется надпись Неисправность локализована (Y), в блок 2 для индикации выдаются также адрес К(т) рассматриваемого компонента () и номер его дефектного входного контакта

пока не находится признак начала сег-20 N(m), (). Устройство останавливамента (Хд 1) в некоторой ячейки ется, блока 7 памяти.

Шаг 14, Осуществляется циклическая реализация теста путем чтения из блока 7 памяти наборов (Y-,) , по- 5 дачи их на блок 12 (Yg) и последующей иНкрементации адресного счетчика 6 (Yy), начиная с найденного в шаге 13 адреса набора и кончая с наФормула изобретения

Устройство для контроля и диагностики цифровых блоков, содержащее блок микропрограммного управления, .блок памяти тестовой информации,блок индикации, логический пробник,счетбором, адрес которого передан на, хра-30 чик адресов, блок сравнения, формирователь входных сигналов, шифратор, регистр и элемент PtlTH, причем первый, второй, третий и четвертый выходы блока микропрограммного управления

40

нение в регистр 23, Признаком окончания этого процесса является совпадение адресов в счетчике 6 и регистре 23 (Х 1), Затем устанавливается

признак Сдвиг во времени (Y.,) про-35 о Динены соответственно исходит переход к шагу 11 для вьщачи указания оператору.

Шаг 15, После пуска устройства нажатием на кнопку 10 происходит сравнение в блоке 18 эталонного сигнала контрольной точки Z(in), запомненного в триггере 26, и реального сигнала, найденного с пробником и зафиксированного в триггере 28 (Yj), При совпадении этих сигналов () продолжается процесс моделирования: на этом пути и происходит переход к шагу 8, При несовпадении этих сигналов, т,е, при обнаружении с пробником ложного сигнала осуществляется переход к моделированию и проверке следующего, компонента, выход которого соединен с данной контрольной точкой, где обнаружен ложный сигнал (переход к шагу 16),

Шаг 16. Выбирается адрес Ац(ю), начальной вершины графа, представляющего новый компонент, к моделиватель входных сигналов, регистр и элемент PtlTH, п второй, третий и четверты блока микропрограммного

сложения и вычитания сче сов, управляющими входам мяти тестовой информации информационные входы кот нены с выходами тестовых блока памяти тестовой ин а первая группа выходов группой входов блока сра рая группа входов которо

45 ся группой входов устрой

подключения к выходам ко го блока, вторая группа гистра соединена с входа вателя вход1 ых сигналов,

50 торого образуют группу вы ройства для подключения контролируемого блоки., г дов блока сравнения соед дами шифратора и элемент ход счетчика адресов сое ресным входом блока памя }шформации, ;выход эталон ций которого и выход элем соединены соответственно

55

рованию и проверке которог.о необходимо поступить ( , Y), Если адрес-А д(га) является нулевым (Х7 l)i неисправность локализована, так как контрольная точка Z(m) соответствует первичному входу проверяемого объекта 12, осуществляется переход к шагу 17 для вьщачи результата диагностирования, В противном случае начинается процесс моделирования нового компонента путем перехода к шагу 4,

Шаг 17, Процесс диагностирования закончен. Па табло блока 2 индицируется надпись Неисправность локализована (Y), в блок 2 для индикации выдаются также адрес К(т) рассматриваемого компонента () и номер его дефектного входного контакта

Формула изобретения

Устройство для контроля и диагностики цифровых блоков, содержащее блок микропрограммного управления, .блок памяти тестовой информации,блок индикации, логический пробник,счетчик адресов, блок сравнения, формиро

о Динены соответственно

ватель входных сигналов, шифратор, регистр и элемент PtlTH, причем первый, второй, третий и четвертый выходы блока микропрограммного управления

с входами

сложения и вычитания счетчика адресов, управляющими входами блока памяти тестовой информации и регистра, информационные входы которого соединены с выходами тестовых воздействий блока памяти тестовой информации, а первая группа выходов - с первой группой входов блока сравнения,вторая группа входов которого является группой входов устройства для

подключения к выходам контролируемого блока, вторая группа выходов регистра соединена с входами формирователя вход1 ых сигналов, выходы которого образуют группу выходов устройства для подключения к входам контролируемого блоки., группа выходов блока сравнения соединена с входами шифратора и элемента ИЖ, выход счетчика адресов соединен с адресным входом блока памяти тестовой }шформации, ;выход эталонных реакций которого и выход элемента ИЛИ соединены соответственно с первым

19

и вторый входами логических условий блока микропрограммного управления, вход устано-вки в исходное состояние которого и установочный вход счетчика соединены с установочным входом устройства, пятый выход блока микропрограммного управления соединен с управляющим входом блока индикации, а третий вход логического условия - с входом пуска процесса контроля устройства, вход логического пробника соединен с контрольными точками контролируемого блока, отличающееся тем, что, с целью повышения производительности за счет сокращения -объема ручных операций, оно содержит блок памяти модели объекта и блок анализа контрольных точек, состоящий из трех регистров, пяти мультиплексоров, двух схем сравнения, пяти триггеров, коммутатора и дешифратора нуля, причем информационные вход и выход первого регистра соединены соответственно с выходом первого мультиплексора и адресным входом блока памяти модели объекта, управляющий вход и выход которого соединены соответственно с шестым выходом блока микропрограммного управления и информационным входом второго регистра, первая группа разрядных выходов которого соединена с группой информационных входов второго мультиплексора, группа выходов которого соединена с группой входов дешифратора нуля и первой группой информационных входов первого мультиплексора, вторая группа информационных входов которого соединена с группой выходов шифратора, первый, второ разрядные выходы второго регистра соединены соответственно с первым и вторым информационными входами коммутатора, выход которого соединен с информационным входом блока инд 1кации.

1

W

258020

выходы третьего и четвертого мультиплексоров соединены соответственно с первым и вторым входами первой схемы сравнения, первый и вто- 5 рой информационные входы третьего мультиплексора соединены соответственно с первым и вторым выходами первого триггера, первый и второй информационные входы четвертого мультиплексора соединены соответственно с выходами второго и третьего триггеров, информационные входы первого и второго триггеров соединены с выходом пятого мультицлексора,ин-f5 формационный и управляющий входы которого соединены соответственно с выходами тестовых воздействий блока памяти тестовой информации и третьим разрядным ВЕ 1ходом второго регистра, информационный вход третьего триггера соединен с выходом логического пробника, а синхровход и вход сброса четвертого триггера объединены и подключены к входу пуска процесса диагностики устройства, первый вход второй схемы сравнения соединен с выходом счетчика адресов и с информационным входом третьего регистра, выход которого соединен с

30 вторым входом второй схемы сравнения, выход которой, выходы четвертого и пятого триггеров, дешифратора нуля, первой схемы сравнения и вторая группа выходов второго регистра

35 соединены с группой входов логических условий блока микропрограммного управления, выходы группы которого соединены с управляющими входами коммутатора, первого, второго и третье40 го регистров, первого, второго,

третьего и четвертого мультиплексоров, первым и вторым установочными входами пятого триггера, синхровхо- дами первого и второго триггеров иуста45 новочным входом четвертого триггера.

20

25

Индикация Неисправность локализована

Индикация Годен

Таблица 2

Пуск процесса контроля Тест закончен Начало сегмента теста Найден ложный сигнал

Пуск процесса поиска неисправности

Найден нужный входной набор Признак нулевого адреса Признак сдвига во времени Т(т Признак инвертирования (т) Признак проверки (т) Совпадение значений сигналов

Признак Бьш осуществлен сдвиг во времени

Значение эталонного значения Исходная установка

86лМ16)

«

вел.з

ел.б i

8SA.5 ВблЛ

BSA.8 BSnf

В 6л.1

с

во

Sj -N

ЯГ

{Конец

Редактор Н.Рогулич

Составитель И.Хазова Техред Н.Глущенко

Заказ 2675Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

,« - ,ы--ч..- -- - - -.-.- - - - -.- - - - -- - - ---- - -. -- - --:- -.

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Фи&М

Корректор И.Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля синхронных цифровых узлов | 1984 |

|

SU1242964A1 |

| Устройство для тестового контроля больших интегральных схем | 1984 |

|

SU1218390A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

Изобретение позволяет в диалоговом режиме перед каждым шагом проверки с логическим пробником провести промежуточный анализ ситуации и . определить контрольные точки, проверка которых на данном шагу нужна, и соответственно отсеивать ненужные точки. Цель изобретения - повьппение производительности устройства за счет сокращения числа ручных операций. Устройство включает блок 8 сопряжения, к которому подключается (Л со 0 ел 00

| Устройство для контроля логических схем | 1976 |

|

SU595735A1 |

| Патент США № 4161276, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

Авторы

Даты

1987-05-23—Публикация

1985-12-06—Подача