Изобретение относится к технической кибернетике и предназначено для построения распознавающих устройств и устройств автоматического управле- ния динамическими объектами в реальном масштабе времени.

Цель изобретения - повышение быстродействия и упрощение устройства.

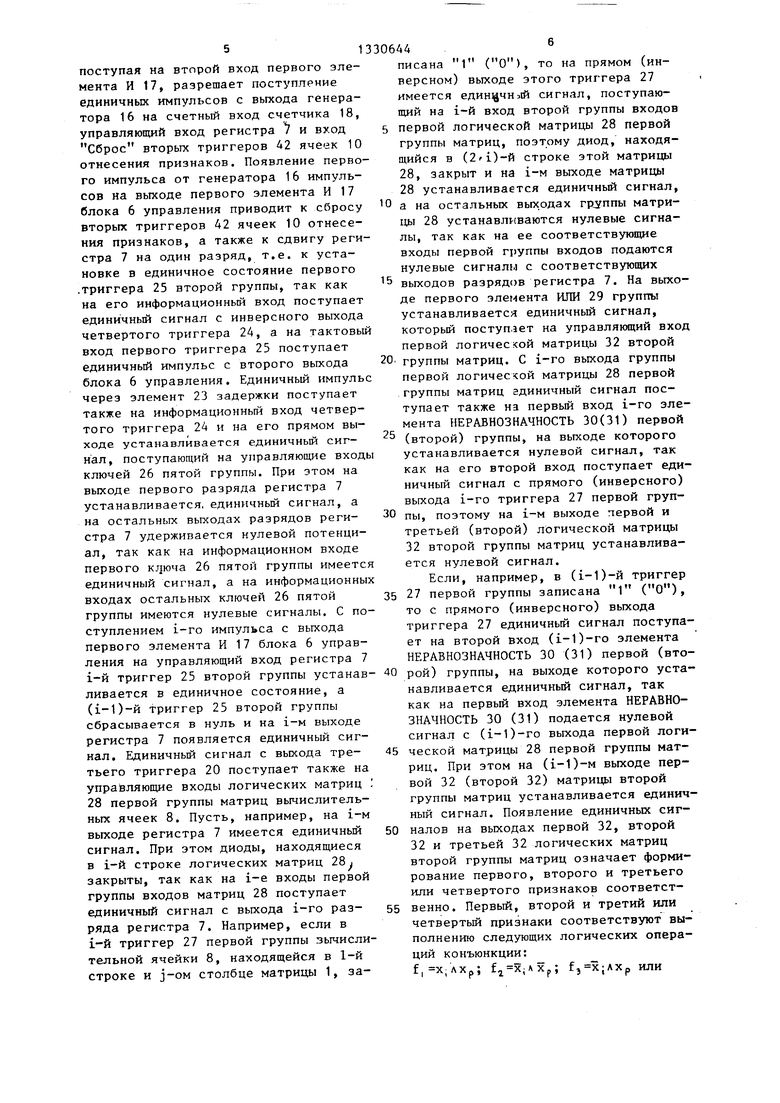

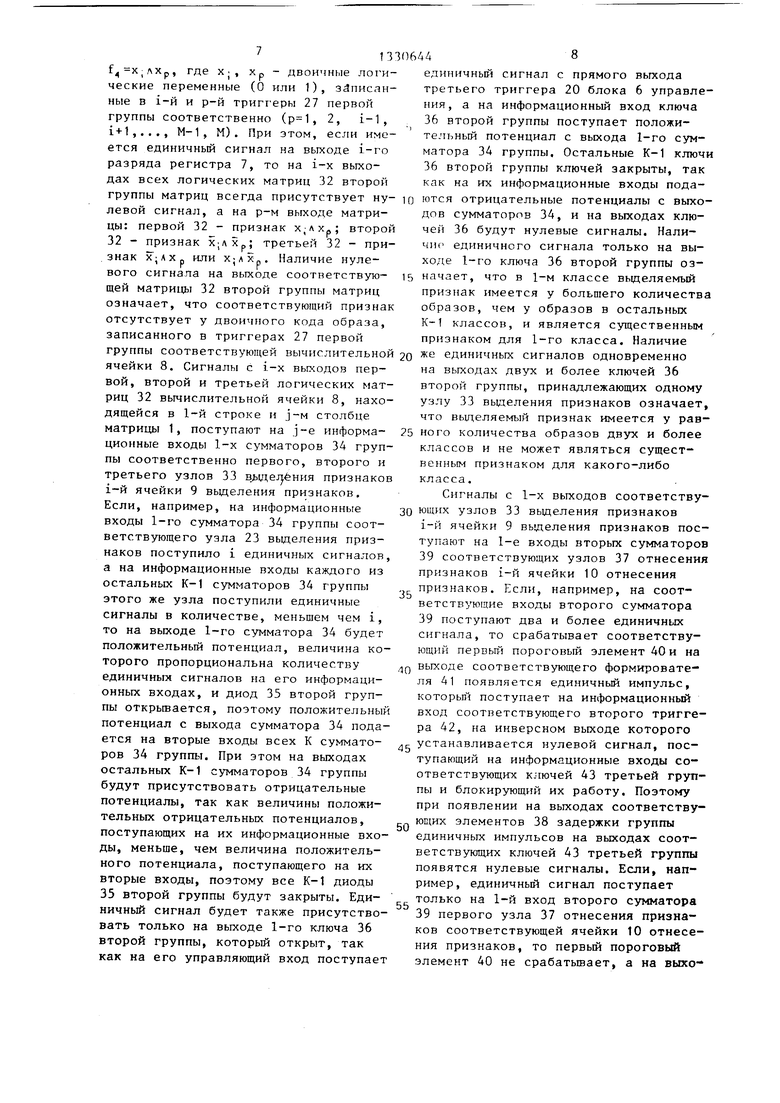

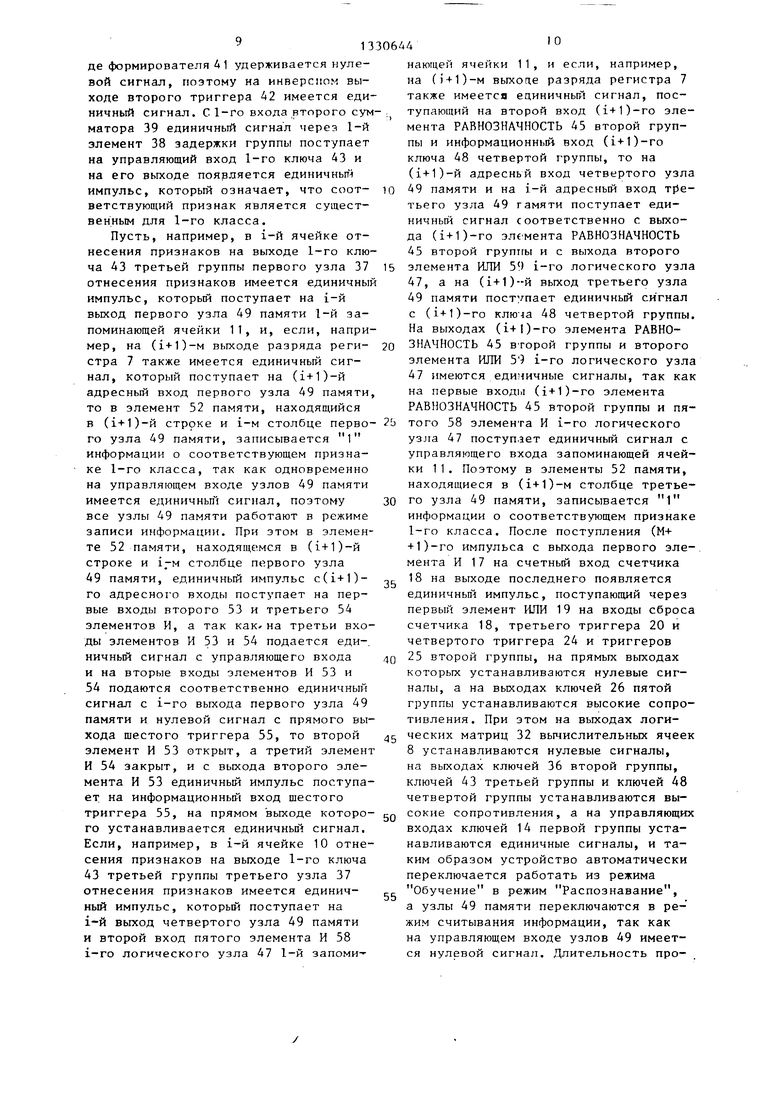

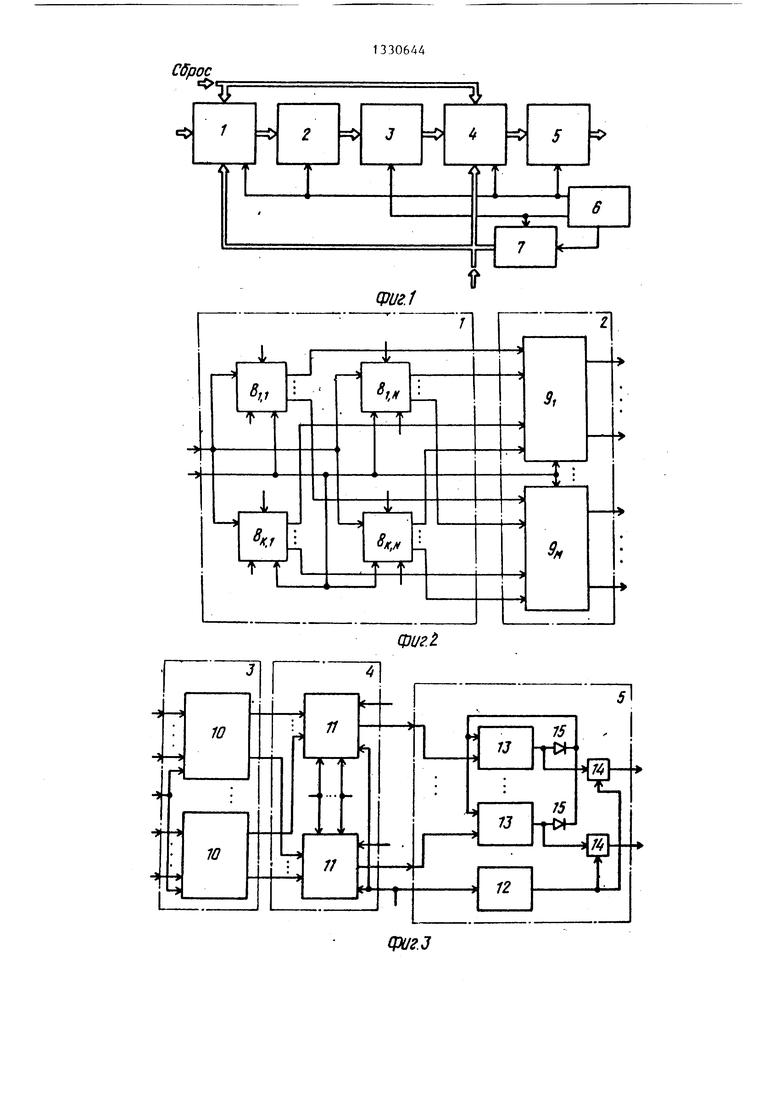

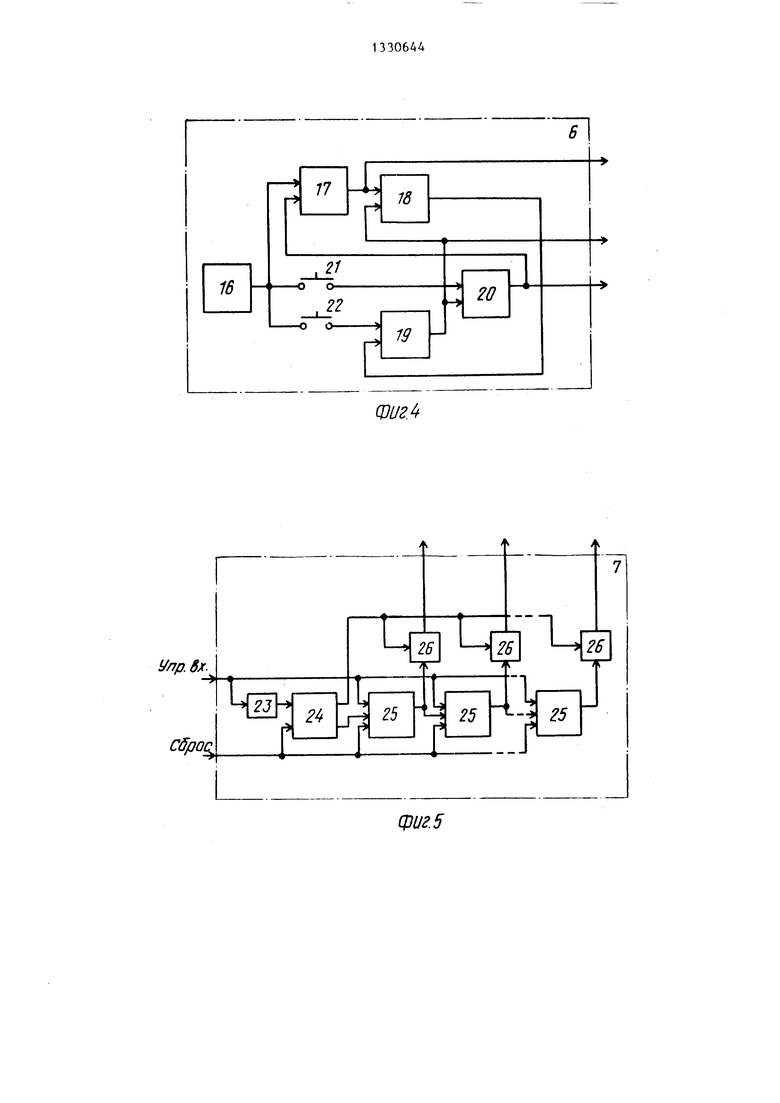

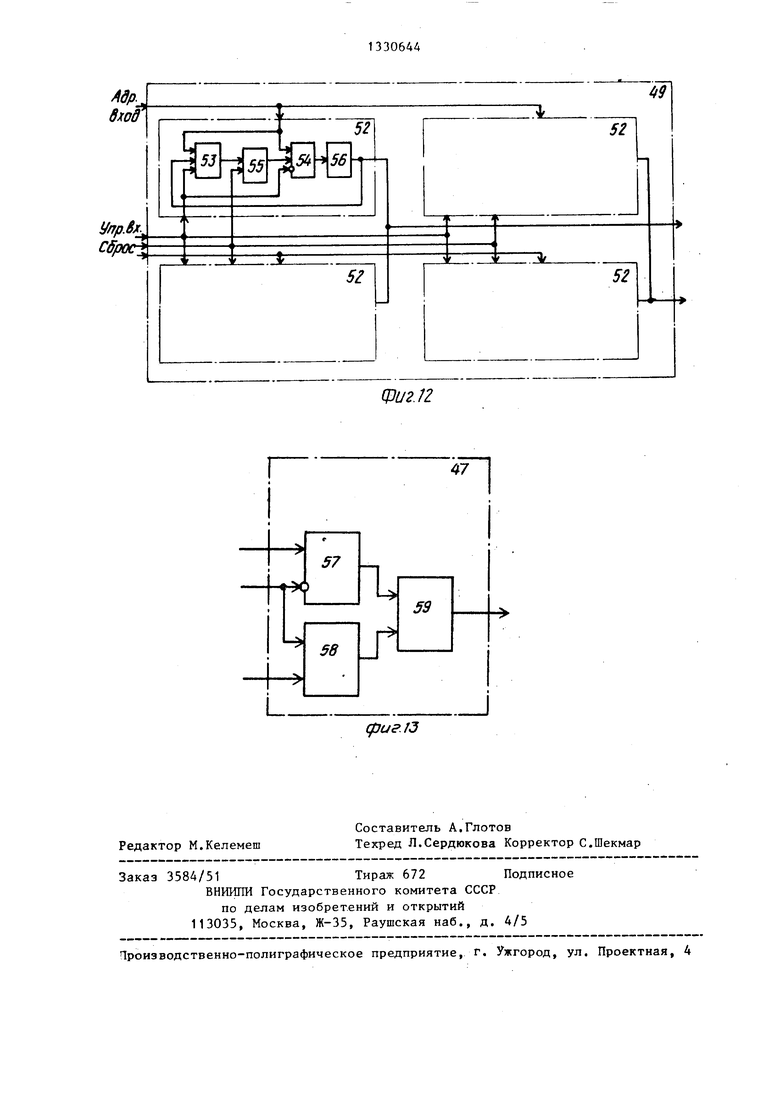

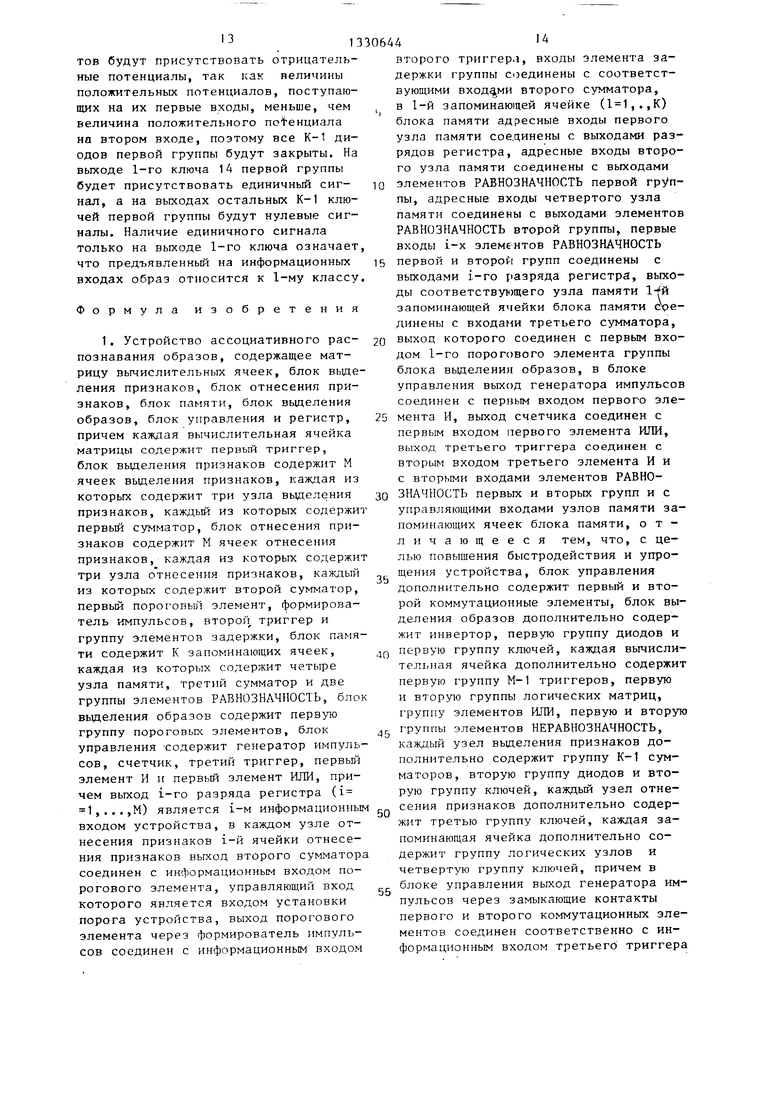

На фиг.1 представлена блок-схема устройства; на фиг.2 - блок-схемы матрицы вычислительных ячеек и блока вьщеления признаков; на фиг.З - схем блока отнесения признаков, блока памяти и блока вьиеления образов; на фиг.4 - схема блока управления; на фиг.З - блок-схема регистра; на фиг, 6 блок-схема вычислительной ячейки; на фиг.7 - блок-схема ячейки выделения признаков; на фиг,8 - блок-схема ячейки отнесения признаков; на фиг.9 блок-схема запоминающей ячейки; на фиг.10 - схема логической матрицы первой группы; на фиг,11 - то же, второй группы; на фиг,12 - блок-схе ма узла памяти; на фиг,13 - блок- схема логического узла,

Устройство ассоциативного распознавания образов (фиг,1) содержит матрицу 1 вычислительных ячеек, блок 2 вьщеления признаков, блок 3 отнесения признаков, блок 4 памяти, блок 5 выделения образов, блок 6 управления, регистр 7,

Матрица 1 вычислительных ячеек содержит вычислительные ячейки 8, Блок 2 выделения признаков содержит ячейки 9 вьщеления признаков (фиг.2) Блок 3 отнесения признаков содержит ячейки 10 отнесения признаков, блок 4 памяти - запоминающие ячейки 11, а блок 5 вьщеления образов - инвертор 12, первую группу пороговых элементов 13, первую группу ключей 14, первую группу диодов 15 (фиг.З),

Блок 6 управления (фиг,4) содержит генератор 16 импульсов, первый элемент И 17, счетчик 18 импульсов, первый элемент ИЛИ 19, третий триггер 20, первый 21 и второй 22 коммутаци- онные элементы.

Регистр 7 (фиг,5) содержит элемент 23 задержки, четвертый триггер 24, вторую группу триггеров 25, пятую группу ключей 26,

J Вычислительная ячейка 8 (фиг.6) содержит первую группу из М первых триггеров 27, первую группу логических матриц 28, группу элементов ИЛИ

29, первую 30 и вторую 31 группы элементов НЕРАВНОЗНАЧНОСТЬ, вторую группу логически матриц 32.

Ячейка 9 выделения признаков (фиг.7) содержит три узла 33 вьщеле- ния признаков, каждый из которых содержит группу п грвых сумматоров 34, вторую группу Д)1одов 35, вторую группу ключей 36.

Ячейка 10 отнесения признаков (фиг,В) содержит три узла 37 отнесения признаков, каждый из которых содержит группу элементов 38 задержки, второй сумматор 39, первый пороговый элемент 40, формирователь 41 импульсов, второй триггер 42, третью группу ключей 43.

Запоминающая ячейка 11 (фиг.9) содержит первую 44 и вторую 45 группы из М элементов РАВНОЗНАЧНОСТЬ, третий сумматор 46, гр уппу логических узлов 47, четвертую г руппу ключей 48, четыре узла 49 памяти.

Логическая матрица 28 первой группы (фиг, 10) пре дставляет собой конъюнктивную матрицу диодов, катоды которых подключены к строкам, а аноды - к столбцам (наличие диода между соответствующими строками и столбцами условно показано в виде точки а). В матрице 28 имеются по количеству столбцов М нагрузочных резисторов 50, управляющий вход, первая и вторая группы из М входов и группа из М выходов , При наличии на катоде хотя бы одного диода нулевого потенциала, что соответствует логическому О, этот диод открывается и на соответствующем выходе устанавливается также сигнал логического О.

Логическая матрица 32 второй группы (фиг,11) представляет собой коньюн- ктивную матрицу диодов, катоды которых подключены к строкам, а аноды - к столбцам (наличие диода между соответствующими строками и столбцами условно показано в виде точки а), В матрице 32 имеются по количеству столбцов М нагрузочных резисторов 51, группа из М входов, управляющий вход и группа из М выходов.

Узел 49 памяти (фиг,12) содержит матрицу элементов 52 памяти, каждый из которых содержит второй 53 и третий 54 элементы И, шестой триггер 55, транзисторный ключ 56,

Логический узел 47 (фиг.13) содержит четвертый 57 и пятый 58 элементы И, второй элемент ИЛИ 59.

Устройство ассоциативного распоз- навания образов работает следующим образом.

Имеются два режима работы устройства: Обучение и Распознавание. В режиме обучения учитель перед на чалом работы устройства устанавливае третий 20 и четвертый 2А триггеры, вторую группу триггеров 25 и, счетчик 18 в нулевое состояние путем замыкания контактов второго коммутационног элемента 22 блока 6 управления. При этом единичные импульсы с выхода генератора 16 импульсов через замкнуты контакты второго коммутационного элемента 22 поступают на второй вход первого элемента ИЛИ 19, с выхода которого единичный импульс поступает на входы сброса счетчика 18, четвертого триггера 24, триггеров 25 второ группы и третьего триггера 20. На прямом выходе последнего устанавливается йулевой потенциал, блокирующий работу первого элемента И 17, и единичные импульсы с выхода генератора на счетный вход счетчика не поступают. Нулевой потенциал с выхода третьего триггера поступает также на управляющие входы логических матриц 28 первой группы матриц вычислительных ячеек 8, поэтому диоды логических матриц закрыты, а на выходах матриц устанавливаются нулевые потенциалы, поступающие на входы элементов ИЛИ 29 группы. На выходе последних также устанавливаются нулевые потенциалы, которые поступают на управляющие ВХОДЫ логических матриц 32 второй группы матриц, поэтому диоды логических матриц также закрыты, а на выходах матриц устанавливаются нулевые потенциалы, поступающие на информационные входы соответствующих сумматоров ЗА группы ячеек 9 выделения признаков, и на выходах сумматоров также устанавливаются нулевые потенциалы. Первый сумматор ЗА представляет собой суммирующий операционный усилитель, инверсный вход которого является вторым входом сумматора, а неинвертирующий вход - информационным входом сумматора. При этом ключи 36 второй группы закрыты, так как на их управляющие входы поступает нулевой потенциал с прямого выхода третьего

0

5

s

0

5

0

5

0

5

триггера 20 блока 6 управления, следовательно, на выходах ключей 36 второй группы имеется высокое сопротивление и выходы первых сумматоров ЗА отключены от соответствующих информационных входов вторых сумматороа 39 ячеек 10 отнесения признаков. Поэтому на вых одах группы элементов 38 задержки имеются нулевые потенциалы, поступающие на управляющие входы ключей A3 третьей группы, на выходах которых yctaнaвливaeтcя высокое сопротивление, и выходы группы элементов 38 задержки отключены от соответствующих адресных входов узлов А9 памяти запоминающих ячеек 11. С прямого выхода третьего триггера 20 нулевой потенциал поступает также на управляющие входы узлов А9 памяти запоминающих ячеек 11, устанавливая все узлы в режим считывания информации, на выходах ключей А8 четвертой группы устанавливается высокое сопротивление, так как на их управляющие входы поступает нулевой потенциал с управляющего входа. Затем учитель устанавливает первую группу триггеров 27 и шестые триггеры 55 соответственно матрицы вычислительных ячеек 1 и блока А памяти в нулевое состояние путем подачи на соответствующие входы Сброс устройства единичных сигналов. Информация о предъявленных образах в виде М-разрядного двоичного кода записывается учителем во все N столбцов вычислительных ячеек 8 матрицы 1 всех К классов путем подачи единичных импульсов на соответствующие входы Установка устройства со- ответствующих триггеров 27 первой группы. При этом в каждую строку матрицы 1 записывается информация об образах, принадлежащих одному классу, а информация о каждом образе - в М триггеров 27 первой группы каждой вычислительной ячейки 8. После установки первой группы триггеров 27 учитель осу1цествляет переключение устройства в режим Обучение путем замыкания контактов первого коммутационного элемента 21 блока 6 управления. При этом единичные импульсы с выхода генератора импульсов через замкнутые контакты первого коммутационного элемента 21 поступают на информационный вход третьего триггера 20 и на его прямом выходе устанавливается единичный сигнал, которьй

поступая на второй вход первого элемента И 17, разрешает поступление единичных импульсов с выхода генератора 16 на счетный вход счетчика 18, управляющий вход регистра и вход Сброс вторых триггеров 42 ячеек 10 отнесения признаков. Появление первого импульса от генератора 16 импульсов на выходе первого элемента И 17 блока 6 управления приводит к сбросу вторых триггеров 42 ячеек 10 отнесения признаков, а также к сдвигу регистра 7 на один разряд, т.е. к установке в единичное состояние первого .триггера 25 второй группы, так как на его информационньй вход поступает единичный сигнал с инверсного выхода четвертого триггера 24, а на тактовый вход первого триггера 25 поступает единичный импульс с второго выхода блока 6 управления. Единичный импульс через элемент 23 задержки поступает также на информационньй вход четвертого триггера 24 и на его прямом выходе устанавливается единичный сигнал, поступающий на управляющие входы ключей 26 пятой группы. При этом на выходе первого разряда регистра 7 устанавливается, единичньш сигнал, а на остальных выходах разрядов регистра 7 удерживается нулевой потенциал, так как на информационном входе первого к;|юча 26 пятой группы имеется единичный сигнал, а на информационных входах остальных ключей 26 пятой группы имеются нулевые сигналы. С поступлением i-ro импульса с выхода первого элемента И 17 блока 6 управления на управляющий вход регистра 7 i-й триггер 25 второй группы устанавливается в единичное состояние, а (1-1)-й триггер 25 второй группы сбрасывается в нуль и на i-м выходе регистра 7 появляется единичный сигнал. Единичный сигнал с выхода третьего триггера 20 поступает также на управляющие входы логических матриц 28 первой группы матриц вычислительных ячеек 8, Пусть, например, на i-м выходе регистра 7 имеется единичный сигнал. При этом диоды, находящиеся в i-й строке логических матриц 28j закрыты, так как на i-e входы первой группы входов матриц 28 поступает единичный сигнал с выхода i-ro разряда регистра 7, Например, если в 1-й триггер 27 первой группы вычислительной ячейки 8, находящейся в 1-й строке и J-OM столбце матрицы 1, за0

0,

писана 1 (О), то на прямом (инверсном) выходе этого триггера 27 имеется единучнзй сигнал, поступающий на i-й вход второй группы входов 6 первой логической матрицы 28 первой группы матриц, поэтому диод, находящийся в (2 i)-й строке этой матрицы 28, закрыт и на i-м выходе матрицы 28 устанавливается единичный сигнал, а на остальных вых.одах группы матрицы 28 устанавливаются нулевые сигналы, так как на ее соответствующие входы первой группы входов подаются нулевые сигналы с соответствующих

выходов разрядов регистра 7. На выходе первого ИЛИ 29 группы устанавливается единичный сигнал, который постуПсЗет на управляющий вход первой логической матрицы 32 второй группы матриц. С i-ro выхода группы первой логической матрицы 28 первой группы матриц единичный сигнал поступает также на первый вход i-ro элемента НЕРАВНОЗНАЧНОСТЬ 30(31) первой

(второй) группы, на выходе которого устанавливается нулевой сигнал, так как на его второй вход поступает единичный сигнал с прямого (инверсного) выхода i-ro триггера 27 первой группы, поэтому на i-M выходе первой и третьей (второй) логической матрицы 32 второй группы матриц устанавливается нулевой сигнал.

Если, например, в (i-1)-й триггер 27 первой группы записана 1 (О), то с прямого (инверсного) выхода триггера 27 единичный сигнал поступает на второй вход (i-l)-ro элемента НЕРАВНОЗНАЧНОСТЬ 30 (31) первой (второй) группы, на выходе которого устанавливается единичный сигнал, так как на первый вход элемента НЕРАВНОЗНАЧНОСТЬ 30 (31) подается нулевой сигнал с (i-l)-ro выхода первой логи5 ческой матрицы 28 первой группы матриц. При этом на (i-l)-M выходе первой 32 (второй 32) матрицы второй группы матриц устанавливается единичный сигнал. Появление единичных сиг0 налов на выходах первой 32, второй 32 и третьей 32 логических матриц второй группы матриц означает формирование первого, второго и третьего или четвертого признаков соответст5 венно. Первый, второй и третий или четвертый признаки соответствуют выполнению следующих логических операций конъюнкции:

0

5

0

,лхр;

Х(ЛХр;

f5 XjAXp ИЛИ

1330644

, где Xj, Хр - двоичные логи-единичный сигнал с прямого выхода

ческие переменные (О или 1), записан-третьего триггера 20 блока 6 управленые в i-й и р-й тригг еры 27 первойния, а на информационный вход ключа

группы соответственно (, 2, ,36 второй группы поступает положиi+1,..., М-1, М). При этом, если имс-тельный потенциал с вьсхода 1-го сумется единичный сигнал на выходе i-roматора 34 группы. Остальные К-1 ключи

разряда регистра 7, то на i-x выхо-36 второй группы ключей закрыты, так

дах всех логических матриц 32 второйкак на их информационные входы пода- группы матриц всегда присутствует ну- ю ются отрицательные потенциалы с выхолевой сигнал, а на р-м выходе матри-дов сумматоров 34, и на выходах клюцы: первой 32 - признак х,лхр; второйчей 36 будут нулевые сигналы. Нали32 - признак Х;лх„; третьей 32 - при-чио единичного сигнала только на вызнак А X р или х;АХр. Наличие нуле-ходе 1-го ключа 36 второй группы оз- вого сигнала на выходе соответствую- 15 начает, что в 1-м классе выделяемый

щей матрицы 32 второй группы матрицпризнак имеется у большего количества

означает, что соответствующий признакобразов, чем у образов в остальных

отсутствует у двоичного кода образа,К-1 классов, и является существенным

записанного в триггерах 27 первойпризнаком для 1-го класса. Наличие группы соответствующей вычислительной 2о единичных сигналов одновременно

ячейки 8. Сигналы с i-x выходов пер-на выходах двух и более ключей 36

вой, второй и третьей логических мат-второй группы, принадлежающих одному

риц 32 вычислительной ячейки 8, нахо-узлу 33 выделения признаков означает,

дящейся в 1-й строке и j-м столбцечто выделяемый признак имеется у рав- матрицы 1, поступают на j-e информа- 25 но го количества образов двух и более

ционные входы 1-х сумматоров 34 груп-классов и не может являться сущестпы соответственно первого, второго ивенным признаком для какого-либо

третьего узлов 33 признаковкласса.

i-й ячейки 9 вьщеления признаков. Сигналы с 1-х выходов соответству- Если, например, на информационные зо ющих узлов 33 выделения признаков входы 1-го сумматора 34 группы соот-i-й ячейки 9 выделения признаков пос- ветствующего узла 23 выделения приз-тупают на 1-е входы вторьпс сумматоров наков поступило i единичных сигналов,39 соответствующих узлов 37 отнесения а на информационные входы каждого изпризнаков i-й ячейки 10 отнесения остальных К-1 сумматоров 34 группыпризнаков. Если, например, на соот- этого же узла поступили единичныеветствующие входы второго сумматора сигналы в количестве, меньшем чем i,39 поступают два и более единичных то на выходе 1-го сумматора 34 будетсигнала, то срабатывает соответству- положительный потенциал, величина ко-ющий первый пороговый элемент 40 и на торого пропорциональна количеству ,JQ выходе соответствующего формировате- единичньм сигналов на его информаци-ля 41 появляется единичный импульс, онных входах, и диод 35 второй груп-которьй поступает на информационный пы открьшается, поэтому положительныйвход соответствующего второго тригге- потенциал с выхода сумматора 34 пода-ра 42, на инверсном выходе которого ется на вторые входы всех К суммато- устанавливается нулевой сигнал, пос- ров 34 группы. При этом на выходахтупающий на информационные входы со- остальных К-1 сумматоров 34 группыответствующкх ключей 43 третьей груп- будут присутствовать отрицательныепы и блокирующий их работу. Поэтому потенциалы, так как величины положи-при появлении на выходах соответству- тельных отрицательных потенциалов, элементов 38 задержки группы поступающих на их информационные вхо-единичных импульсов на выходах соот- ды, меньше, чем величина положитель-ветствующих ключей A3 третьей группы кого потенциала, поступающего на ихпоявятся нулевые сигналы. Если, нап- вторые входы, поэтому все К-1 диодыример, единичный сигнал поступает 35 второй группы будут закрыты. Еди-только на 1-й вход второго сумматора ничньй сигнал будет также присутство-39 первого узла 37 отнесения признавать только на выходе 1-го ключа 36ков соответствующей ячейки 10 отнесе- второй группы, который открыт, такния признаков, то первый пороговый как на его управляющий вход поступаетэлемент 40 не срабатьшает, а на выхо

де формирователя 41 удерживается нулевой сигнал, поэтому на инверсном выходе второго триггера 42 имеется единичный сигнал. С 1-го входа второго сумматора 39 единичный сигнал через 1-й элемент 38 задержки группы поступает на управляющий вход 1-го ключа 43 и на его выходе появляется единичный импульс, который означает, что соответствующий признак является существенным для 1-го класса.

Пусть, например, в i-й ячейке отнесения признаков на выходе 1-го ключа A3 третьей группы первого узла 37 отнесения признаков имеется единичный импульс, который поступает на i-й выход первого узла 49 памяти 1-й запоминающей ячейки 11, и, если, например, на (i+1)-M выходе разряда регистра 7 также имеется единичный сигнал, который поступает на (1+1)-й

адресный вход первого узла 49 памяти то в элемент 52 памяти, находящийся в (1-|-1)-й строке и i-M столбце перво го узла 49 памяти, записывается 1 информации о соответствующем признаке 1-го класса, так как одновременно на управляющем входе узлов 49 памяти имеется единичньш сигнал, поэтому все узлы 49 памяти работают в режиме записи информации. При этом в элементе 52 памяти, находящемся в (1+1)-й строке и i.-M столбце первого узла 49 памяти, единичный импульс c(i+1)- го адресного входы поступает на первые входы второго 53 и третьего 54 элементов И, а так как на третьи входы элементов И 53 и 54 подается еди-. ничньй сигнал с управляющего входа и на вторые входы элементов И 53 и 54 подаются соответственно единичный сигнал с i-ro выхода первого узла 49 памяти и нулевой сигнал с прямого выхода шестого триггера 55, то второй элемент И 53 открыт, а третий элемент И 54 закрыт, и с выхода второго элемента И 53 единичный импульс поступает на информационный вход щестого триггера 55, на прямом выходе которого устанавливается единичньпЧ сигнал. Если, например, в i-й ячейке 10 отнесения признаков на выходе 1-го ключа 43 третьей группы третьего узла 37 отнесения признаков имеется единичный импульс, который поступает на i-й выход четвертого узла 49 памяти и второй вход пятого элемента И 58 i-ro логического узла 47 1-й запоми

0

5

0

5

нающей ячейки 11, и если, например, на ())-м выхоае разряда регистра 7 также имеется единичный сигнал, поступающий на второй вход (i+l)-ro элемента РАВНОЗНАЧНОСТЬ 45 второй группы и информационный вход (i+1)-ro ключа 48 четвертой группы, то на (i+1)-й адресньй вход четвертого узла

0 А9 памяти и на i-й адресный вход третьего узла 49 гамяти поступает единичный сигнал соответственно с выхода (i+1)-ro элемента РАВНОЗНАЧНОСТЬ 45 второй груптгы и с выхода второго

5 элемента ИЛИ 59 i-ro логического узла 47, а на ()й выход третьего узла 49 памяти поступает единичный си гнал с (i-f-l)-ro ключа 48 четвертой группы. На выходах (i-bl)-ro элемента РАВНОЗНАЧНОСТЬ 45 второй группы и второго элемента ИЛИ 59 i-ro логического узла 47 имеются единичные сигналы, так как на первые входы (i+1)-ro элемента РАВНОЗНАЧНОСТЬ 45 второй группы и пятого 58 элемента И i-ro логического узла 47 поступает единичный сигнал с управляющего входа запоминающей ячейки 11. Поэтому в элементы 52 памяти, находящиеся в (i+1)-M столбце третьего узла 49 памяти, записывается 1 информации о соответствующем признаке 1-го класса. После поступления (М+ +1)-го импульса с выхода первого элемента И 17 на счетный вход счетчика 18 на выходе последнего появляется единичньй импульс, поступающий через первый элемент ИЛИ 19 на входы сброса счетчика 18, третьего триггера 20 и четвертого триггера 24 и триггеров 25 второй группы, на прямых выходах которых устанавливаются нулевые сигналы, а на выходах ключей 26 пятой группы устанавливаются высокие сопротивления. При этом на выходах логиg ческих матриц 32 вычислительных ячеек 8 устанавливаются нулевые сигналы, на выходах ключей 36 второй группы, ключей 43 третьей группы и ключей 48 четвертой группы устанавливаются высокие сопротивления, а на управляющих входах ключей 14 первой группы устанавливаются единичные сигналы, и таким образом устройство автоматически переключается работать из режима Обучение в режим Распознавание, а узлы 49 памяти переключаются в режим считывания информации, так как на управляющем входе узлов 49 имеется нулевой сигнал. Длительность про-

0

5

.1

цесса Обучение равна произведению числа М (количество разрядов в двоичном коде образа) на период следования импульсов Т на выходе генератора 16 блока 6 управления. Период следования импульсов Т должен быть не меньше суммы времен задержки передач импульса третьим триггером 20, первым элементом И 17, элементом 23 за- держки, четвертым триггером 24, ключом 26 пятой группы, логической матрицей 28 первой группы, элементом ИЛИ 29 группы, логической матрицей 32 второй группы, первым сумматором 34, ключом 36 второй группы, элементом 38 задержки группы, ключом 43 третьей группы, логическим узлом 47 группы и вторым элементом И 53. Переключение работы устройства в режим Распознавание осуществляется автоматически после завершения процесса Обучение или учителем путем замыкания контактов второго коммутационного элемента 22 в блоке 6 управле- ния. При этом входная информация в виде М-разрядного двоичного кода подается на информационные входы устройства и поступает непосредственно на адресные входы первых узлов 49 памяти, первые входы элементов РАВНОЗНАЧНОСТЬ 44 и 45 первой и второй групп и первые входы четвертых элементов И 57 запоминающих ячеек 11,

Например, если на i-й информационный вход поступает единичный сигнал, то происходит считывание информации с элементов 52 памяти, находящихся в i-x строках первых узлов 49 памяти запоминающих ячеек 11. При этом в каждом элементе 52 памяти второй элемент И 53 закрыт, так как на его третий вход поступает нулевой сигнал с управляющего йхода узла 49 памяти, а третий элемент И 54 открыт. Если в шестом триггере 55 записана 1 и на первый вход третьего элемента И 54 поступает единичный сигнал с адресного входа, тогда на выходе третьего элемента И 54 имеется единичный сигнал, который открывает соответствующий ключ 56, и на его выходе также устанавливается единичный сигнал. Если на выходе третьего элемент И 54 имеется нулевой сигнал, то соответствующий ключ 56 закрыт и на его выходе устанавливается высокое сопротивление .

F, 0 Ь о

г

П

0

5

4 2

Единичньп сигнал с i-ro информационного входа поступает также на первые входы i-x элементов РАВНОЗНАЧ-, НОСТЬ 44, 45 первой и второй групп, на выходе которых устанавливается нулевой сигнал, так как на их вторые входы подается нулевой сигнал с управляющего входа. На выходе вторых элементов ИЛИ 59 i-x логических узлов 47 имеются единичные сигналы, поступающие на i-e адресные входы третьих узюв 49 памяти запоминающих ячеек 11, так как на первые входы четвертых элементов И 57 поступает единич- ньй сигнал с i-ro информационного входа, а на вторые входы поступает нулевой сигнал с управляющего входа. Поэтому в третьих узлах 49 памяти запоминающих ячеек 11 также происходит считывание информации с элементов 52 памяти, находящихся в i-й строке.

Например, если на i-й информаци- онньй вход поступает нулевой сигнал, то происходит считывание информации с элементов 52 памяти, находящихся в i-x строках вторых и четвертых узлов памяти запоминающих ячеек,, так как на выходах i-x элементов НЕРАВНО-- ЗНАЧНОСТЬ первой и второй групп будут единичные сигналы. С выходов узлов памяти единичные сигналы поступают на соответствующие входы соответствующих третьих сумматоров 46, на выходах которых формируются положительные потенциалы, а их величина пропорциональна количеству единичных сигналов на входах соответствующих сумматоров. Эти потенциалы поступают на соответствующие первые входы пороговых элементов 13 первой группы. Каждый из пороговых элементов первой группы представляет собой операционный усилитель, инверсньш вход которого является вторым входом элемента, а неинвертирующий вход - первым входом порогового элемента. Если, например, на втором входе 1-го порогового элемента первой группы величина положительного потенциала больше, чем на вторых входах других К-1 пороговых элементов, то на выходе 1-го порогового элемента будет положительный потенциал и диод 15 первой группы открыт, поэтому положительный потенциал с выхода порогового элемента подается на вторые входы пороговых элементов первой группы. При этом на выходах остальных К-1 пороговых элемен 1

тов будут присутствовать отрицательные потенциалы, так как величины положительных потенциалов, поступающих на их первые входы, меньи е, чем величина положительного по1 енциала на втором входе, поэтому все К-1 диодов первой группы будут закрыты. На выходе 1-го ключа 14 первой группы будет присутствовать единичный сиг- нал, а на выходах остальных К-1 ключей первой группы будут нулевые сигналы. Наличие единичного сигнала только на выходе 1-го ключа означает что предъявленный на информационных входах образ относится к 1-му классу

Формула изобретения

1. Устройство ассоциативного распознавания образов, содержащее матрицу вычислительных ячеек, блок выделения признаков, блок отнесения признаков, блок памяти, блок вьщеления образов, блок управления и регистр, причем каждая вычислительная ячейка матрицы содержит первый триггер, блок выделения признаков содержит М ячеек выделения признаков, каждая из которых содержит три узла выделения признаков, каждый из которых содержи первьш сумматор, блок отнесения признаков содержит М ячеек отнесения признаков, каждая из которых содержи три узла отнесения признаков, каждый из которых содержит второй сумматор, первый порог овый элемент, формирователь импульсов, второй триггер и группу элементов задержки, блок памяти содержит К запоминающих ячеек, каждая из которых содержит четыре узла памяти, третий сумматор и две группы элементов РАВНОЗНАЧНОСТЬ, блок вьщеления образов содержит первую группу пороговых элементов, блок управления -содержит генератор импульсов, счетчик, третий триггер, первьв элемент И и первый элемент ИЛИ, причем выход i-ro разряда регистра (i 1,...,М) является i-M информационным входом устройства, в каждом узле отнесения признаков i-й ячейки отнесения признаков выход второго сумматора соединен с информационным входом порогового элемента, управляющий вход которого является входом установки порога устройства, выход порогового элемента через формирователь импульсов соединен с информационным входом

4

14

второго триггера, входы элемента задержки группы соединены с соответствующими входч|,ми второго сумматора, в 1-й запоминающей ячейке (,.,К) блока памяти адресные входы первого узла памяти соединены с выходами разрядов регистра, адресные входы второго узла памяти соединены с выходами элементов РАВНОЗНАЧНОСТЬ первой грУп- пы, адресные входы четвертого узла

памяти соединены с выходами элементов РАВНОЗНАЧНОСТЬ второй группы, первые входы i-x элементов РАВНОЗНАЧНОСТЬ первой и BTopofi групп соединены с выходами i-ro Г азряда регистра, выходы соответствующего узла памяти 1-|й запоминающей ячейки блока памяти сре- динены с входами третьего сумматора, выход которого соединен с первым входом 1-го порогового элемента группы блока выделения образов, в блоке управления выход генератора импульсов соединен с первым входом первого элемента И, выход счетчика соединен с первым входом первого элемента ИЛИ, выход третьего триггера соединен с вторым входом третьего элемента И и с вторыми входами элементов РАВНОЗНАЧНОСТЬ первых и вторых групп и с управляющими входами узлов памяти запоминающих ячеек блока памяти, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, блок управления дополнительно содержит первый и второй коммутационные элементы, блок выделения образов дополнительно содержит инвертор, первую группу диодов и первую группу ключей, каждая вычислительная ячейка дополнительно содержит первую группу М-1 триггеров, первую и вторую группы логических матриц, группу элементов ИЛИ, первую и вторую

группы элементов НЕРАВНОЗНАЧНОСТЬ, каждый узел вьщеления признаков дополнительно содержит группу К-1 сумматоров, вторую группу диодов и вторую группу ключей, каждый узел отнесения признаков дополнительно содержит третью группу ключей, каждая запоминающая ячейка дополнительно содержит группу логических узлов и четвертую группу ключей, причем в блоке управления выход генератора импульсов через замыкающие контакты первого и второго коммутационных элементов соединен соответственно с информационным входом третьего триггера

и вторым входом первого элемента ИЛИ, выход которого соединен с входом сброса триггера, прямой выход которого соединен с управляющими входами логических матриц первой группы вычислительных ячеек матрицы, с управляющими входами ключей второй группы узлов выделения признаков, с управля- входами ключей четвертой груп- пы и вторыми входами логических узлов запоминающих ячеек блока памяти, с входом инвертора блока выделения образов, вход сброса счетчика и вход установки нуля регистра соединены с выходом элемента ИЛИ блока управления, выход первого элемента И блока управления соединен со счетным входом счетчика, с управляющим входом

регистра и входом сброса второго триг-20 тора и информационным входом 1-го

30

гера узлов отнесения признаков, в блоке выделения образов вторые входы пороговых элементов соединены с катодами диодов первой группы, выход 1-го порогового элемента соединен с анодом 1-го диода первой группы и информационным входом 1-го ключа первой группы, выход которого является 1-м выходом устройства, управляющие входы ключей первой группы соединены с выходом инвертора, в каждой вычислительной ячейке матрицы информационный вход i-ro триггера первой группы является i-M входом установки устройства, а вход Сброс триггеров первой г группы является входом Сброс устройства, прямой выход i-ro триггера первой группы соединен с вторым входом i-ro элемента НЕРАВНОЗНАЧНОСТЬ первой группы и с i-м входом второй группы входов первой логической матрицы первой группы матриц, 1-й выход которой соединен с i-м входом первого элемента ИЛИ группы и с первым входом

ключа второй группы, j-й информационный вход (,.,N) 1-го сумматора группы каждого узла вьщеления признаков является i-M выходом соответству- 25 ющей логической матрицы второй группы матриц вычислительной ячейки, находящейся в 1-й строке и J-M столбце матрицы вычислительных ячеек, в каждом узле отнесения признаков инверсный выход третьего триггера соединен с информационным входом ключей третьей группы, управляющие входы которых соединены с выходами соответствующих элементов задержки группы, входы второго cyNfMaTopa каждого узла отнесения признаков соединены с выходами ключей второй группы соответствующих узлов выделения признаков, входы сброса узлов памяти являются входом Сброс устройства, адресные входы третьего узла памяти соединены с выходами логических узлов группы, первый вход i-ro логического узла группы и информационный вход i-ro ключа четвертой

40

i-ro элемента НЕРАВНОЗНАЧНОСТЬ первой 45 группы соединены с выходом i-ro разгруппы, выход которого соединен с i-M входом первой и третьей логических матриц второй группы матриц, инверсный выход i-ro триггера соединен с вторым входом i-ro элемента НЕРАВНОЗНАЧНОСТЬ второй группы и с i-M входом второй группы входов второй логической матрицы второй группы матриц, i-й выход которой соединен с i-M входом второго элемента ИЛИ группы и с первым входом i-ro элемента НЕРАВНОЗНАЧНОСТЬ второй группы, выход которого соединен с i-M входом второй логической матрицы второй

16

группы матриц, выход первого элемента ИЛИ группы соединен с управляющим входом первой логической матрицы второй группы матриц, выход второго элемента ИЛИ группы подключен к управ- ляюпщм входам второй и третьей логических матриц второй группы матриц, i-й информационный вход каждой вычислительной ячейки является i-м информационным входом устройства, i-й информационный вход первой группы входов первой и второй логических матриц первой группы матриц является информационным входом устройства, в каждом узле выделения признаков вторые входы сумматоров группы соединены с катодами диодов второй группы, анод 1-го диода соединен с выходом 1-го сумма0

г

ключа второй группы, j-й информационный вход (,.,N) 1-го сумматора группы каждого узла вьщеления признаков является i-M выходом соответству- 5 ющей логической матрицы второй группы матриц вычислительной ячейки, находящейся в 1-й строке и J-M столбце матрицы вычислительных ячеек, в каждом узле отнесения признаков инверсный выход третьего триггера соединен с информационным входом ключей третьей группы, управляющие входы которых соединены с выходами соответствующих элементов задержки группы, входы второго cyNfMaTopa каждого узла отнесения признаков соединены с выходами ключей второй группы соответствующих узлов выделения признаков, входы сброса узлов памяти являются входом Сброс устройства, адресные входы третьего узла памяти соединены с выходами логических узлов группы, первый вход i-ro логического узла группы и информационный вход i-ro ключа четвертой

0

0

5

ряда регистра, выходы ключей четвертой группы и выходы третьего узла памяти соединены с входами третьего сумматора, выходы 1-х управляемых ключей третьей группы первого и второго узлов отнесения признаков соединены с выходами соответственно первого и второго узлов памяти, выходы 1-х управляемых ключей третьего узла отнесения признаков и четвертого узла памяти соединены с третьими входами логических узлов 1 - и запоминающей ячейки блока памяти.

17

2.Устройство по П.1, отличающееся тем, что регистр содержит элемент задержки, четвертый триггер, вторую группу триггеров и пятую группу ключей, выходы которых являются выходами разрядов регистра, управляющие входы ключей пятой группы соединены с прямым выходом четвертого триггера, инверсный выход которого соединен с информационным входо первого триггера второй группы, тактовые входы триггеров второй группы

и вход элемента задержки являются управляющим входом регистра, входы сброса четвертого триггера и триггеров второй группы являются входом Сброс регистра, выход элемента задержки соединен с информационным входом четвертого триггера, прямой выход i-ro триггера второй группы соединен с информационным входом i-ro ключа пятой группы и информационньм входом (i-t-l)-ro триггера второй группы,

3.Устройство по чающееся

п. 1, о т л и - тем, что каждая логическая матрица первой группы матри содержит матрицу диодов из 2-М строк и М столбцов и группу из М нагрузочных резисторов, причем один из выводов i-ro резистора является управляющим входом матрицы, а другой вывод соединен сi-м столбцом матрицы, (2х x(i-1)-H строка матрицы соединена с i-M входом первой группы входов матрицы, а (2xi)-H строка матрицы соединена с i-M входом второй группы входов матрицы, i-й столбец матрицы является i-M выходом матрицы, (2х x(i-1)-я и (2xi)-H строки через соответствующие диоды соединены с i-м столбцом матрицы, причем аноды диодо соединены со столбцами, а катоды диодов - со строками матрицы,

4, Устройство по п.1, о т л и - чающееся тем, что каждая логическая матрица второй группы матриц содержит матрицу диодов из М строк и М столбцов и группу из М нагрузочных резисторов, причем один из вьшодов i-ro резистора является вхо1

30644

дом матрицы, а другой вывод соединен с i-M столбцом матрицы, i-я строка является i-M входом матрицы и через

соответствующий диод соединена с i-м

)

столбцом матрицы, который является i-M выходом матрицы, причем аноды диодов соединены со столбцами, а катоды диодов - со строками матрицы,

10 5, Устройство по п,1, о тли- чающееся тем, что узел памяти содержит матрицу элементов памяти из М строк и М столбцов, а каждый элемент памяти содержит второй и тре15 тий элементы И, шестой триггер и

транзисторный ключ, в каждом элементе памяти выход второго элемента И соединен с информационным входом шестого триггера, вход сброса которого явля20 ется входом сброса узла памяти, прямой выход шестого триггера соединен с вторым входом третьего элемента И, выход которого через транзисторньй ключ соединен с вторым входом второго

Ь элемента И, третий вход которого и третий инверсный вход третьего элемента И являются входом узла памяти, первые входы второго и третьего элементов И являются информационным

30 входом элемента памяти, выход транзисторного ключа является выходом элемента памяти, причем информационные входы Элементов памяти i-й строки узла являются i-м адресным входом узла, выходы элементов памяти i-ro столбца узла являются i-м выходом узла,

35

6, Устройство по п,1, о т л и - чающееся тем, что логический узел содержит четвертый и пятый элементы И и второй элемент ИЛИ, выход которого является выходом узла, первый вход четвертого элемента И соединяется первым входом узда, второй инверсный вход четвертого элемента И и первый вход пятого элемента И являются вторым входом узла, второй вход пятого элемента И является третьим входом узла, выходы четвертого и пятого элементов И соединены с входами второго элемента ИЛИ.

Сброс

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативная однородная обучаемая среда для распознавания объектов | 1983 |

|

SU1149287A1 |

| Устройство цифровой информации | 1991 |

|

SU1815653A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| Устройство распределения оперативной памяти | 1988 |

|

SU1509909A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Устройство для параллельного формирования адресов | 1990 |

|

SU1734097A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Вычислительное устройство | 1989 |

|

SU1697077A2 |

| Устройство для решения оптимизационных задач стандартизации | 1988 |

|

SU1594568A1 |

Изобретение относится к технической кибернетике и предназначено для построения устройства распознавания. Цель изобретения - повышение быстродействия и упрощение устройства. Это достигается введением двух групп логических матриц, двух групп диодов, четьфех групп ключей, группы триггеров, группы сумматоров, группы логических узлов, элемента задержки, группы элементов ИЛИ, двух групп элементов НЕРАВНОЗНАЧНОСТЬ, инвертора и двух коммутационных элементов, что позволяет распараллелить процесс выделения признаков и формировать классы распознаваемых образов в виде двумерной матрицы блока памяти для последующего ассоциативного распознавания объектов. 5 з.п. ф-лы, 13 ил. с ф W оа со о Од 4ib

фцг.2.

сриг.З

фиг А

фиг. 5

Ннф- 8ходУпр. 6л.

Я

J9

38

itO ill

J

ЧЗЕ

«7

CSpoc

Unp-SA

Г

упр.вк.

dx.

Bx.M.

1

iq

(ftifs. fO

Й

5/

a

,j

if фиг. ft

Редактор М.Келемеш

Заказ 3584/51Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Q:JU2J2

л

ери г. 13

Составитель А.Глотов

Техред Л.Сердюкова Корректор С.Шекмар

| Асооциативная однородная среда | 1978 |

|

SU798803A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ассоциативная однородная обучаемая среда для распознавания объектов | 1983 |

|

SU1149287A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-15—Публикация

1985-08-25—Подача