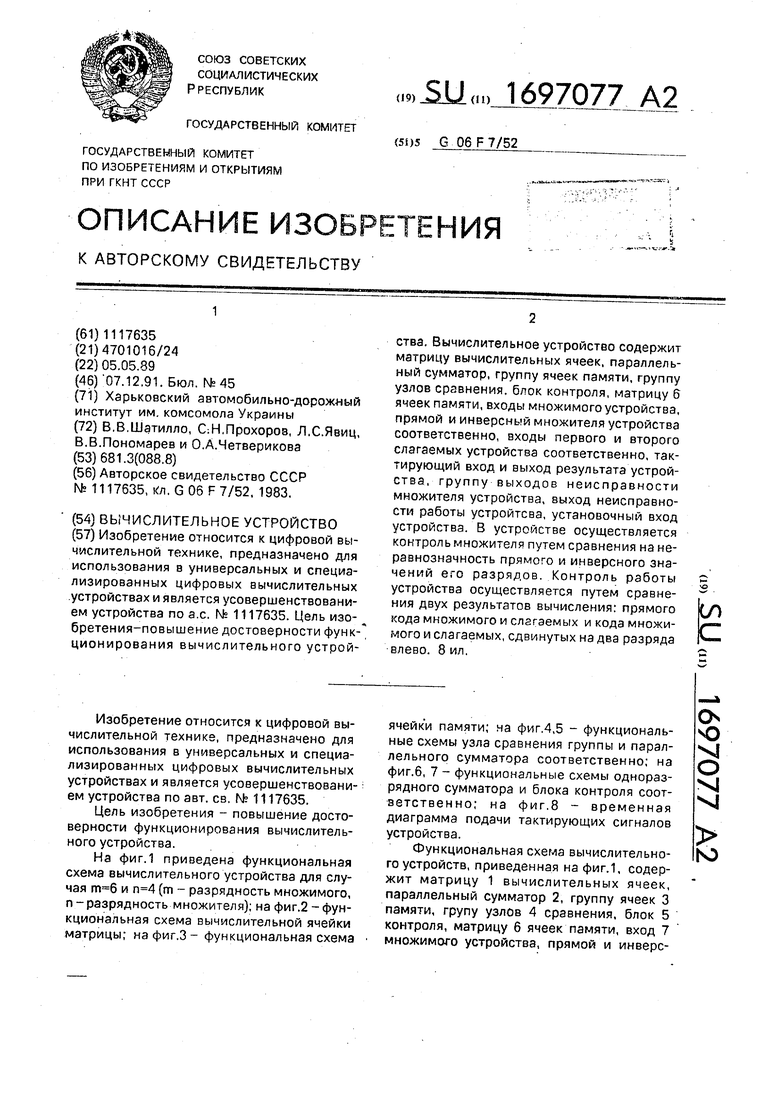

Изобретение относится к цифровой вычислительной технике, предназначено для использования в универсальных и специализированных цифровых вычислительных устройствах и является усовершенствованием устройства по авт. св. N; 1117635.

Цель изобретения - повышение достоверности функционирования вычислительного устройства.

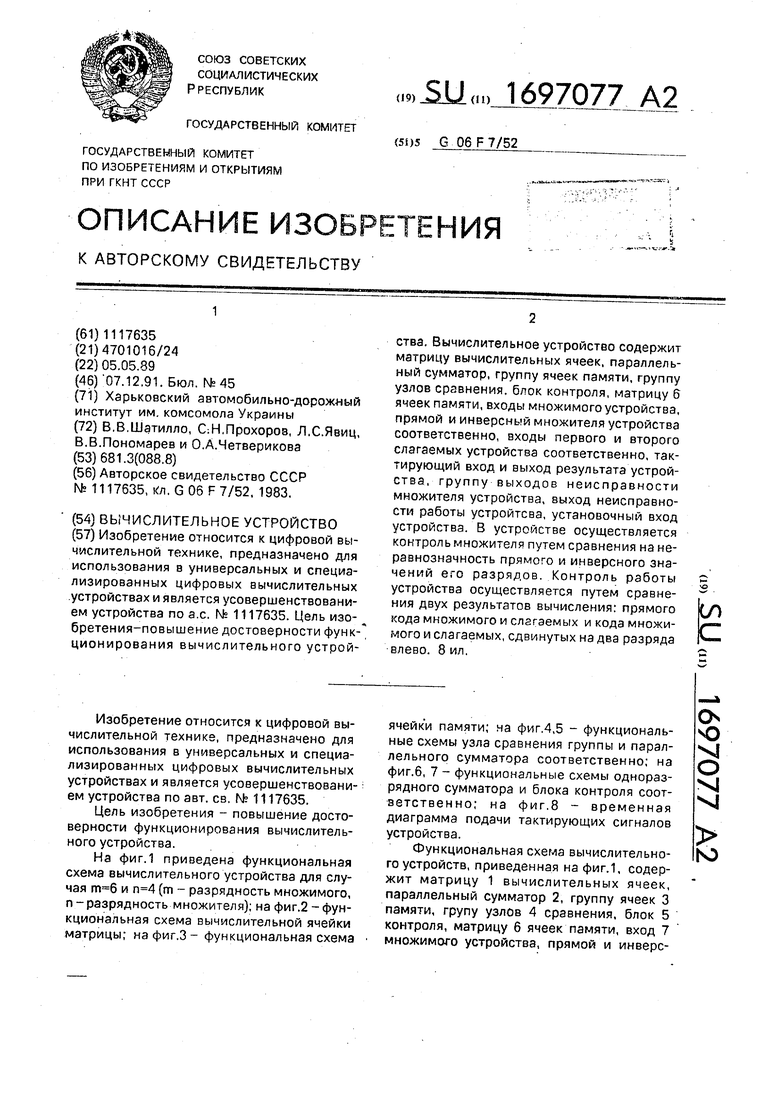

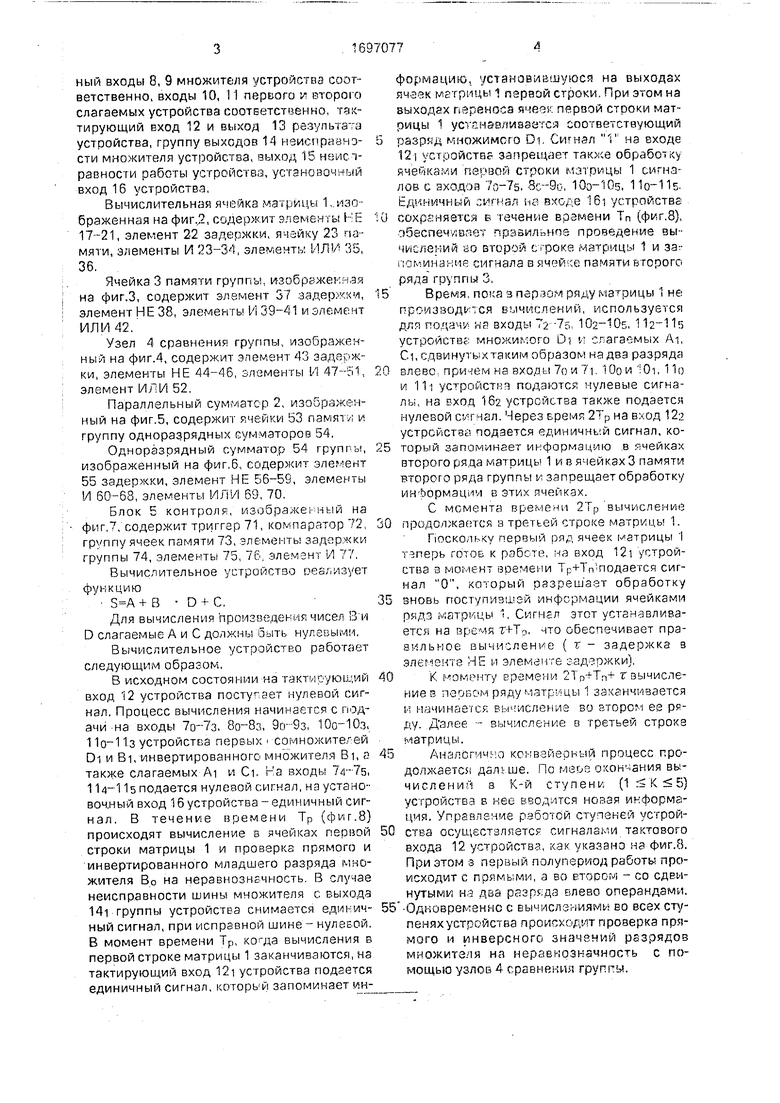

На фиг.1 приведена функциональная схема вычислительного устройства для случая и (т - разрядность множимого, п - разрядность множителя); на фиг.2 - функциональная схема вычислительной ячейки матрицы; на фиг,3- функциональная схема

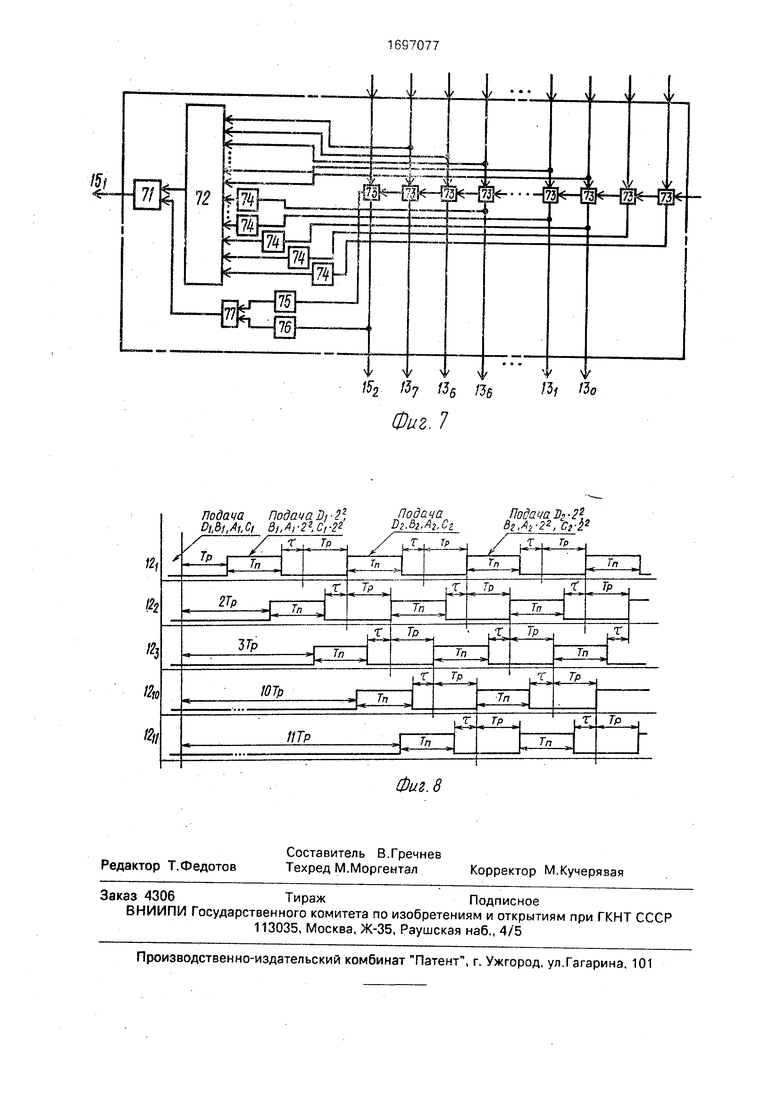

ячейки памяти; на фиг.4,5 - функциональные схемы узла сравнения группы и параллельного сумматора соответственно; на фиг.6, 7 - функциональные схемы одноразрядного сумматора и блока контроля соответственно; на фиг.8 - временная диаграмма подачи тактирующих сигналов устройства.

Функциональная схема вычислительного устройств, приведенная на фиг.1, содержит матрицу 1 вычислительных ячеек, параллельный сумматор 2, группу ячеек 3 памяти, трупу узлов 4 сравнения, блок 5 контроля, матрицу б ячеек памяти, вход 7 множимого устройства, прямой и инверсо ю

XI О VI vj

ю

ный входы 8, 9 множителя устройства соответственно, входы 10, 11 первого и второго слагаемых устройства соответственно, тактирующий вход 12 и выход 13 результата устройства, группу выходов 14 неисправности множителя устройства, выход 15 неисправности работы устройства, установочный вход 16 устройства.

Вычислительная ячейка матрицы 1, изображенная на фиг.;2, содержит элементы НЕ 17-21, элемент 2-2 задержки, ячейку 23 памяти, элементы И 23-3-1, элементы ИЛИ 35, 36.

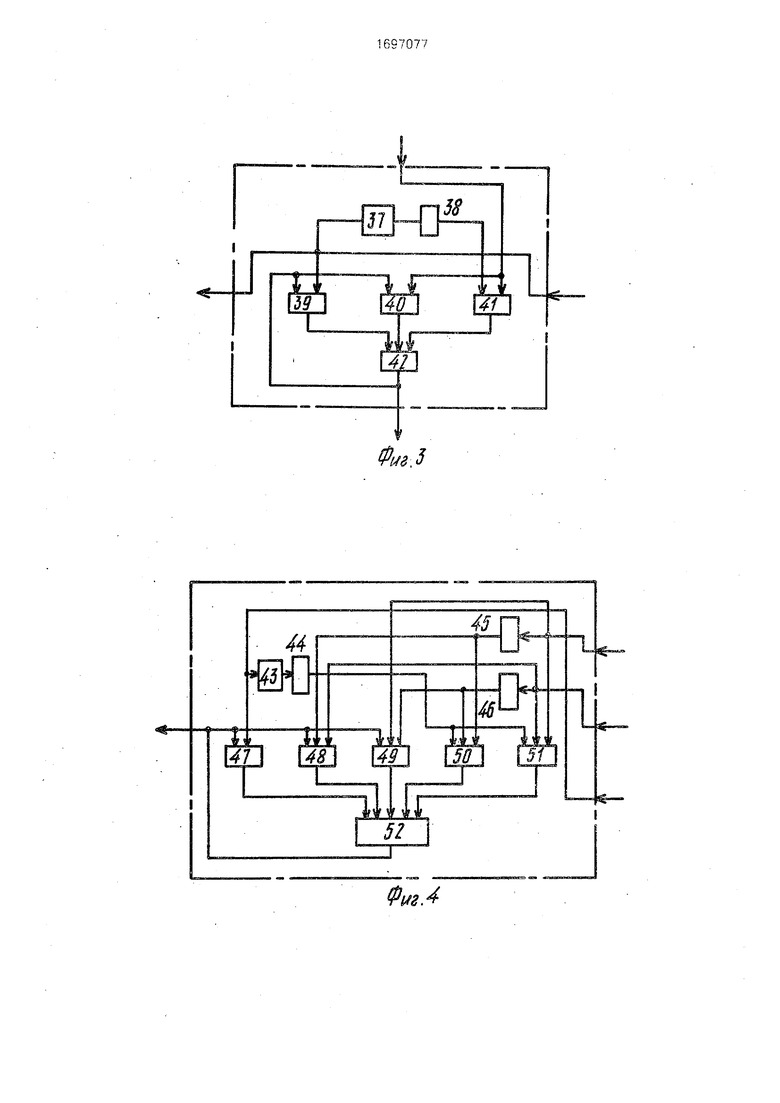

Ячейка 3 памяти группы, изображенная на фиг.З, содержит элемент 37 задержки, элемент НЕ 38, элементы И 39-41 и элемент ИЛИ 42.

Узел 4 сравнения группы, изображенный на фиг.4, содержит элемент 43 задеож- ки, элементы НЕ 44-46, элементы И 47-51, элемент ИЛИ 52.

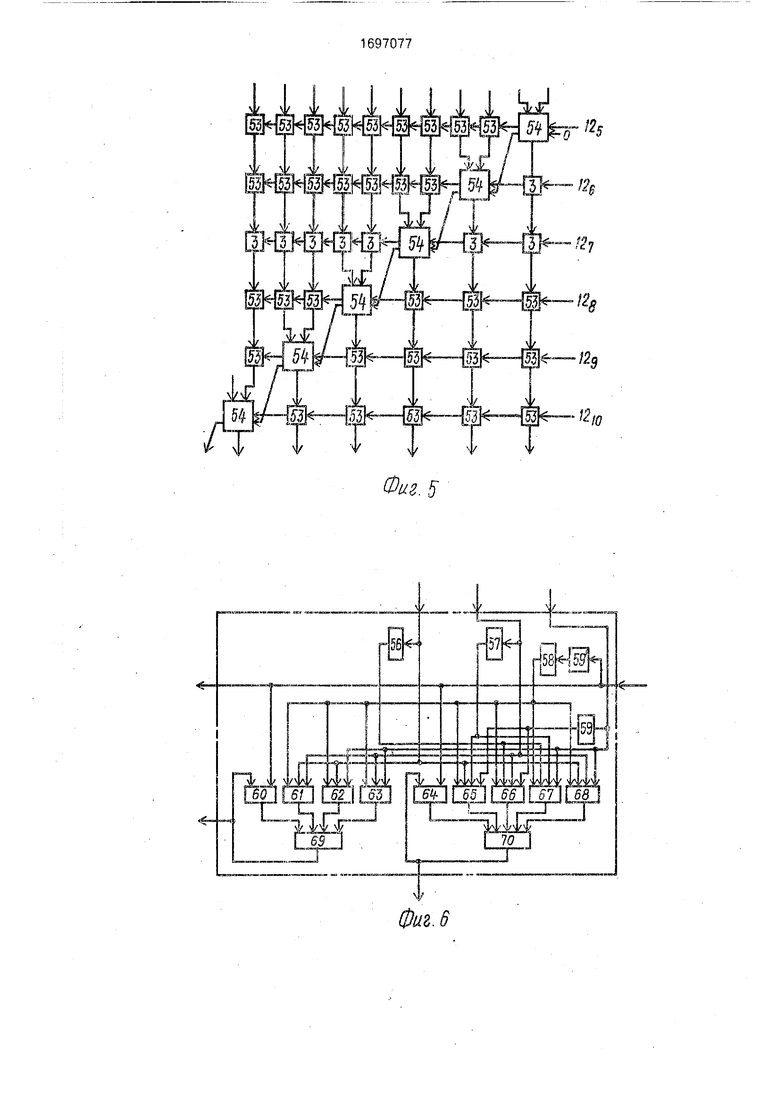

Параллельный сумматор 2, изображенный на фиг.5, содержит ячейки 53 памяти и группу одноразрядных сумматоров 54.

Одноразрядный сумматор 54 группы, изображенный на фиг.6, содержит элемент 55 задержки, элемент НЕ 56-59, элементы И 60-68, элементы ИЛИ 69, 70,

Блок 5 контроля, изображенный на фиг.7, содержит триггер 71, компаратор 72, группу ячеек памяти 73, элементы задержки группы 74, элементы 75, 76, элемент И 77,

Вычислительное устройство реализует функцию

+ В D + С,

Для вычисления произведения чисел В и D слагаемые А и С должны быть нулевыми,

Вычислительное устройство работает следующим образом.

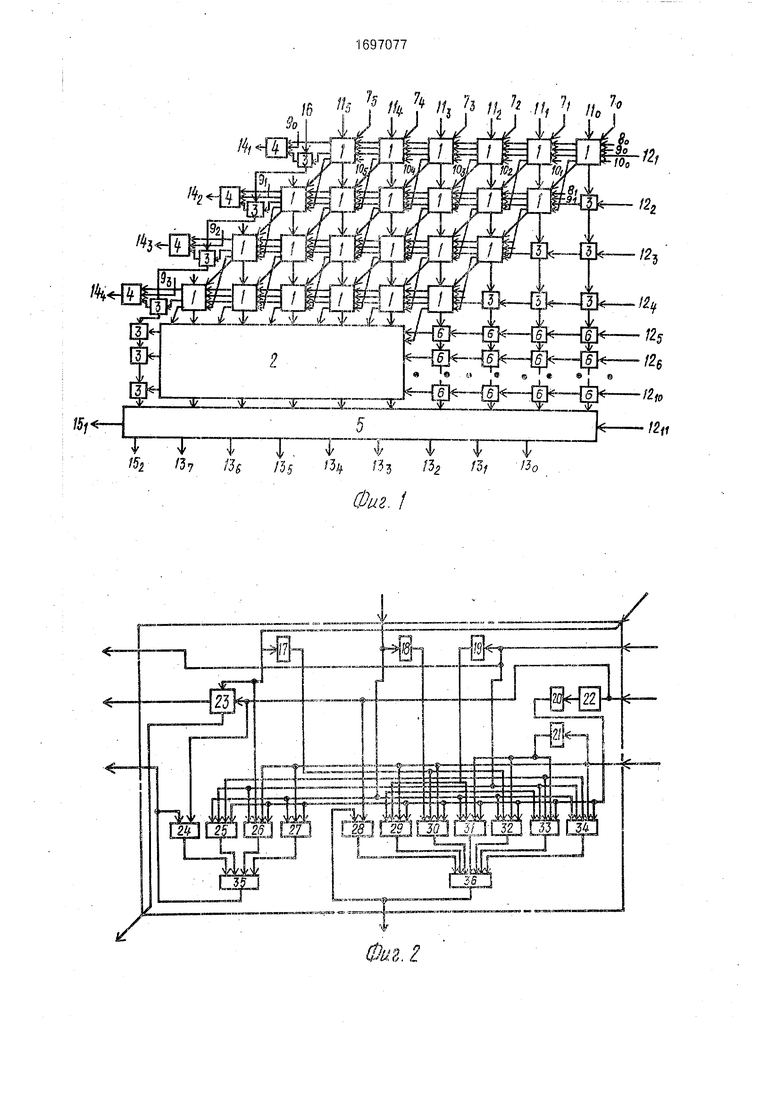

В исходном состоянии на тактирующий вход 12 устройства поступает нулевой сигнал. Процесс вычисления начинается с подачи на входы 7о-7з. , , 10о-10з, устройства первых сомножителей DI и Bi, инвертированного множителя Bi, a также слагаемых AI и CL На входы , 1 U-115 подается нулевой сигнал, на установочный вход 16устройства -единичный сигнал. В течение времени Тр (фиг.8) происходят вычисление в ячейках первой строки матрицы 1 и проверка прямого и инвертированного младшего разряда множителя Во на неравнозначность. В случае неисправности шины множителя с выхода 14i группы устройства снимается единичный сигнал, при исправной шине - нулевой. В момент времени Тр, когда вычисления в первой строке матрицы 1 заканчиваются, на тактирующий вход 12i устройства подается единичный сигнал, который запоминает информацию,, установившуюся на выходах ячеек матрицы 1 первой строки, При этом на выходах переноса ячеек первой стооки матрицы 1 устанавливается соответствующий

разряд множимого DL Сигнал 11 на входе 12 устройства запрещает также обработку ячейками первой строки матрицы 1 сигналов с входов 7o-7s, 8c-9o, 10o-10s, 11o-11s. Единичный сигнал на входе 16i устройства

сохраняется Б течение времени Тп (фиг.8), обеспечивает правильное проведение вычислений зо второй строке матрицы 1 и за- поминание сигнала в ячей;се памяти второго ряда группы 3.

Время, пока а первом ряду матрицы 1 не производится вычислений, используется для подачи на входы 2 -7g 102-105, 112-11s устройства множимого DI и слагаемых AI, Ст.сдвинутыхтаким образом на два разряда

влево, причем на входы 7о и 7j, Юо и f От, 11о и 11i устройства подаются нулевые сигналы, на вход 162 устройства также подается нулевой сигнал. Через время 2ТР на вход 122 устройства подается единичный сигнал, который запоминает информацию в ячейках второго ряда матрицы 1 и в ячейках 3 памяти второго ряда группы и запрещает обработку информации в этих ячейках.

С момента времени 2ТР вычисление

продолжается в третьей строке матрицы , Поскольку первый ряд ячеек матрицы 1 теперь готов к работе, на вход 12i устройства в момент времени Тр+Тп подается сигнал О, который разрешает обработку

вновь поступившей информации ячейками ряда матрицы 1. Сигнал этот устанавливается на время г+Тр, что обеспечивает правильное вычисление ( т - задержка в элементе НЕ и элементе задеожки),

К моменту времени 2ТР+Т.Т4- г вычисление в первом ряду матрицы 1 заканчивается и начинается вычисление во втором ее ряду. Далее - вычисление в третьей строке матрицы.

Аналогично конвейерный процесс продолжается дальше. По меое окончания вычислений в К-й ступени (1 К 5) устройства в нее вводится новая информация. Управление работой ступеней устройства осуществляется сигналами тактового входа 12 устройства, как указано на фиг.8. При этом в первый полупериод работы происходит с прямыми, а во втором - со сдвинутыми на два разряда влево операндами.

-Одновременно с вычислениями во всех ступенях устройства происходит проверка прямого и инверсного значений разрядов множителя на неравнозначность с помощью узлов 4 сравнения группы.

В блоке 5 контроля результат вычисления с прямыми операндами сравнивается с результатом вычисления со сдвинутыми операндами. При несравнении формируется единичный сигнал на выходе 15 неисп- равности работы устройства.

Результат вычислений поступает на выход 13 результата устройства.

Формула изобретения

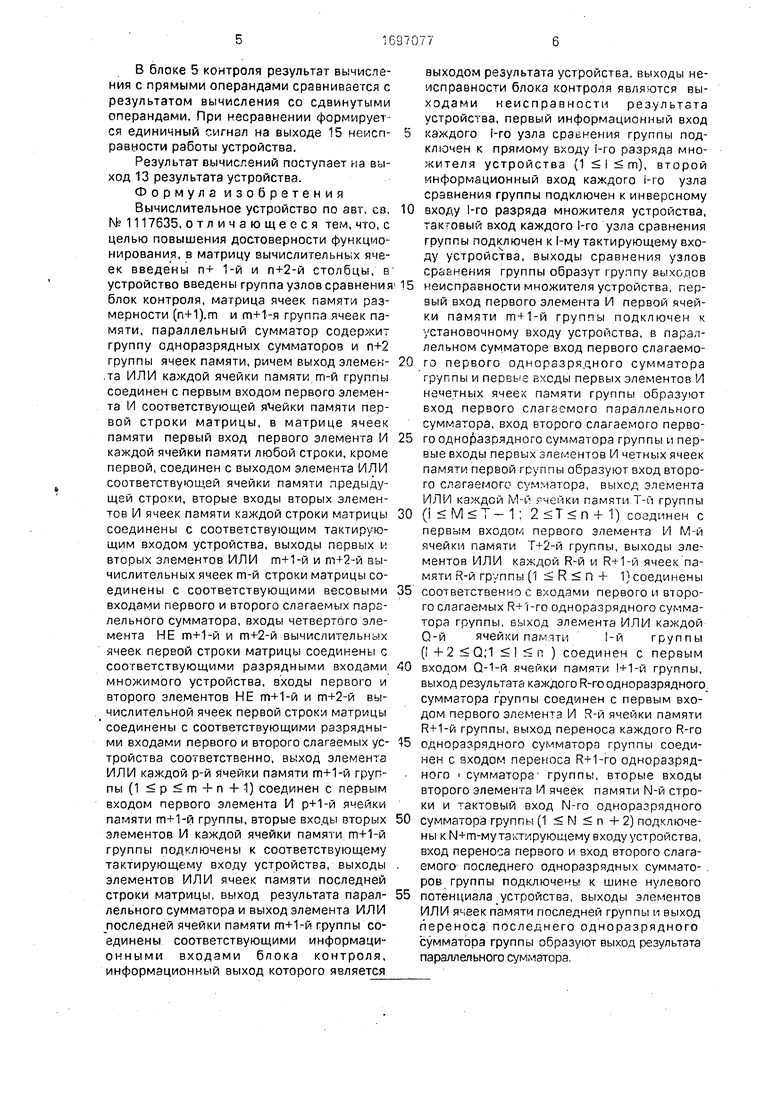

Вычислительное устройство по авт. св. № 1117635, отличающееся тем, что, с целью повышения достоверности функционирования, в матрицу вычислительных ячеек введены п+ 1-й и n+2-й столбцы, в устройство введены группа узлов сравнения блок контроля, матрица ячеек памяти размерности (n+1).m и m+1-я группа ячеек памяти, параллельный сумматор содержит группу одноразрядных сумматоров и п+2 группы ячеек памяти, ричем выход элемен- .та ИЛИ каждой ячейки памяти rri-й группы соединен с первым входом первого элемента И соответствующей ячейки памяти первой строки матрицы, в матрице ячеек памяти первый вход первого элемента И каждой ячейки памяти любой строки, кроме первой, соединен с выходом элемента ИЛИ соответствующей ячейки памяти предыдущей строки, вторые входы вторых элементов И ячеек памяти каждой строки матрицы соединены с соответствующим тактирующим входом устройства, выходы первых и вторых элементов ИЛИ m+1-й и m+2-й вычислительных ячеек m-й строки матрицы соединены с соответствующими весовыми входами первого и второго слагаемых парз- лельного сумматора, входы четвертого элемента НЕ m+1-й и m+2-й вычислительных ячеек первой строки матрицы соединены с соответствующими разрядными входами множимого устройства, входы первого и второго элементов НЕ m+1-й и m+2-й вычислительной ячеек первой строки матрицы соединены с соответствующими разрядными входами первого и второго слагаемых ус- тройства соответственно, выход элемента ИЛИ каждой р-й ячейки памяти m+1-й группы (1 р m + n + 1) соединен с первым входом первого элемента И р+1-й ячейки памяти m+1-й группы, вторые входы вторых элементов И каждой ячейки памяти m+1-й группы подключены к соответствующему тактирующему входу устройства, выходы элементов ИЛИ ячеек памяти последней строки матрицы, выход результата парал- лельного сумматора и выход элемента ИЛИ последней ячейки памяти m+1-й группы соединены соответствующими информационными входами блока контроля, информационный выход которого является

выходом результата устройства, выходы неисправности блока контроля являются выходами неисправности результата устройства, первый информационный вход каждого i-го узла сравнения группы подключен к прямому входу 1-го разряда множителя устройства (1 ), второй информационный вход каждого i-ro узла сравнения группы подключен к инверсному входу i-ro разряда множителя устройства, тактовый вход каждого 1-го узла сравнения группы подключен к 1-му тактирующему входу устройства, выходы сравнения узлов сравнения группы образут группу выходов неисправности множителя устройства, первый вход первого элемента И первой ячейки памяти m + 1-й группы подключен к установочному входу устройства, в параллельном сумматоре вход первого слагаемого первого одноразрядного сумматора группы и первые входы первых элементов И нечетных ячеек памяти группы образуют вход первого слагаемого параллельного сумматора, вход второго слагаемого первого одноразрядного сумматора группы и первые входы первых элементов И четных ячеек памяти первой группы образуют вход второго слагаемого сумматора, выход элемента ИЛИ каждой М-и ячейки памяти Т-й группы (I 1 ; ) соединен с первым входом первого элемента И М-й ячейки памяти Т+2-й группы, выходы элементов ИЛИ каждой R-й и R+1-й ячеек памяти R-й группы (1 R n + 1) соединены соответственно с входами первого и второго слагаемых R+1-го одноразрядного сумматора группы, выход элемента ИЛИ каждой Q-й ячейки памяти1-й группы

( + 2 Q;1 п ) соединен с первым входом Q-l-й ячейки памяти 1+1-й группы, выход результата каждого R-ro одноразрядного сумматора группы соединен с первым входом первого элемента И R-й ячейки памяти R+1-й группы, выход переноса каждого R-ro одноразрядного сумматора группы соединен с входом переноса R+1-го одноразрядного i сумматора- группы, вторые входы второго элемента И ячеек памяти N-й строки и тактовый вход N-го одноразрядного сумматора группы (1 N n 4- 2) подключены к M+m-му тактирую тему входу устройства, вход переноса первого и вход второго слагаемого последнего одноразрядных суммато- . ров группы подключены к шине нулевого потенциала устройства, выходы элементов ИЛИ ячеек памяти последней группы и выход переноса последнего одноразрядного сумматора группы образуют выход результата параллельного сумматора.

ft t j jjHf ft «.

/

1ТТ

& /37 %

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1697078A1 |

| Вычислительное устройство | 1987 |

|

SU1509872A1 |

| Вычислительное устройство | 1983 |

|

SU1117635A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Матричный умножитель | 1988 |

|

SU1615704A1 |

Изобретение относится к цифровой вычислительной технике, предназначено для использования в универсальных и специализированных цифровых вычислительных устройствах и является усовершенствованием устройства по а.с, № 1117635. Цель изо- бретения-повышение достоверности функционирования вычислительного устройства. Вычислительное устройство содержит матрицу вычислительных ячеек, параллельный сумматор, группу ячеек памяти, группу узлов сравнения, блок контроля, матрицу 6 ячеек памяти, входы множимого устройства, прямой и инверсный множителя устройства соответственно, входы первого и второго слагаемых устройства соответственно, тактирующий вход и выход результата устройства, группу выходов неисправности множителя устройства, выход неисправности работы устройтсва, установочный вход устройства. В устройстве осуществляется контроль множителя путем сравнения на неравнозначность прямого и инверсного значений его разрядов Контроль работы устройства осуществляется путем сравнения двух результатов вычисления: прямого кода множимого и слагаемых и кода множимого и слагаемых, сдвинутых на два разряда влево. 8 ил. сл С

. /

Фиг. 2

44

7

ПИ

58

О

Фиг 5

45

1

I

Фиг.4

u

Фиг 5

Фиг. 6

tf2 /37 % Яв/3 /Зв

Фиг. 7

| Вычислительное устройство | 1983 |

|

SU1117635A1 |

Авторы

Даты

1991-12-07—Публикация

1989-05-05—Подача