b.i 1 K2J---RF

7Г Г-.ГТГ

сравнения, 2N блоков 4 элементов И, блок 5 формирования признака окончания адресации, введены N узлов 6 сдвига адреса. Это позволяет в соответствии со значением кода сдвига адреса производить параллельно запись - считывание необходимых элементов вектора из блоков оперативной памяти ЭВМ. 9 ил., 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельного формирования адресов | 1988 |

|

SU1575181A2 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для параллельного формирования адресов | 1985 |

|

SU1337898A1 |

| Устройство для параллельного формирования адресов | 1987 |

|

SU1418711A1 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство цифровой двумерной свертки | 1988 |

|

SU1647585A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1168940A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

Изобретение относится к вычислительной технике и может быть использовано в параллельных вычислительных системах с общим управлением и с основной памятью, состоящей из нескольких независимо адресуемых блоков. Цель изобретения - повышение пропускной способности устройства. В устройство, содержащее блок 1 формирования адресов, N сумматоров 2, N блоков 3

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных ЭВМ с общей основной памятью, состоящей из нескольких независимо адресуемых блоков.

Известно устройство для формирования адреса, содержащее узел вычисления индексов, три регистра адреса, три регистра индексов. Это устройство позволяет вычислять адреса обращения к ОЗУ без обращения за значениями индекса к ОЗУ.

Недостатком этого устройства является низкое быстродействие вычисления адресов обращения к ОЗУ.

Известно также устройство формирования адреса, содержащее счетчик адреса, счетчик итерации, два коммутатора, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, ПЗУ, два элемента ИЛИ, формирователь импульсов и дополнительный счетчик. В этом устройстве в зависимости от номера итерации из ПЗУ выбираются значения требуемых адресов операндов.

Недостатком устройства является невозможность формирования необходимого количества адресов для обращения к ОЗУ, состоящего из нескольких независимо адресуемых блоков.

Наиболее близким к изобретению является устройство для параллельного формирования адресов, содержащее группу регистров адреса, группу регистров шага индекса, коммутатор адреса, коммутатор индекса, сумматоры, группу регистров номера блоков, коммутатор номера блоков, блок запоминания и сдвига индексов, группу схем сравнения, элемент ИЛИ, триггер, регистр максимального индекса, группу блоков элементов И, причем информационный вход К-го регистра адреса подключен к К-му входу начального адреса устройства (К 1Н, где Н - количество начальных адресов), выход К-ro регистра адреса подключен к К-му информационному входу коммутатора адреса, выход которого подключен к первому входу первого сумматора. Выход R-ro регистра шага индекса подключен к R-му информационному входу коммутатора индексов (R 1,..., О, где Q количество шагов изменения индексов). Вход максимально допустимого индекса устройства подключен к информационному входу регистра максимального индекса, выход которого подключен к первым входам схем сравнения группы, выходы которых подключены к входам элемента ИЛИ, выход которого подключен к входу установки в 1 триггера. Выход последнего подключен к

выходу признака окончания адресации устройства. Вход выбора адреса устройства соединен с входом выбора шага изменения индекса коммутатора индекса и подключен к входу выбора коммутатора номера блока,

выход которого подключен к входу сдвига блока запоминания и сдвига индексов, а i-й вход начального номера блока устройства подключен к i-му входу регистра номера блока (где i 1 ...К), выход коммутатора адреса подключен к первым входам сумматоров с второго по (М-1)-й вход разрешения считывания которого подключен к I-му входу выбора группы адресов устройства (где I 1...М, где М - количество тактов адресации

массива), n-й выход поля индекса блока запоминания и сдвига индексов и выход п-го сумматораподключенык n-м информационным входам соответственно первого и второго блоков групп элементов И (п 1 ...N, где

N - количество параллельно формируемых адресов), n-ные информационные выходы которых подключены к n-м выходам соответственно младших и старших разрядов адреса устройства, n-й выход схемы сравнения

группы подключен к n-му входу разрешения выдачи информации первого и второго блоков групп элементов И. n-й выход поля индекса и n-й выход поля приращения адреса блока запоминания и сдвига индексов подключены к второму входу n-й схемы сравнения группы, n-й выход поля приращения блока запоминания индекса подключен к второму входу n-го сумматора. Информационный вход R-ro регистра шага индекса

группы подключен к R-му входу шага изменения индекса группы устройства.

В этом устройстве основная адресуемая память вычислительной системы состоит из Р блоков, имеющих независимые адресные

цепи одинаковой разрядности. Полный адрес ячейки основной памяти образуется двумя составляющими: номером блока (младшие разряды полного адреса) и адресом ячейки в блоке (старшие разряды полного адреса). Предполагается хранение адресуемых данных в основной памяти в виде одномерного массива (вектора). Причем соседние элементы вектора имеют отличающиеся на единицу адреса. Начальный адрес ячейки в блоке и начальный номер блока поступают на входные регистры устройства. Кроме того, на входные регистры устройства подаются шаг, с которым необходимо осуществить обращение к элементам вектора, а также граница вектора. Устройство формирует параллельно несколько (N) адресов для обращения к элементам вектора, пока сформированный адрес не достигает максимальной границы вектора. Для параллельного формирования М адресов за N тактов (где M N Р - количество независимо адресуемых блоков памяти) на вход устройства подаются адрес ячейки, размер вектора, значение шага, с которым необходимо считывать элементы вектора, номер блока, в котором расположен первый элемент вектора, а на выходе устройства формируются полные значения адресов (младшие разряды - номер блока, старшие разряды - номер ячейки). Значениями М и N можно варьировать в больших пределах.

Данное устройство размещает соседние элементы вектора при их записи в подряд расположенные ячейки памяти. Однако возникает необходимость считывания элементов вектора или из подряд расположенных ячеек памяти (значение шага индекса при этом равно единице), или из ячеек памяти с шагом, отличным от единицы. Необходимость выборки элементов вектора с шагом, большим единицы, возникает, например, при выборке столбцов матрицы, диагональных элементов матрицы (матрицы в памяти хранятся в виде совокупности векторов - строк или векторов - столбцов). При этом при определенных значениях шага выбираемые элементы размещаются в одном блоке памяти. В результате этого происходит падение пропускной способности памяти из-за последовательного считывания элементов вектора из данного блока.

Недостатком данного устройства является отсутствие возможности размещать (выбирать) данные в соответствии с некоторой закономерностью, что приводит к падению пропускной способности памяти.

Цель изобретения - повышение пропускной способности памяти за счет рацио0 нального размещения элементов вектора по блокам оперативной памяти.

В устройстве сформированные адреса сдвинуты согласно значению кода на входе задания кода сдвига адресов устройства.

5 При этом пропускная способность памяти при обращении к диагональным элементам матриц и элементам столбцов матриц по сравнению с прототипом возрастает пропорционально числу блоков памяти. Таким образом, технико-экономическим преимуществом предлагаемого устройства по сравнению с прототипом является повышение пропускной способности памяти в Р раз, где Р - количество блоков памяти.

Поставленная цель достигается тем, что

в устройство для параллельного формирования адресов, содержащее блок формирования адресов, блок формирования признака окончания адресации, N блоков сравнения

0 (где N - количество параллельно формируемых адресов), N сумматоров, 2N блоков эле- ментов И, причем выход 1-го блока сравнения соединен с первыми входами i-ro и (i+1)-ro блоков элементов И и i-тым входом

5 блока формирования признака окончания

адресации (i 1 N), управляющий вход

блока формирования адресов является входом выбора группы адресов устройства, i- тый выход блока формирования адресов

0 соединен с первым входом i-ro сумматора, выход которого соединен с вторым входом i-ro блока элементов И, выход которого является выходом старших разрядов i-ro адреса устройства, выход (i + N)-ro блока

5 элементов И является выходом младших разрядов i-ro адреса устройства, введены N узл«в сдвига адреса, причем первый адресный вход i-ro узла сдвига адреса соединен с выходом i-ro сумматора и с первым входом

0 i-ro блока сравнения, второй адресный вход - с входом задания кода сдвига адресов устройства, информационный вход соединен с (i+N)-M выходом блока формирования адресов, адресный вход которого является

5 входом задания шага индекса устройства, информационный вход - входом задания начального номера блока устройства, управляющие входы узлов сдвига адреса объединены и являются входом разрешения сдвига

0 адреса устройства, выход i-ro узла сдвига адреса соединен с вторыми входами i-ro блока сравнения и (i+N)-ro блока элементов И, третьи входы блоков элементов И объединены и являются входом разрешения вы5 дачи группы адресов устройства, третьи входы блоков сравнения объединены и являются входом задания границы массива устройства, вторые входы сумматоров объединены и являются входом задания адреса

ячейки устройства, выход блока формирования признака окончания адресации является выходом признака окончания адресации устройства.

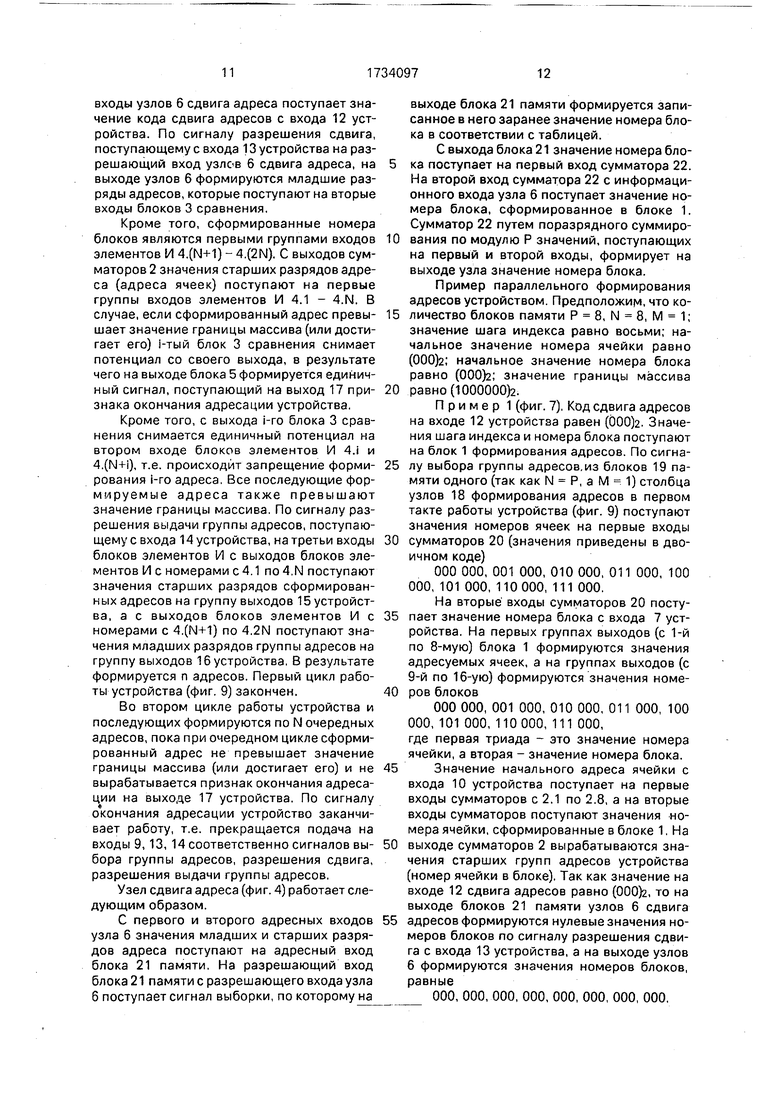

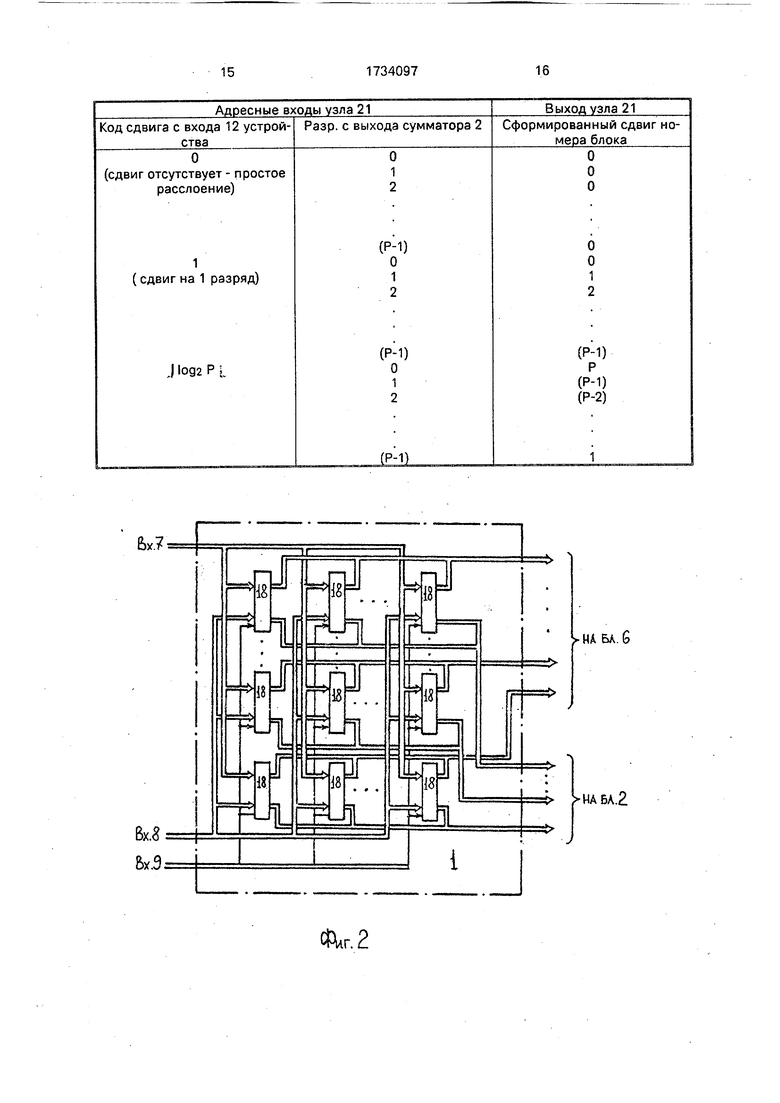

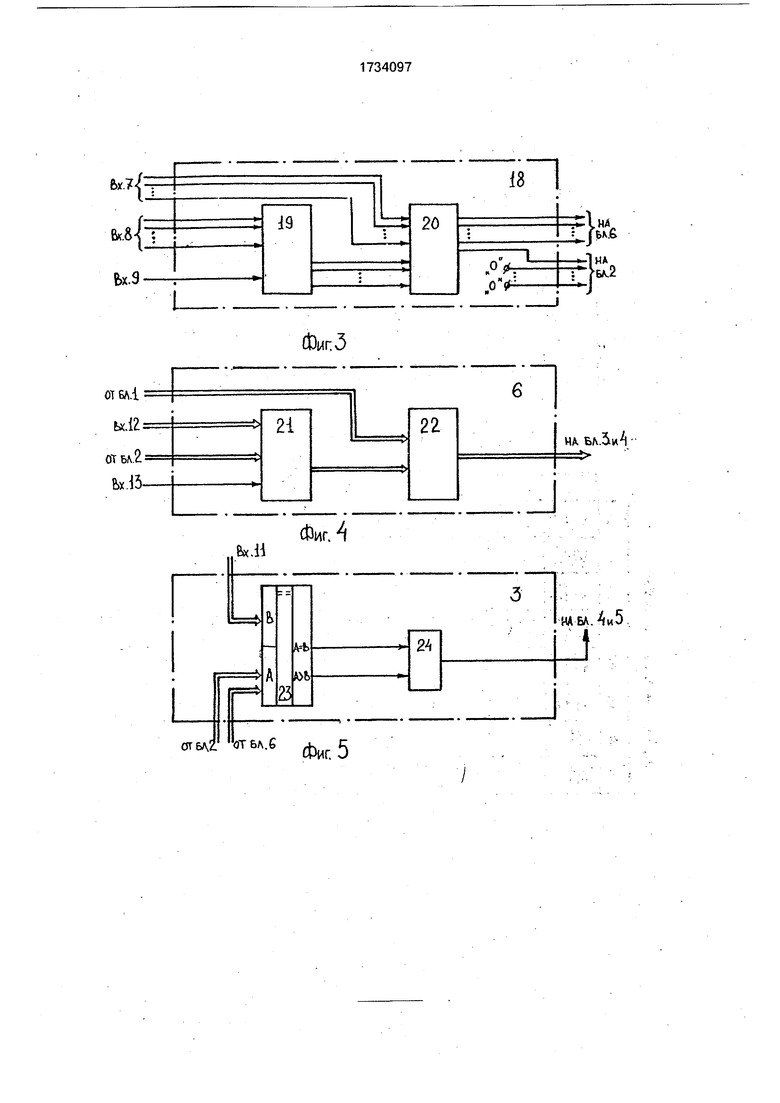

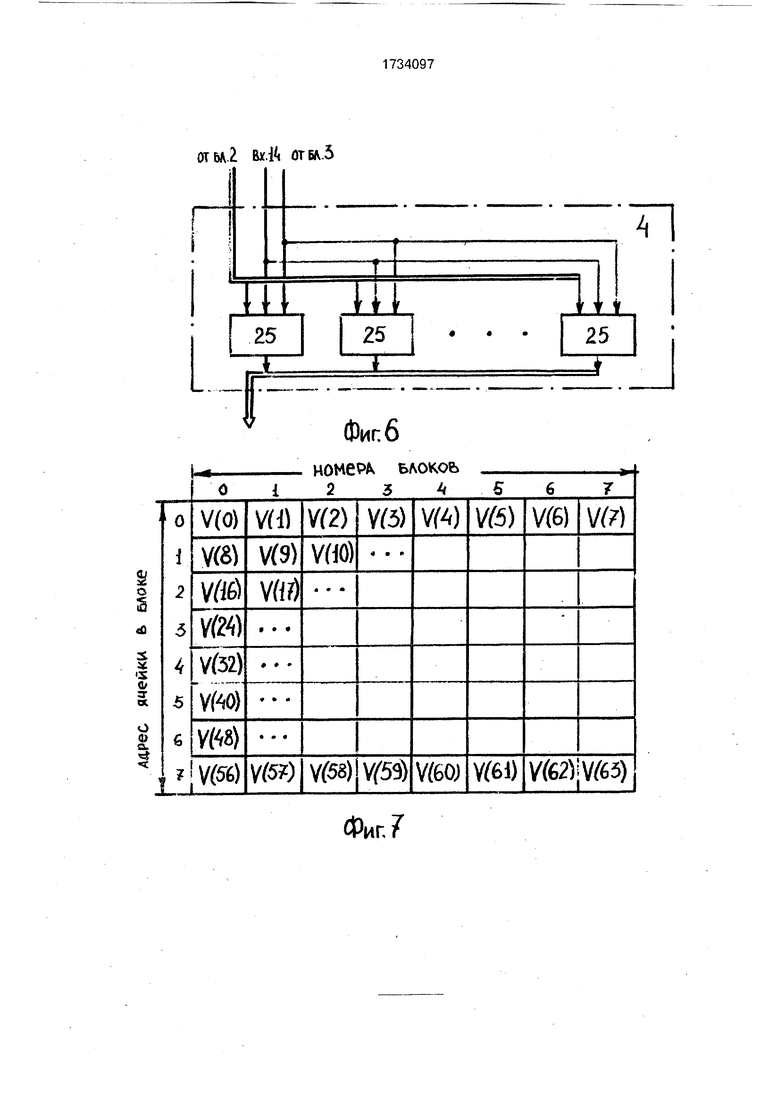

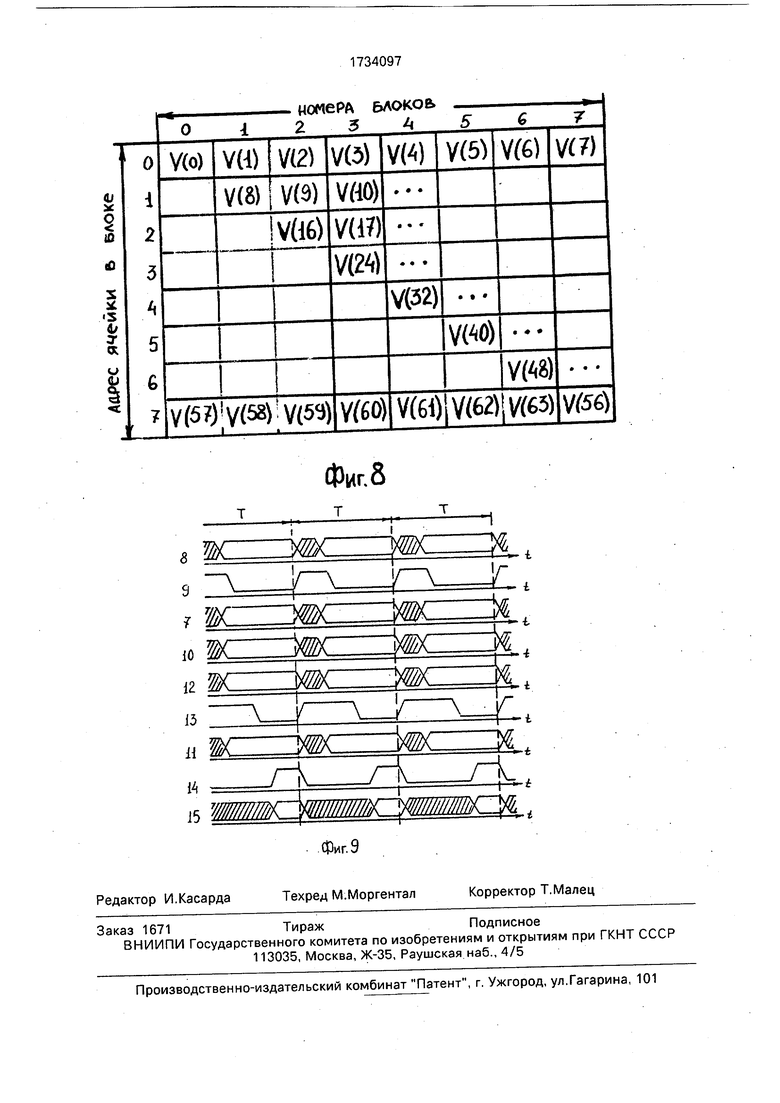

На фиг. 1 представлена функциональная схема устройства для параллельного формирования адресов; на фиг. 2 -функциональная схема блока формирования адресов; на фиг. 3 - функциональная схема узла формирования адреса; на фиг. 4 -функциональная схема узла сдвига адреса; на фиг. 5

-функциональная схема блока сравнения; на фиг. 6 - функциональная схема блока элементов И; на фиг. 7 и 8 - примеры размещения информации в оперативной памяти; на фиг. 9 - временные диаграммы работы устройства.

Устройство (фиг. 1) содержит блок 1 формирования адресов, N сумматоров 2.1 - 2.N, N блоков 3.1 - 3.N сравнения, 2N блоков 4.1

-4.2N элементов И, блок 5 формирования признака окончания адресации, N узлов 6.1

-6.N сдвига адреса. Устройство также имеет вход 7 задания начального номера блока устройства, вход 8 задания шага индекса устройства, вход 9 выбора группы адресов устройства, вход 10 задания адреса ячейки устройства, вход 11 задания границы массива устройства, вход 12 задания кода сдвига адресов устройства, вход 13 разрешения сдвига адреса, вход 14 разрешения выдачи группы адресов, группу выходов 15 старших разрядов группы адресов, группу выходов 16 младших разрядов группы адресов, выход 17 признака окончания адресации устройства.

Блок 1 формирования адресов содержит (фиг. 2) группу узлов 18 формирования адреса 18.

Каждый узел 18 формирования адреса содержит (фиг. 3) блок 19 памяти и сумматор 20.

Узел 6 сдвига адреса содержит (фиг. 4) блок 21 памяти и сумматор 22,

Блок 3 сравнения содержит (фиг.5) элемент 23 сравнения и элемент ИЛИ 24, в частности, в качестве элементов 23 сравнения могут быть использованы микросхемы серий К 555СП1, К 531СП1 и др.

Блок 4 элементов И содержит (фиг. 6) группу 25 трехвходовых элементов И.

На фиг. 9 обозначены: Т - цикл работы устройства; 7, 8, 10-12, 15-информационные сигналы на соответствующих входах (выходах) устройства; 9, 13, 14 - управляющие сигналы на соответствующих входах устройства.

Устройство работает следующим образом.

Основная адресуемая память вычислительной системы, в которой предполагается применение устройства, состоит из Р (Р - целое число) блоков, имеющих независимые

адресные цепи одинаковой разрядности. Полный адрес ячейки основной памяти образуется номером блока (младшие разряды адреса) и номером ячейки в блоке (старшие разряды адреса.

Основной особенностью вычислительной системы, в которой предполагается использование устройства, является то, что операции производятся над векторами - операндами, а результатом является вектор

- операнд. Под вектором понимается массив данных V, состоящий из п элементов V(0), V(1)V(i)V(n-1), где п - ограничивается емкость памяти. Матрица представляется как совокупность определенного

числа векторов - строк. Векторы обычно размещаются в памяти так, что каждый элемент вектора находится в одной ячейке, а номера ячеек следуют или подряд, или в определенной зависимости. Производительность вычислительной системы зависит, с одной стороны, от возможности процессора по обработке векторов-операндов, а с другой стороны - от пропускной способности памяти. Под пропускной способностью памяти понимается количество элементов вектора, записываемое или считываемое в память за единицу времени. Пропускную способность памяти удобно характеризовать количеством W обращений к

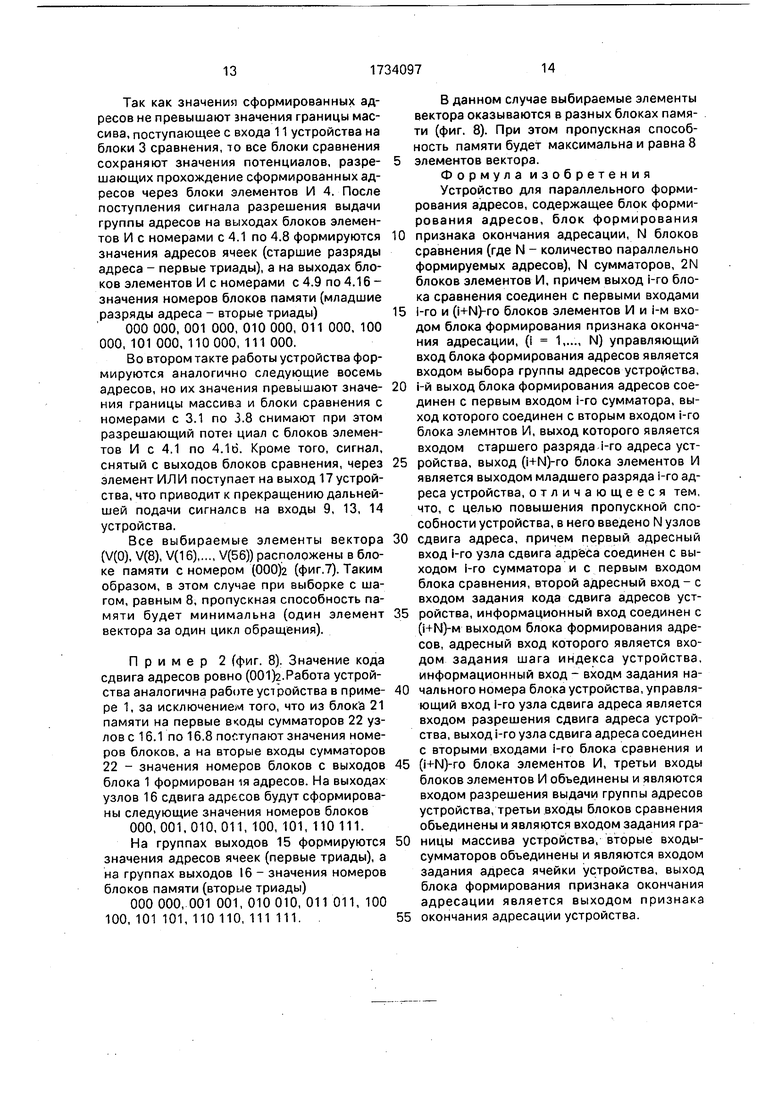

ОП, необходимых для считывания (записи) заданного количества (п) элементов вектора (п Р), Обычно элементы вектора размещаются в подряд расположенных ячейках памяти (фиг. 7). Считывание элементов

вектора возможно или из подряд расположенных ячеек ОП (с шагом h 1), или из ячеек ОП с шагом, отличным от единицы. В общем виде порядок выборки элементов вектора можно представить следующим образом: V(i),V(i+h), V(i+2h)где шаг - h 1.

Необходимость выборки элементов вектора с шагом h 1 возникает, например, при выборке столбцов матрицы, диагональных элементов матрицы и т.д. Адрес ячейки памяти при размещении элементов вектора в подряд расположенных ячейках состоит из двух частей. Первая часть (младшие разряды адреса) определяет номер блока памяти, а вторая часть (старшие разряды адреса) номер ячейки в блоке. Если число модулей памяти равно Р, то К-й элемент вектора (О К (п-1)) будет размещен в блоке с номером Мк, определяемым по формуле Мк KmodP.

Пропускная способность памяти при таком размещении зпеь ентов вектора существенно зависит от шага доступа к ним. Так, например, (фиг. 7) при шаге доступа h 8 выбираемые элементы вектора размещаются в одном блоке памяти, в результате чего возникают конфликты при одновременном обращении к этим элементам вектора. Для снижения конфликтов предлагается размещать элементы вектора не в подряд расположенных ячейках памяти, а в ячейках, номера блоков которых определяются в соответствии с некоторой зависимостью. Такое размещение элементов вектора (фиг. 8) обеспечивается в устройстве с помощью узлов сдвига адреса.

Связь между номерами элементов вектора и номерами блоков, в которых размещаются эти элементы, однозначно устанавливается с помощью зависимости, имеющей вид

MK (K + rK/P)modP, где г 0,1(Р-1).

В частности, при г 0 сдвиг номеров блоков не производится (фиг. 7) и номер блока формируется согласно зависимости, имеющей вид

Мк KmodP.

Значение г формируется программно и поступает с входа 12 задания кода сдвига адресов устройства на вторые адресные входы узлов 6 сдвига адресов.

Адреса операндов поступают от процессора на входы 7, 8,10, 11,12 устройства. Разрядность входа 10 адреса ячейки зависит от количества ячеек в адресуемых блоках памяти. Разрядность входа 8 задания шага индекса зависит от возможных значений шага обращения к элементам вектора. Разрядность входа 7 задания начального номера блока зависит от числа блоков памяти и равна МодаИ , где%|... L наибольшее целое. Разрядность входа 12 задания кода сдвига адресов зависит от числа блоков памяти и равна Jlog2P. Разрядность входа 9 выбора группы адресов (М) зависит от количества узлов формирования адреса 18 в блоке 1 формирования адресов и количества групп (N) узлов 18 и определяется соотношением М P/N. Общее количество узлов 18 равно количеству независимо адресуемых блоков памяти (Р). Структура предлагаемого устройства позволяет варьировать количеством параллельно формируемых адресов (N) в больших пределах от N 1 до N Р. Причем при N 1 работа устройства сводится к последовательному формированию адресов. Код, поступающий на вход 9 выбора группы адресов устройства, является унитарным, т.е. по первому сигналу адресации

с первого разряда шины 9 сигнал разрешения считывания поступает на N узлов 18 первой вертикальной линейки блоков 18 (фиг, 2); по i-му сигналу с входа 9 через i-й

разряд шины сигнал поступает на i-тую вертикальную линейку узлов 18 блока 1 и так далее до М. Если N Р, то шина 9 содержит один разряд, а устройство формирует Р адресов одновременно. Причем устройство

0 позволяет формировать сразу i-тую группу адресов. Количество блоков 3 сравнения, сумматоров 2 и узлов 6 сдвига адреса равно количеству одновременно формируемых адресов (N). Разрядность шин блоков элемен5 тов И с номерами с 4.1 по 4.N равна разрядности входа 10 устройства. Разрядность шин блоков элементов И с номерами с 4.(N+1) no 4.2N равна разрядности входа 7 устройства. Количество элементов И 25 в

0 блоках 4 определяется разрядностью входных шин (фиг. 6). Количество входов блока 5 формирования признака окончания адресации (представляет собой элемент ИЛИ) равно N. Разрядность входа 11 задания

5 границы массива равна сумме разрядностей входов 7 и 10.

С выходов сумматоров 2 на первые входы блоков 3 сравнения поступают все разряды, а на первые адресные входы узлов

0 сдвига адресовJlog2P| , младших разрядов сформированных адресов ячеек. Первый адрес, формируемый устройством, состоит из адреса ячейки (старшие разряды полного адреса) на выходе блока элементов И с но5 мером 4.1 и номера блока (младшие разряды полного адреса) на выходе блока элементов И с номером 4,(N+1).

По первому сигналу, поступающему с входа 9 выбора группы адресов устройства

0 на разрешающий вход блока 1 формирования адресов, на его выходах вырабатывается первая группа адресов. Причем на выходах с первого по N-1 формируются группы старших разрядов полного адреса, а

5 на выходах с (N+1)-ro по 2М-й формируются группы младших разрядов полного адреса. Группы младших разрядов поступают на информационные входы узлов 6 сдвига адресов, а группы старших разрядов поступают

0 на вторые входы сумматоров 2. На первые входы сумматоров 2 поступает значение адреса ячейки с входа 10 устройства. Группы старших разрядов с выходов сумматоров 2 поступают на первые входы блоков 3 срав5 нения. На третьи входы блоков 3 сравнения поступает значение границы массива с входа 11 устройства. На первые адресные входы узлов 6 сдвига адреса поступает JlogaPL разрядов адреса ячейки, сформированного на выходе сумматора 2. На вторые адресные

входы узлов 6 сдвига адреса поступает значение кода сдвига адресов с входа 12 устройства. По сигналу разрешения сдвига, поступающему с входа 13 устройства на разрешающий вход узлов 6 сдвига адреса, на выходе узлов 6 формируются младшие разряды адресов, которые поступают на вторые входы блоков 3 сравнения.

Кроме того, сформированные номера блоков являются первыми группами входов элементов И 4.(N+1) - 4.(2N). С выходов сумматоров 2 значения старших разрядов адреса (адреса ячеек) поступают на первые группы входов элементов И 4.1 - 4.N. В случае, если сформированный адрес превы- шает значение границы массива (или достигает его) i-тый блок 3 сравнения снимает потенциал со своего выхода, в результате чего на выходе блока 5 формируется единичный сигнал, поступающий на выход 17 при- знака окончания адресации устройства.

Кроме того, с выхода i-ro блока 3 сравнения снимается единичный потенциал на втором входе блоков элементов И 4.1 и 4.(N+i), т.е. происходит запрещение форми- рования i-ro адреса. Все последующие формируемые адреса также превышают значение границы массива. По сигналу разрешения выдачи группы адресов, поступающему с входа 14 устройства, на третьи входы блоков элементов И с выходов блоков элементов И с номерами с 4.1 по 4.N поступают значения старших разрядов сформированных адресов на группу выходов 15 устройства, а с выходов блоков элементов И с номерами с 4,(N+1) no 4.2N поступают значения младших разрядов группы адресов на группу выходов 16 устройства, В результате формируется п адресов. Первый цикл работы устройства (фиг. 9) закончен.

Во втором цикле работы устройства и последующих формируются по N очередных адресов, пока при очередном цикле сформированный адрес не превышает значение границы массива (или достигает его) и не вырабатывается признак окончания адресации на выходе 17 устройства. По сигналу окончания адресации устройство заканчивает работу, т.е. прекращается подача на входы 9,13, 14 соответственно сигналов вы- бора группы адресов, разрешения сдвига, разрешения выдачи группы адресов,

Узел сдвига адреса (фиг. 4) работает следующим образом.

С первого и второго адресных входов узла 6 значения младших и старших разрядов адреса поступают на адресный вход блока 21 памяти. На разрешающий вход блока 21 памяти с разрешающего входа узла 6 поступает сигнал выборки, по которому на

выходе блока 21 памяти формируется записанное в него заранее значение номера блока в соответствии с таблицей.

С выхода блока 21 значение номера блока поступает на первый вход сумматора 22. На второй вход сумматора 22 с информационного входа узла 6 поступает значение номера блока, сформированное в блоке 1. Сумматор 22 путем поразрядного суммирования по модулю Р значений, поступающих на первый и второй входы, формирует на выходе узла значение номера блока.

Пример параллельного формирования адресов устройством. Предположим, что количество блоков памяти Р 8, N 8, М 1; значение шага индекса равно восьми; начальное значение номера ячейки равно (000)2; начальное значение номера блока равно (000)2 значение границы массива равно (1000000)2.

Пример 1 (фиг. 7), Код сдвига адресов на входе 12 устройства равен (000)2. Значения шага индекса и номера блока поступают на блок 1 формирования адресов. По сигналу выбора группы адресов.из блоков 19 памяти одного (так как N Р, а М 1) столбца узлов 18 формирования адресов в первом такте работы устройства (фиг. 9) поступают значения номеров ячеек на первые входы сумматоров 20 (значения приведены в двоичном коде)

000 000, 001 000, 010 000, 011 000, 100 000, 101 000, 110000, 111 000.

На вторые входы сумматоров 20 поступает значение номера блока с входа 7 устройства. На первых группах выходов (с 1-й по 8-мую) блока 1 формируются значения адресуемых ячеек, а на группах выходов (с 9-й по 16-ую) формируются значения номеров блоков

000 000, 001 000, 010 000, 011 000, 100 000, 101 000, 110000, 111 000, где первая триада - это значение номера ячейки, а вторая - значение номера блока.

Значение начального адреса ячейки с входа 10 устройства поступает на первые входы сумматоров с 2.1 по 2.8, а на вторые входы сумматоров поступают значения номера ячейки, сформированные в блоке 1. На выходе сумматоров 2 вырабатываются значения старших групп адресов устройства (номер ячейки в блоке). Так как значение на входе 12 сдвига адресов равно (000)2, то на выходе блоков 21 памяти узлов 6 сдвига адресов формируются нулевые значения номеров блоков по сигналу разрешения сдвига с входа 13 устройства, а на выходе узлов 6 формируются значения номеров блоков, равные

000, 000, 000, 000, 000, 000, 000, 000.

Так как значения сформированных адресов не превышают значения границы массива, поступающее с входа 11 устройства на блоки 3 сравнения, то все блоки сравнения сохраняют значения потенциалов, разрешающих прохождение сформированных адресов через блоки элементов И 4. После поступления сигнала разрешения выдачи группы адресов на выходах блоков элементов И с номерами с 4.1 по 4.8 формируются значения адресов ячеек (старшие разряды адреса - первые триады), а на выходах блоков элементов И с номерами с 4.9 по 4.16 - значения номеров блоков памяти (младшие разряды адреса - вторые триады)

000 000, 001 000, 010 000, 011 000, 100 000, 101 000, 110000, 111 000.

Во втором такте работы устройства формируются аналогично следующие восемь адресов, но их значения превышают значения границы массива и блоки сравнения с номерами с 3.1 по 3.8 снимают при этом разрешающий noTet циал с блоков элементов И с 4.1 по 4.16. Кроме того, сигнал, снятый с выходов блоков сравнения, через элемент ИЛИ поступает на выход устройства, что приводит к прекращению дальнейшей подачи сигналсв на входы 9, 13, 14 устройства.

Все выбираемые элементы вектора (V(0), V(8), V(16)V(56)) расположены в блоке памяти с номером (000)2 (фиг.7). Таким образом, в этом случае при выборке с шагом, равным 8, пропускная способность памяти будет минимальна (один элемент вектора за один цикл обращения).

Пример 2 (фиг. 8). Значение кода сдвига адресов ровно (001)2.Работа устройства аналогична работе устройства в примере 1, за исключением того, что из блок а 21 памяти на первые вкоды сумматоров 22 узлов с 16.1 по 16.8 поступают значения номеров блоков, а на вторые входы сумматоров 22 - значения номеров блоков с выходов блока 1 формирован тя адресов. На выходах узлов 16 сдвига адресов будут сформированы следующие значения номеров блоков

000,001,010,011, 100, 101, 110111.

На группах выходов 15 формируются значения адресов ячеек (первые триады), а на группах выходов 16 - значения номеров блоков памяти (вторые триады)

000000, 001 001, 010010, 011 011, 100 100, 101 101, 110 110, 111 111.

В данном случае выбираемые элементы вектора оказываются в разных блоках памяти (фиг. 8). При этом пропускная способность памяти будет максимальна и равна 8

элементов вектора.

Формула изобретения Устройство для параллельного формирования адресов, содержащее блок формирования адресов, блок формирования

признака окончания адресации, N блоков сравнения (где N - количество параллельно формируемых адресов), N сумматоров, 2N блоков элементов И, причем выход i-ro блока сравнения соединен с первыми входами

i-ro и (i+N)-ro блоков элементов И и i-м входом блока формирования признака окончания адресации, (i 1 N) управляющий

вход блока формирования адресов является входом выбора группы адресов устройства,

i-й выход блока формирования адресов соединен с первым входом i-ro сумматора, выход которого соединен с вторым входом i-ro блока элемнтов И, выход которого является входом старшего разряда i-ro адреса устройства, выход (i+N)-ro блока элементов И является выходом младшего разряда 1-го адреса устройства, отличающееся тем, что, с целью повышения пропускной способности устройства, в него введено N узлов

сдвига адреса, причем первый адресный вход i-ro узла сдвига адреса соединен с выходом 1-го сумматора и с первым входом блока сравнения, второй адресный вход - с входом задания кода сдвига адресов устройства, информационный вход соединен с (i+N)-M выходом блока формирования адресов, адресный вход которого является входом задания шага индекса устройства, информационный вход- входм задания начального номера блока устройства, управляющий вход i-ro узла сдвига адреса является входом разрешения сдвига адреса устройства, выход i-ro узла сдвига адреса соединен с вторыми входами i-ro блока сравнения и

(i+N)-ro блока элементов И, третьи входы блоков элементов И объединены и являются входом разрешения выдачи группы адресов устройства, третьи входы блоков сравнения объединены и являются входом задания границы массива устройства, вторые входы- сумматоров объединены и являются входом задания адреса ячейки устройства, выход блока формирования признака окончания адресации является выходом признака

окончания адресации устройства.

Вх.8

Ьх.9:

JW.2

НД БА 6

НАБА.2

Фиг.З

Ч, 6v6

НА

0Ш.2 to.tt OTSV.5

25

Фиг 6

S

о

s

у

S

ф

DC

о

D

О.

Фиг7

4

1 Г , г I

JL

25

25

| Устройство для формирования адреса | 1979 |

|

SU826350A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Формирователь адреса | 1982 |

|

SU1062703A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для параллельного формирования адресов | 1988 |

|

SU1575181A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-15—Публикация

1990-06-12—Подача