Изобретение относится к автоматике и вычислительной технике и может быть использовано в составе специализированных быстродействующих вычислительных систем обработки изображений.

Целью изобретения является повышение быстродействия.

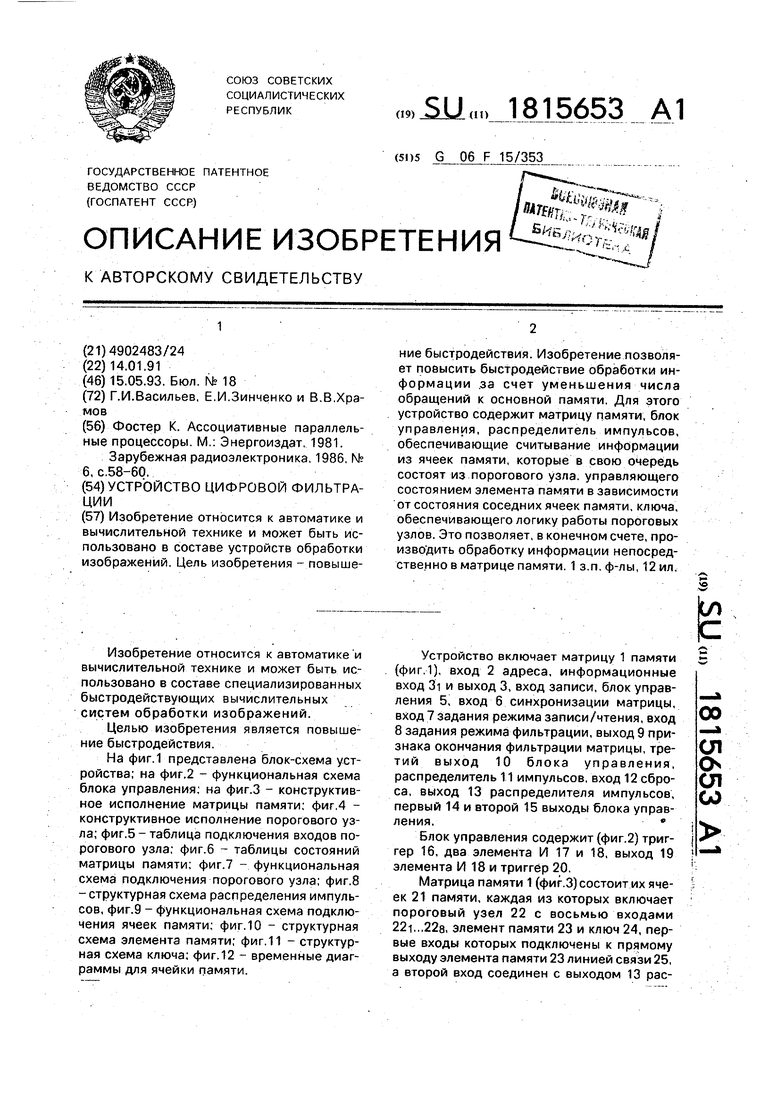

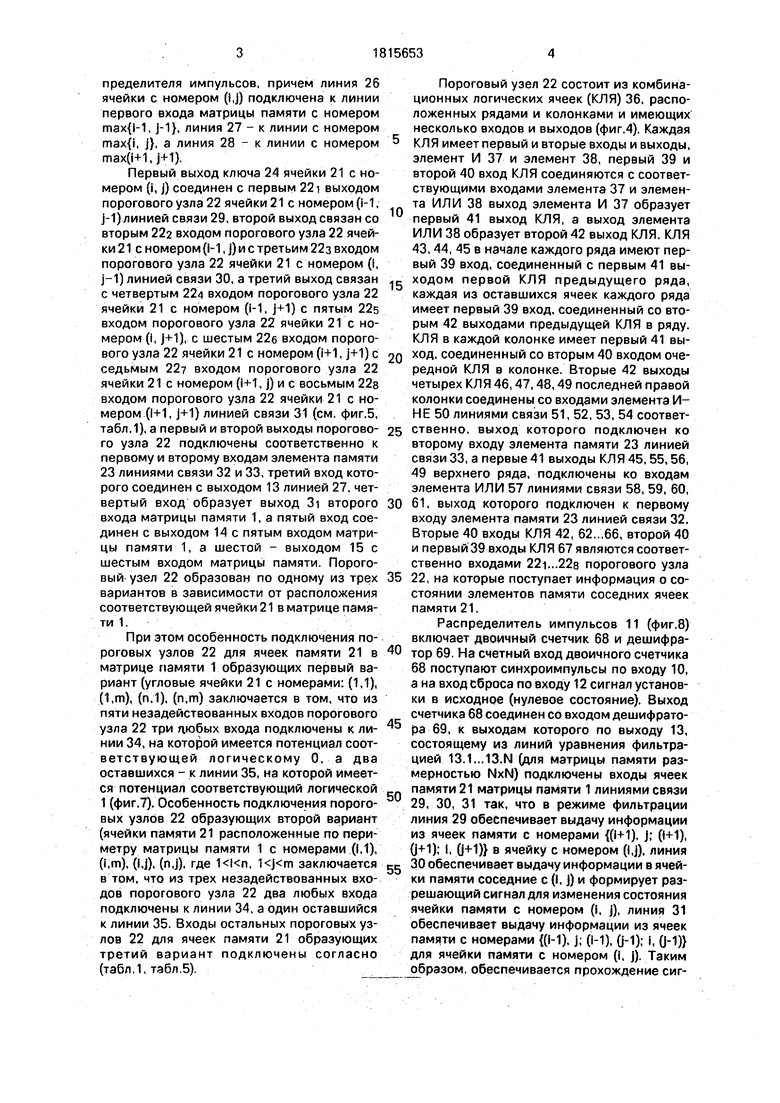

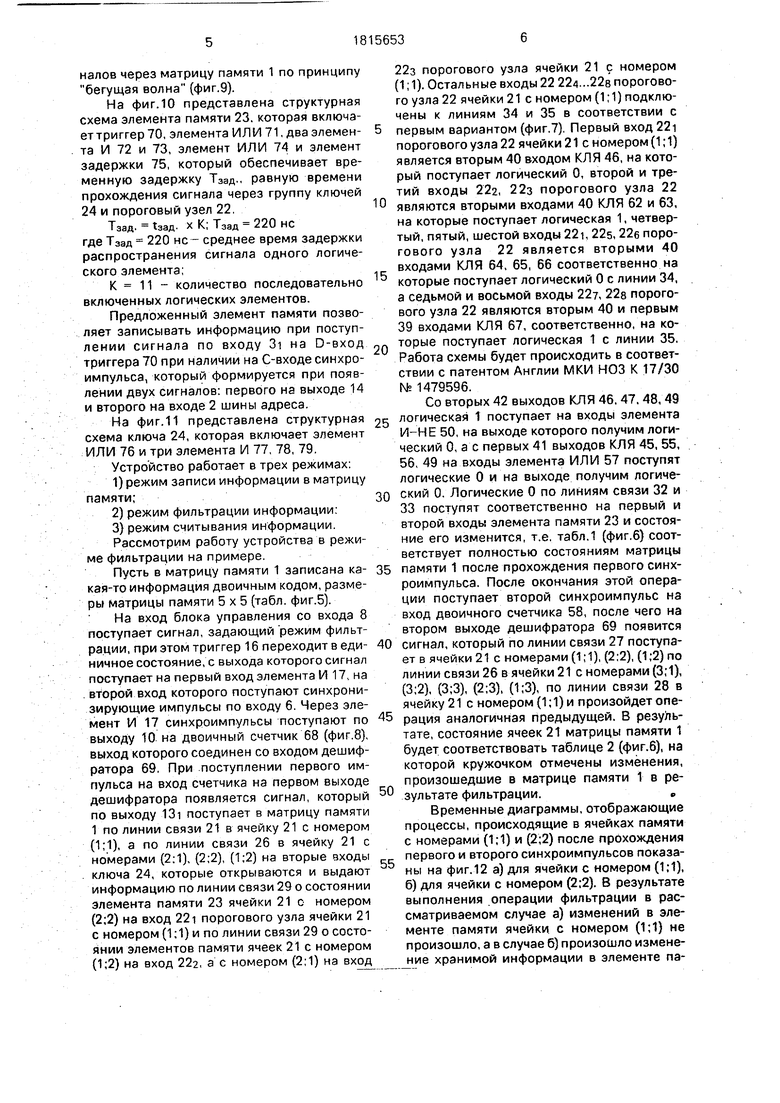

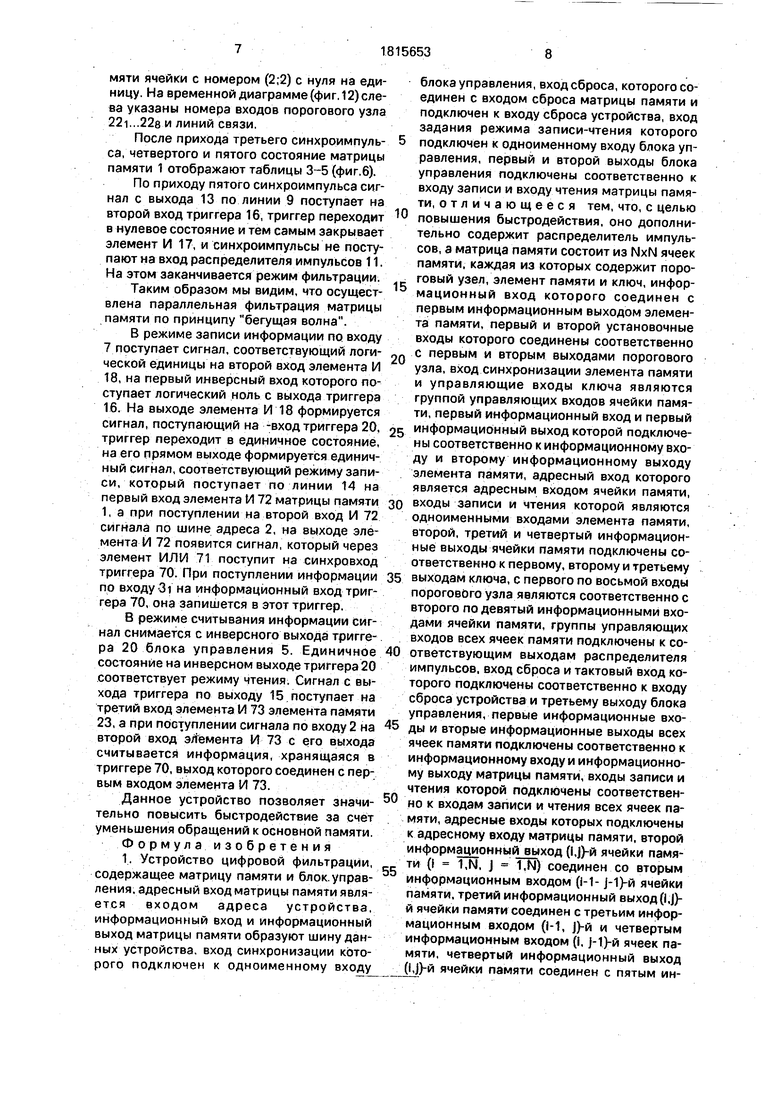

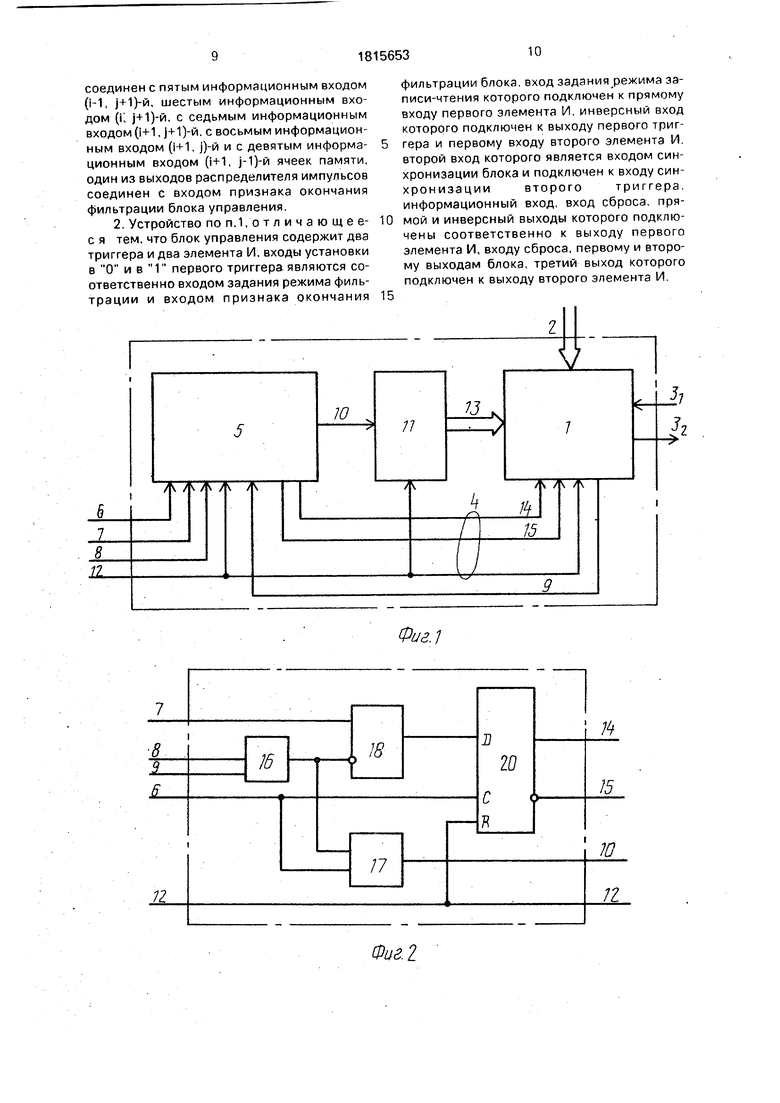

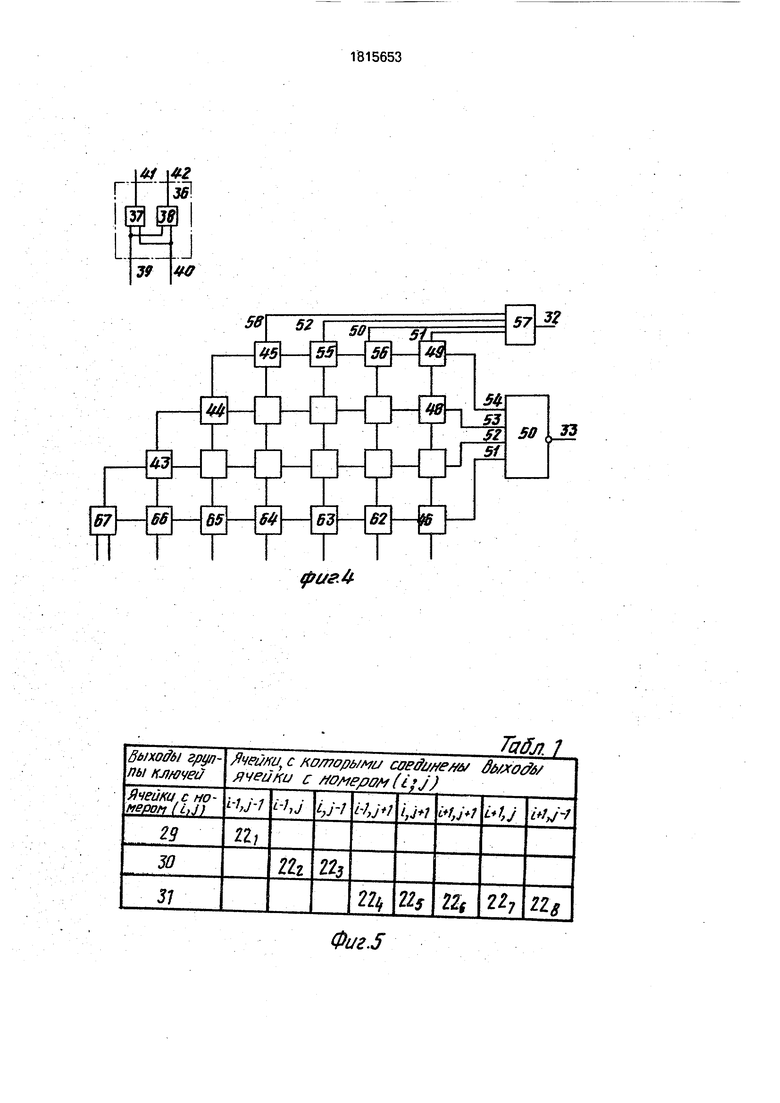

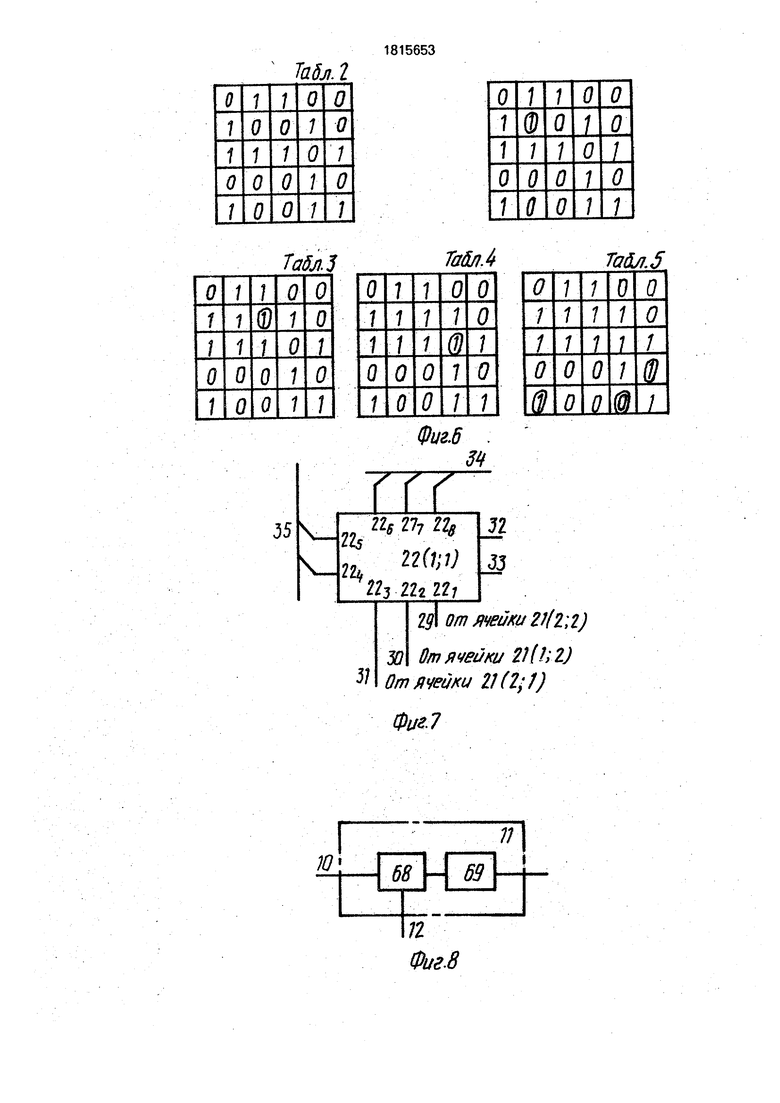

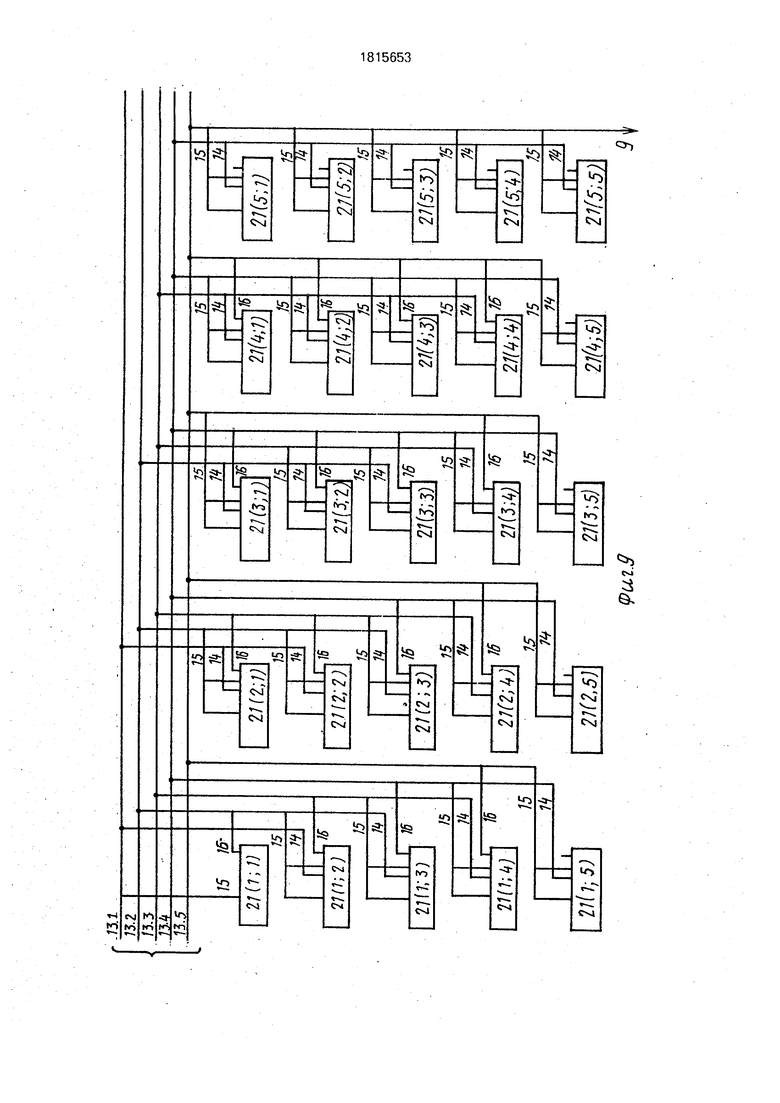

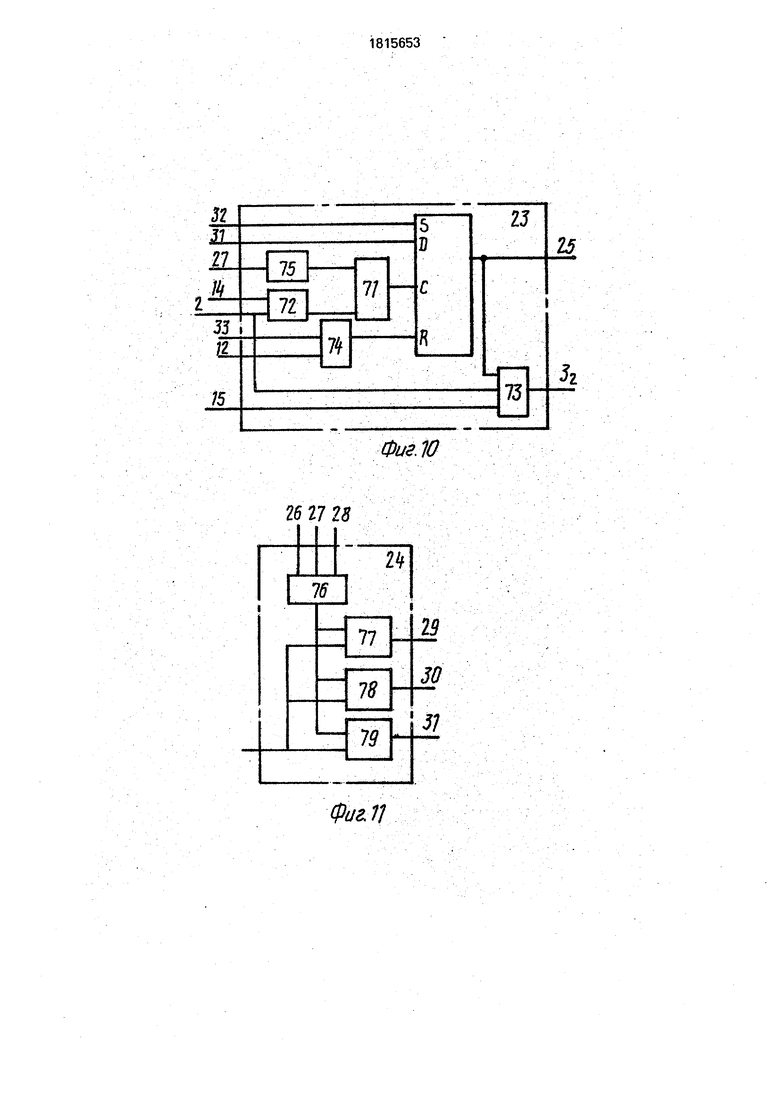

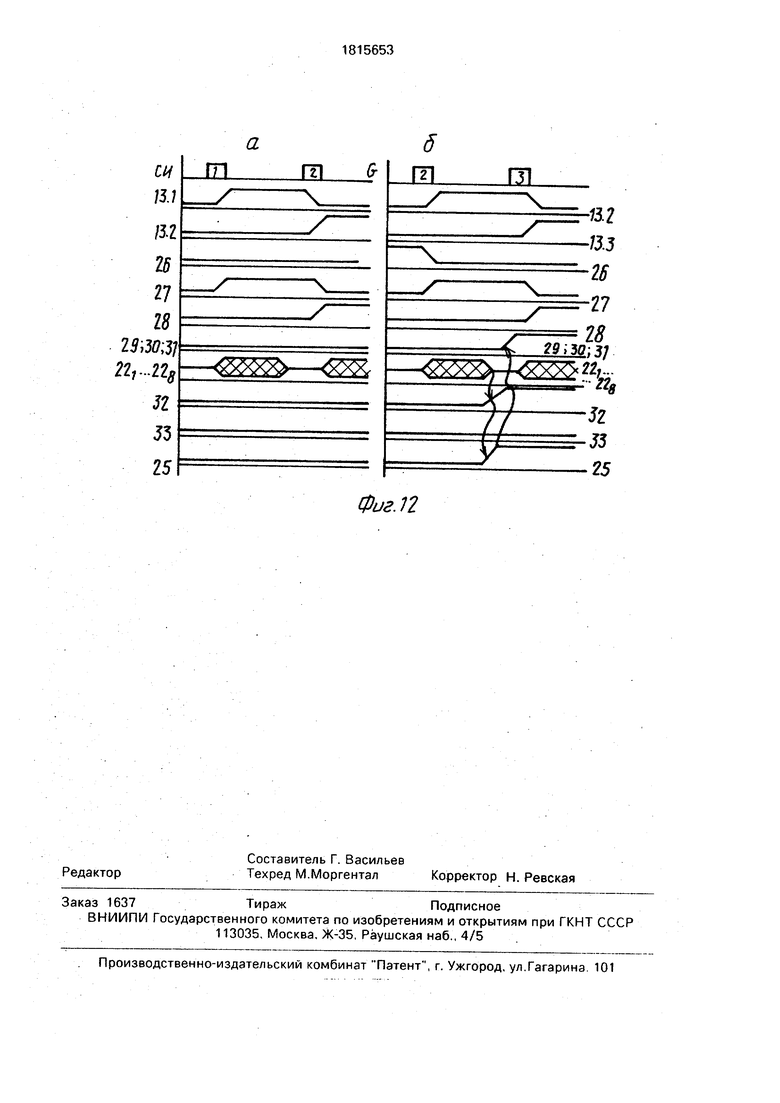

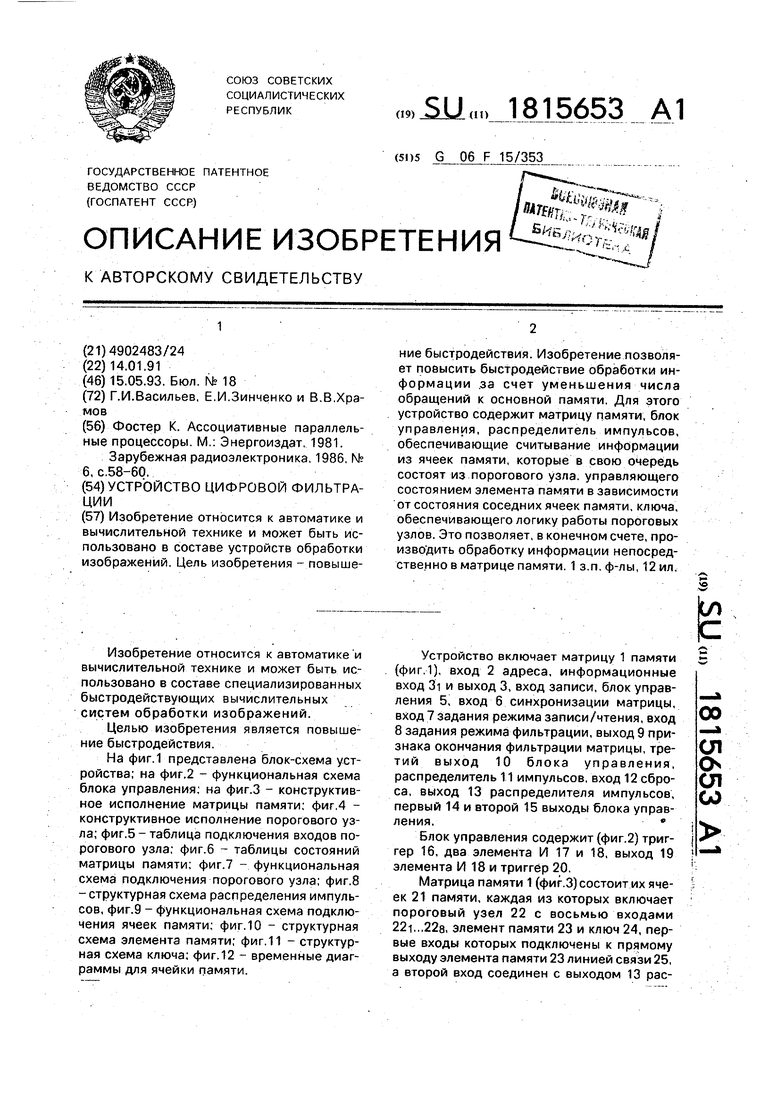

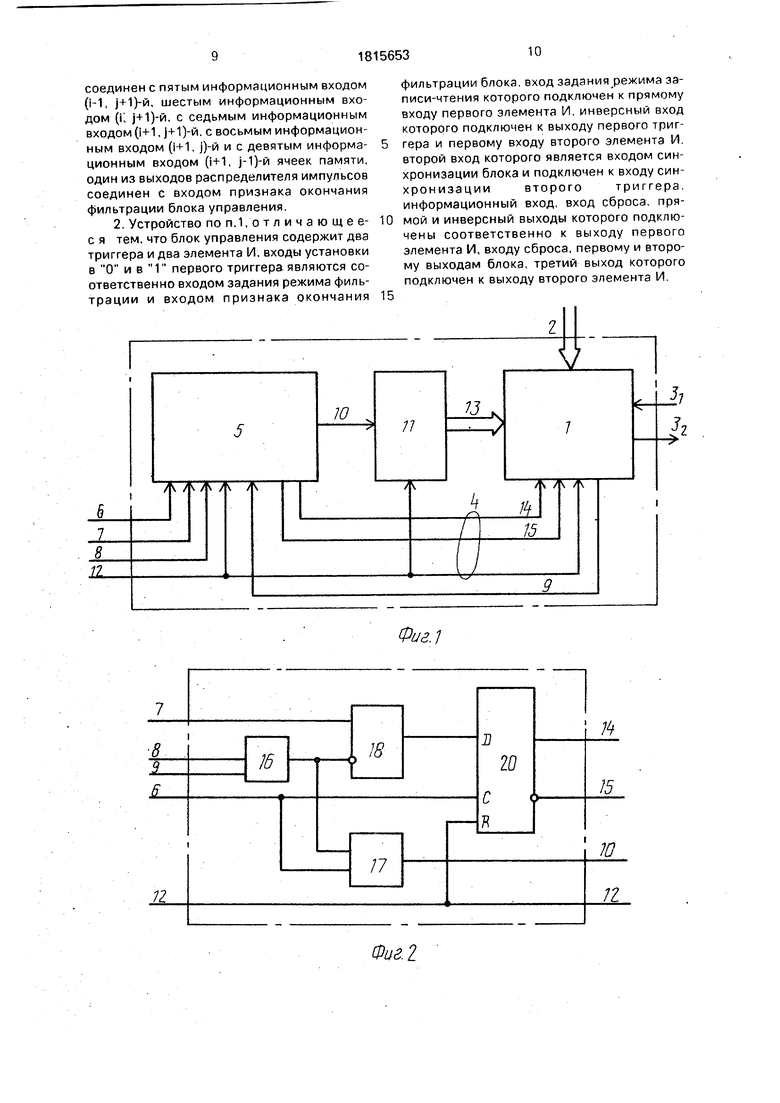

На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональная схема блока управления; на фиг.З - конструктивное исполнение матрицы памяти; фиг,4 - конструктивное исполнение порогового узла; фиг.5 - таблица подключения входов порогового узла; фиг.6 - таблицы состояний матрицы памяти; фиг.7 -. функциональная схема подключения порогового узла; фиг.8 - структурная схема распределения импульсов, фиг.9 - функциональная схема подключения ячеек памяти; фиг. 10 - структурная схема элемента памяти; фиг. 11 - структурная схема ключа; фиг. 12 - временные диаграммы для ячейки памяти.

Устройство включает матрицу 1 памяти (фиг.1), вход 2 адреса, информационные вход и выход 3, вход записи, блок управления 5, вход 6 синхронизации матрицы, вход 7 задания режима записи/чтения, вход 8 задания режима фильтрации, выход 9 признака окончания фильтрации матрицы, третий выход 10 блока управления, распределитель 1.1 импульсов, вход 12 сброса, выход 13 распределителя импульсов, первый 14 и второй 15 выходы блока управления.

Блок управления содержит (фиг.2) триггер 16, два элемента И 17 и 18, выход 19 элемента И 18 и триггер 20.

Матрица памяти 1 (фиг.З) состоит их ячеек 21 памяти, каждая из которых включает пороговый узел 22 с восьмью входами 221...228, элемент памяти 23 и ключ 24, первые входы которых подключены к прямому выходу элемента памяти 23 линией связи 25, а второй вход соединен с выходом 13 рас00

ел о ел со

пределителя импульсов, причем линия 26 ячейки с номером (l,j) подключена к линии первого входа матрицы памяти с номером max{i-1, J-1}, линия 27 - к линии с номером maxji, j}, а линия 28 - к линии с номером max(i+1, j-H).

Первый выход ключа 24 ячейки 21с номером (i, j) соединен с первым 221 выходом порогового узла 22 ячейки 21 с номером (И, j-1) линией связи 29, второй выход связан со вторым 222 входом порогового узла 22 ячейки 21 с номером (И, j) и с третьим 22з входом порогового узла 22 ячейки 21 с номером (I, j-1) линией связи 30, а третий выход связан с четвертым 224 входом порогового узла 22 ячейки 21 с номером (И, J+1) с пятым 22s входом порогового узла 22 ячейки 21с номером (I, J+1), с шестым 22б входом порогового узла 22 ячейки 21 с номером р+1, j+Т) с седьмым 22 входом порогового узла 22 ячейки 21 с номером (1+1, j)n с восьмым 22в входом порогового узла 22 ячейки 21 с номером (1+1, J+1) линией связи 31 (ем. фиг.5, табл.1), а первый и второй выходы порогового узла 22 подключены соответственно к первому и второму входам элемента памяти 23 линиями связи 32 и 33, третий вход которого соединен с выходом 13 линией 27, четвертый вход образует выход 3i второго входа матрицы памяти 1, а пятый вход соединен с выходом 14 с пятым входом матрицы памяти 1, а шестой - выходом 15 с шестым входом матрицы памяти. Пороговый узел 22 образован по одному из трех вариантов в зависимости от расположения соответствующей ячейки 21 в матрице памяти 1.

При этом особенность подключения пороговых узлов 22 для ячеек памяти 21 в матрице памяти 1 образующих первый вариант (угловые ячейки 21 с номерами: (1,1), (1,m), (n,1), (n,m) заключается в том, что из пяти незадействованных входов порогового узла 22 три дюбых входа подключены к линии 34, на которой имеется потенциал соответствующей логическому 0, а два оставшихся - к линии 35, на которой имеется потенциал соответствующий логической 1 (фиг.7). Особенность подключения пороговых узлов 22 образующих второй вариант (ячейки памяти 21 расположенные по периметру матрицы памяти 1 с номерами (1,1), (i,m), (i.j), (n,j), где , заключается в том, что из трех незадействованных входов порогового узла 22 два любых входа подключены к линии 34, а один оставшийся к линии 35. Входы остальных пороговых узлов 22 для ячеек памяти 21 образующих третий вариант подключены согласно (табл.1, табл.5).

0

5

5

0

Пороговый узел 22 состоит из комбинационных логических ячеек (КЛЯ) 36. расположенных рядами и колонками и имеющих несколько входов и выходов (фиг.4). Каждая КЛЯ имеет первый и вторые входы и выходы, элемент И 37 и элемент 38, первый 39 и второй 40 вход КЛЯ соединяются с соответствующими входами элемента 37 и элемента ИЛИ 38 выход элемента И 37 образует первый 41 выход КЛЯ, а выход элемента ИЛИ 38 образует второй 42 выход КЛЯ. КЛЯ 43, 44, 45 в начале каждого ряда имеют первый 39 вход, соединенный с первым 41 выходом первой КЛЯ предыдущего ряда, каждая из оставшихся ячеек каждого ряда имеет первый 39 вход, соединенный со вторым 42 выходами предыдущей КЛЯ в ряду. КЛЯ в каждой колонке имеет первый 41 вы0 ход, соединенный со вторым 40 входом очередной КЛЯ в колонке. Вторые 42 выходы четырех КЛЯ 46,47,48,49 последней правой колонки соединены со входами элемента И- НЕ 50 линиями связи 51, 52, 53, 54 соответственно, выход которого подключен ко второму входу элемента памяти 23 линией связи 33, а первые 41 выходы КЛЯ 45,55,56, 49 верхнего ряда, подключены ко входам элемента ИЛИ 57 линиями связи 58, 59, 60, 61, выход которого подключен к первому входу элемента памяти 23 линией связи 32. Вторые 40 входы КЛЯ 42, 62,..66, второй 40 и первыйЗЭ входы КЛЯ 67 являются соответственно входами 22i...22e порогового узла

5 22, на которые поступает информация о состоянии элементов памяти соседних ячеек памяти 21.

Распределитель импульсов 11 (фиг.8) включает двоичный счетчик 68 и дешифра0 тор 69. На счетный вход двоичного счетчика 68 поступают синхроимпульсы по входу 10, а на вход Сброса по входу 12 сигнал установки в исходное (нулевое состояние). Выход счетчика 68 соединен со входом дешифратора 69, к выходам которого по выходу 13, состоящему из линий уравнения фильтрацией 13.1...13.N (для матрицы памяти размерностью NxN) подключены входы ячеек памяти 21 матрицы памяти 1 линиями связи 29, 30, 31 так, что в режиме фильтрации линия 29 обеспечивает выдачу информации из ячеек памяти с номерами {(i+1), j; 0+1), G+ O. t. 0+1)} в ячейку с номером (l,j), линия

5 30 обеспечивает выдачу информации в ячейки памяти соседние с (I, j) и формирует разрешающий сигнал для изменения состояния ячейки памяти с номером (i, j), линия 31 обеспечивает выдачу информации из ячеек памяти с номерами {(И), j; (1-1), (j-1); i, (j-1)} для ячейки памяти с номером (i, j). Таким образом, обеспечивается прохождение сиг5

0

налов через матрицу памяти 1 по принципу бегущая волна (фиг,9).

На фиг.10 представлена структурная схема элемента памяти 23. которая включа- еттриггерТО, элемента ИЛИ 71, два элемента И 72 и 73, элемент ИЛИ 74 и элемент задержки 75, который обеспечивает временную задержку Тзад., равную времени прохождения сигнала через группу ключей 24 и пороговый узел 22.

Тзад. 1зад. X К; Тзад 220 НС

где Т3ад 220 не- среднее время задержки распространения сигнала одного логического элемента;

К 11 - количество последовательно включенных логических элементов.

Предложенный элемент памяти позволяет записывать информацию при поступлении сигнала по входу 3t на D-вход триггера 70 при наличии на С-входе синхроимпульса, который формируется при появлении двух сигналов: первого на выходе 14 и второго на входе 2 шины адреса.

На фиг.11 представлена структурная схема ключа 24, которая включает элемент ИЛИ 76 и три элемента И 77, 78, 79.

Устройство работает в трех режимах:

1) режим записи информации в матрицу памяти;

2) режим фильтрации информации:

3} режим считывания информации.

Рассмотрим работу устройства в режиме фильтрации на примере.

Пусть в матрицу памяти 1 записана какая-то информация двоичным кодом, размеры матрицы памяти 5x5 (табл. фиг.5).

На вход блока управления со входа 8 поступает сигнал, задающий режим фильтрации, при этом триггер 16 переходит в единичное состояние, с выхода которого сигнал поступает на первый вход элемента И 17, на . второй вход которого поступают синхронизирующие импульсы по входу 6. Через элемент И 17 синхроимпульсы поступают по выходу 10 на двоичный счетчик 68 (фиг.8), выход которого соединен со входом дешифратора 69. При поступлении первого импульса на вход счетчика на первом выходе дешифратора появляется сигнал, который по выходу 13i поступает в матрицу памяти 1 по линии связи 21 в ячейку 21 с номером (1;1), а по линии связи 26 в ячейку 21 с номерами (2:1), (2;2), (1;2) на вторые входы ключа 24, которые открываются и выдают информацию по линии связи 29 о состоянии элемента памяти 23 ячейки 21 с номером (2;2) на вход 221 порогового узла ячейки 21 с номером (1;1) и по линии связи 29 о состоянии элементов памяти ячеек 21с номером (1;2) на вход 222, а с номером (2;1) на вход

0

5

0

5

0

5

0

5

0

5

22з порогового узла ячейки 21 с номером (1; 1). Остальные входы 22 224...22в порогового узла 22 ячейки 21с номером (1 ;1) подключены к линиям 34 и 35 в соответствии с первым вариантом (фиг.7). Первый вход 22i порогового узла 22 ячейки 21с номером (1; 1) является вторым 40 входом КЛЯ 46, на который поступает логический 0, второй и третий входы 222, 22з порогового узла 22 являются вторыми входами 40 КЛЯ 62 и 63, на которые поступает логическая 1, четвертый, пятый, шестой входы 221, 22s, 22e порогового узла 22 является вторыми 40 входами КЛЯ 64, 65, 66 соответственно на которые поступает логический 0 с линии 34, а седьмой и восьмой входы 22т, 22а порогового узла 22 являются вторым 40 и первым 39 входами КЛЯ 67, соответственно, на которые поступает логическая 1 с линии 35. Работа схемы будет происходить в соответствии с патентом Англии МКИ НОЗ К 17/30 № 1479596.

Со вторых 42 выходов КЛЯ 46, 47, 48, 49 логическая 1 поступает на входы элемента И-НЕ 50, на выходе которого получим логический 0, ас первых 41 выходов КЛЯ 45, 55, 56, 49 на входы элемента ИЛИ 57 поступят логические 0 и на выходе получим логический 0. Логические 0 по линиям связи 32 и 33 поступят соответственно на первый и второй входы элемента памяти 23 и состояние его изменится, т.е, табл.1 (фиг.6) соответствует полностью состояниям матрицы памяти 1 после прохождения первого синхроимпульса. После окончания этой операции поступает второй синхроимпульс на вход двоичного счетчика 58, после чего на втором выходе дешифратора 69 появится сигнал, который по линии связи 27 поступает в ячейки 21 с номерами (1;1), (2;2), (1;2) по линии связи 26 в ячейки 21 с номерами (3;1), (3;2), (3;3), (2;3), (1:3), по линии связи 28 в ячейку 21 с номером (1;1) и произойдет операция аналогичная предыдущей. В результате, состояние ячеек 21 матрицы памяти 1 будет соответствовать таблице 2 (фиг.6), на которой кружочком отмечены изменения, произошедшие в матрице памяти 1- в результате фильтрации.

Временные диаграммы, отображающие процессы, происходящие в ячейках памяти с номерами (1;1) и (2;2) после прохождения первого и второго синхроимпульсов показаны на фиг.12 а) для ячейки с номером (1;1), б) для ячейки с номером (2;2). В результате выполнения операции фильтрации в рассматриваемом случае а) изменений в элементе памяти ячейки с номером (1;1) не произошло, а в случае б) произошло изменение хранимой информации в элементе памяти ячейки с номером (2:2) с нуля на единицу. На временной диаграмме (фиг. 12) слева указаны номера входов порогового узла 22i...22e и линий связи.

После прихода третьего синхроимпульса/четвертого и пятого состояние матрицы памяти 1 отображают таблицы 3-5 (фиг.6).

По приходу пятого синхроимпульса сигнал с выхода 13 по линии 9 поступает на второй вход триггера 16, триггер переходит в нулевое состояние и тем самым закрывает элемент И 17, и синхроимпульсы не поступают на вход распределителя импульсов 11. На этом заканчивается режим фильтрации.

Таким образом мы видим, что осуществлена параллельная фильтрация матрицы памяти по принципу бегущая волна.

В режиме записи информации по входу 7 поступает сигнал, соответствующий логической единицы на второй вход элемента И 18, на первый инверсный вход которого поступает логический ноль с выхода триггера 16. На выходе элемента И 18 формируется сигнал, поступающий на -вход триггера 20, триггер переходит в единичное состояние, на его прямом выходе формируется единичный сигнал, соответствующий режиму записи, который поступает по линии 14 на первый вход элемента И 72 матрицы памяти 1, а при поступлении на второй вход И 72 сигнала по шине адреса 2, на выходе элемента И 72 появится сигнал, который через элемент ИЛИ 71 поступит на синхровход триггера 70. При поступлении информации по входу-31 на информационный вход триггера 70, она запишется в этот триггер.

В режиме считывания информации сигнал снимается с инверсного выхода триггера 20 блока управления 5. Единичное состояние на инверсном выходе триггера 20 соответствует режиму чтения. Сигнал с выхода триггера по выходу 15 поступает на третий вход элемента И 73 элемента памяти 23, а при поступлении сигнала по входу 2 на второй вход э/темента И 73 с его выхода считывается информация, хранящаяся в триггере 70, выход которого соединен с первым входом элемента И 73.

Данное устройство позволяет значительно повысить быстродействие за счёт уменьшения обращений к основной памяти. .Фор мула, изобретения

1. Устройство цифровой фильтрации, содержащее матрицу памяти и блок, управления, адресный вход матрицы памяти является входом адреса устройства, информационный вход и информационный выход матрицы памяти образуют шину данных устройства, вход синхронизации которого подключен к одноименному входу

0

5

0

5

0

5

0

5

0

5

блока управления, вход сброса, которого соединен с входом сброса матрицы памяти и подключен к входу сброса устройства, вход задания режима записи-чтения которого подключен к одноименному входу блока управления, первый и второй выходы блока управления подключены соответственно к входу записи и входу чтения матрицы памяти, отличающееся тем, что, с целью повышения быстродействия, оно дополнительно содержит распределитель импульсов, а матрица памяти состоит из NxN ячеек памяти, каждая из которых содержит пороговый узел, элемент памяти и ключ, информационный вход которого соединен с первым информационным выходом элемента памяти, первый и второй установочные входы которого соединены соответственно с первым и вторым выходами порогового узла, вход синхронизации элемента памяти и управляющие входы ключа являются группой управляющих входов ячейки памяти, первый информационный вход и первый информационный выход которой подключены соответственно к информационному входу и второму информационному выходу элемента памяти, адресный вход которого является адресным входом ячейки памяти, входы записи и чтения которой являются одноименными входами элемента памяти, второй, третий и четвертый информационные выходы ячейки памяти подключены соответственно к первому, второму и третьему выходам ключа, с первого по восьмой входы порогового узла являются соответственно с второго по девятый информационными входами ячейки памяти, группы управляющих входов всех ячеек памяти подключены к соответствующим выходам распределителя импульсов, вход сброса и тактовый вход которого подключены соответственно к входу сброса устройства и третьему выходу блока управления, первые информационные входы и вторые информационные выходы всех ячеек памяти подключены соответственно к информационному входу и информационному выходу матрицы памяти, входы записи и чтения которой подключены соответственно к входам записи и чтения всех ячеек памяти, адресные входы которых подключены к адресному входу матрицы памяти, второй информационный выход (,1)-й ячейки памяти (i 1.N. J 1,N) соединен со вторым информационным входом (И- j-1)-u ячейки памяти, третий информационный выход (I,J)- й ячейки памяти соединен с третьим информационным входом (1-1, JJ-й и четвертым информационным входом (I, j-tj-й ячеек памяти, четвертый информационный выход (1,))-й ячейки памяти соединен с пятым инсоединен с пятым информационным входом (И, +1)-й, шестым информационным входом (К +1)-й, с седьмым информационным входом (1+1, +1)-й. с восьмым информационным входом (1+1, j)-n и с девятым информационным входом (i+1, Н)-й ячеек памяти, один из выходов распределителя импульсов соединен с входом признака окончания фильтрации блока управления.

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем. что блок управления содержит два триггера и два элемента И. входы установки в О и в 1 первого триггера являются соответственно входом задания режима фильтрации и входом признака окончания

0

5

фильтрации блока, вход задания режима записи-чтения которого подключен к прямому входу первого элемента И, инверсный вход которого подключен к выходу первого триггера и первому входу второго элемента И. второй вход которого является входом синхронизации блока и подключен к входу синхронизации второго триггера, информационный вход, вход сброса, прямой и инверсный выходы которого подключены соответственно к выходу первого элемента И, входу сброса, первому и второму выходам блока, третий выход которого подключен к выходу второго элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Ассоциативная однородная обучаемая среда для распознавания объектов | 1983 |

|

SU1149287A1 |

| Устройство ассоциативного распознавания образов | 1985 |

|

SU1330644A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| Устройство для исследования цветового зрения | 1985 |

|

SU1261620A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ЦИФРОВЫХ СХЕМ | 1992 |

|

RU2042196C1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для компенсации различий в чувствительности элементов матрицы фотоприемников | 1987 |

|

SU1571793A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1996 |

|

RU2107955C1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в составе устройств обработки изображений. Цель изобретения - повышение быстродействия. Изобретение позволяет повысить быстродействие обработки информации .за счет уменьшения числа обращений к основной памяти. Для этого устройство содержит матрицу памяти, блок управления, распределитель импульсов, обеспечивающие считывание информации из ячеек памяти, которые в свою очередь состоят из порогового узла, управляющего состоянием элемента памяти в зависимости от состояния соседних ячеек памяти, ключа, обеспечивающего логику работы пороговых узлов. Это позволяет, в конечном счете, про- изво дить обработку информации непосредственно в матрице памяти. 1 з.п.ф-лы, 12 ил.

ll

h

Фиг.1

Фиг. 2

фигЬ

Фиг.5

гадл г

ТаблЗ

1815653

ТаблЛ

Та&л.З

Фиг.6

Я От ячейки 21(2-1)

32

27

75

33

12

Ъ

15

26 27 28

фиг.11

2J

Г5

75

Фиг.10

29

шиш

JO

Ml

J7

Фиг. 12

| Фостер К | |||

| Ассоциативные параллельные процессоры | |||

| М.: Энергоиздат, 1981 | |||

| Зарубежная радиоэлектроника, 1986, № 6, с.58-60. |

Авторы

Даты

1993-05-15—Публикация

1991-01-14—Подача