1

Изобретение относится к измерительной технике и может быть использовано VIЯ технологического контроля цифроана:1оговьгх преобразователей

(ЦАП).

Цель изобретения - повышение точности.

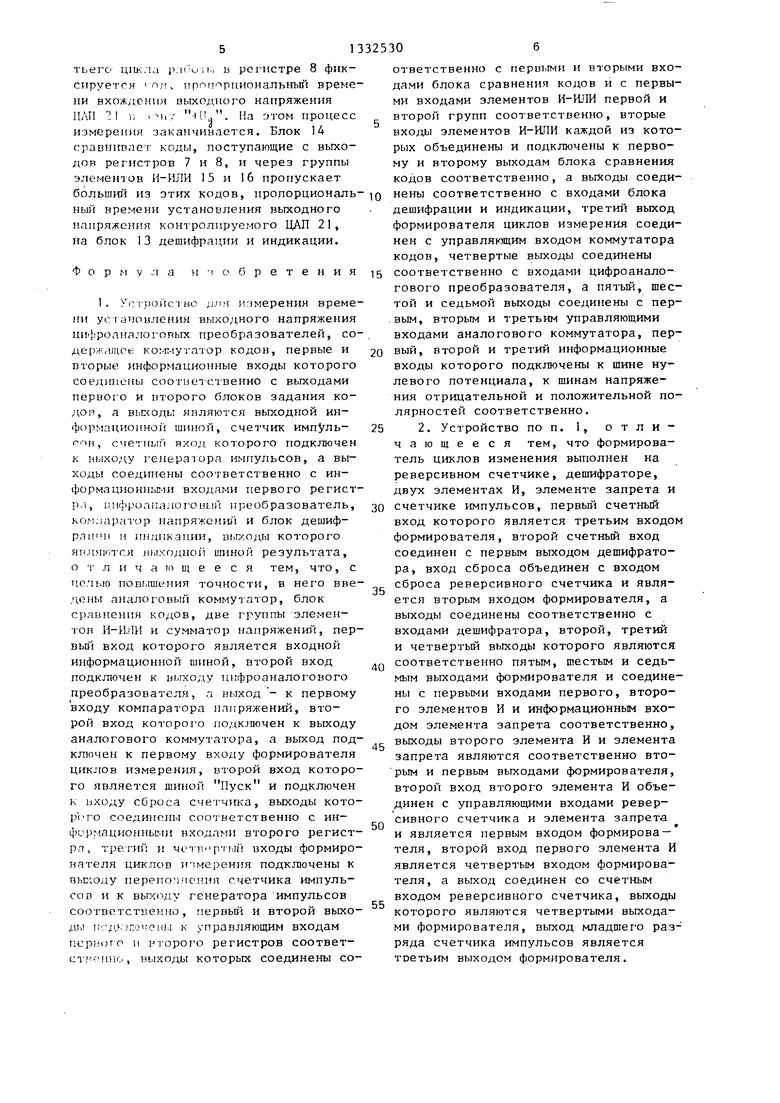

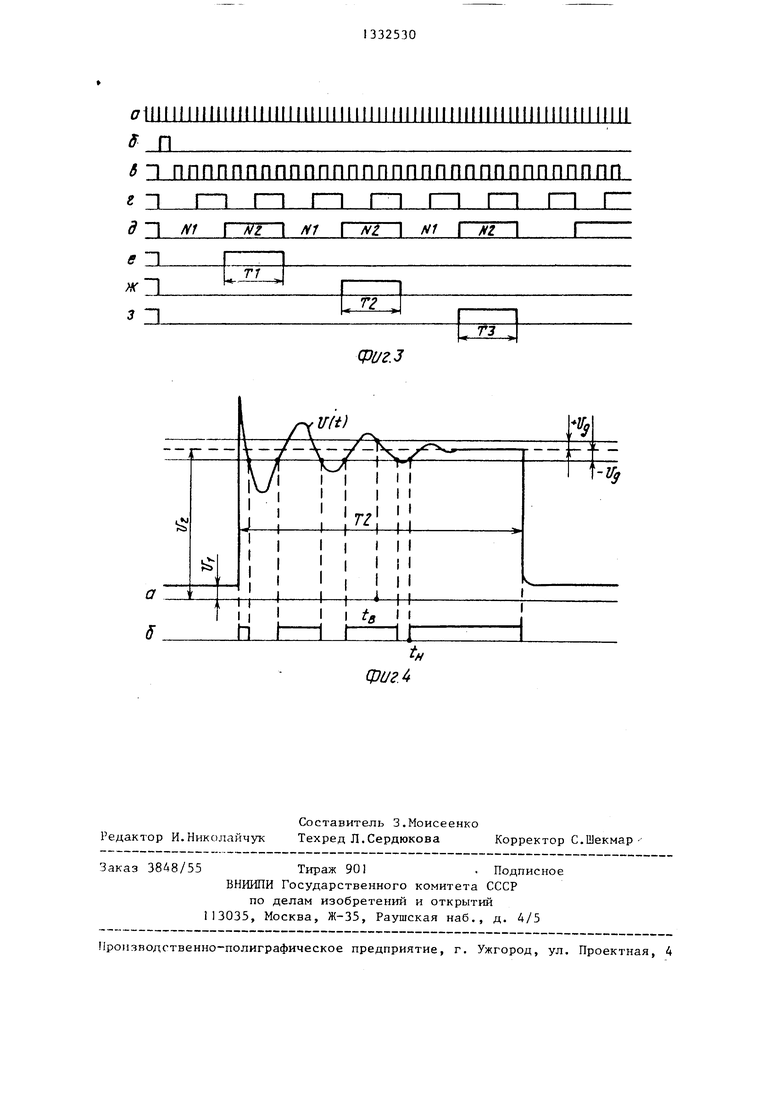

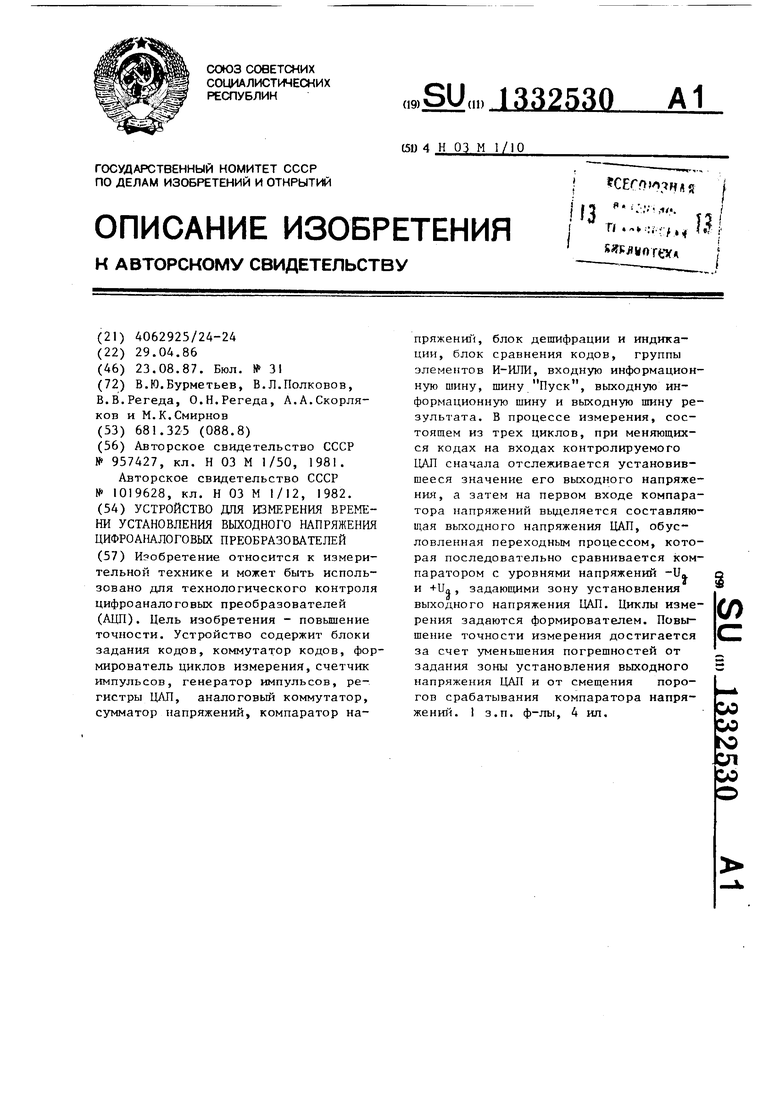

На фш . 1 приведена блок-схема устройства; на фиг. 2 - функциональная схема формирователя циклов измерения; на фиг. 3 и 4 - временные диаграммы работы устройства.

Устройство содержит блоки 1 и 2 задания кодов, коммутатор 3 кодов, формирователь А циклов измерения, счетчик 5 импульсов, генератор 6 импульсов, регистры 7 и 8, цифроанало- говый преобразователь 9, аналоговый коммутатор 10, сумматор 11 напряжений, компаратор 12 напряжений, блок 13 дешифрации и индикации, блок 1А сравнения кодов, группы 15 и 16 элементов И-ИЛИ, входную информационную шину 17, шину 18 Пуск, выходную информационную шину 19 и выходную шину 20 результата.

Устройство контролирует ЦЛП 21.

Формирователь 4 циклов измерения содержит счетчик 22 импульсов, дешиф ратор 23, реверсивный счетчик 24, элементы И 25 и 26 и элемент 28 запрета.

Устройство работает следующим образом.

Измерение состоит из трех циклов, которые условно показаны временными интервалами Т1, Т2 и ТЗ (фиг. 3 е, ж,з).

Перед началом измерения при помощи блоков 1 и 2 задания кодов, выполненных, например, в виде набора клавишных переключателей, число которых равно числу разрядов контролируемого ПДП 21, задаются два кода № 1 и № 2, при смене которых измеряется время установления выходного напряжения ЦАП 21. По сигналу Пуск (фиг. 36) счетчики 5, 22 и 24 устанавливаются в нулевое состояние. При этом по нулевому сигналу с выхода младшего разряда счетчика 22 ког-шутатор 3 подключает к входам контролируемого ЦАЛ код № 1 (фиг. Зд).

По окончании сигнала Пуск начи- пае-. С я заполнение счетчика 5 импуль- гами тактовой частоты с выхода генератора 6 (фиг. За). Период Т, импульсов тактовой частоты выбирается из

3325302

условия обеспечения требуемой разрешающей способности при измерении вре

5

0

5

0

5

0

мени установления, а емкость N счетчика импульсов 5 определяется из соотношения

М V -IlA i Jie- Т„

где - максимальное значение измеряемого времени установления.

При переполнении счетчика 5 его выходной импульс, воздействуя на счетный вход счетчика 22, изменяет его состояние на единицу. С этого момента начинается первый цикл измерения. По сигналу с выхода младшего разряда счетчика 22 коммутатор подключает к входу контролируемого ЦАП код N, сигнал с выхода 1 дешифратора через

0 аналоговый коммутатор 10 подключает к входу компаратора 12 шину ОВ нулевого потенциала и разрешает прохождение тактовых импульсов с выхода генератора 6 через элемент 25 на

5 счетный вход реверсивного счетчика 24, разрешая тем самым работу следящей замкнутой системе, включающей в себя сумматор 11 напряжений, компаратор 12 напряжений, реверсивный счетчик 24 и ЦАП 9.

В зависимости от состояния компаратора 12, определяемого отношением напряжений на выходе контролируемого ЦАП 21 и ЦАП 9, а также погрешностями сумматора 11 и компаратора 12, реверсивный счетчик 24 работает либо на сложение, либо на вычитание. Если напряжение на выходе ЦАП 9 меньше, чем на выходе ЦАП 21, то реверсивньш счетчик работает на сложение и его выходной код, воздействуя на входы ЦАП 9, увеличивает его выходное напряжение. В противном случае ревер- сивньй счетчик работает на вычитание и выходное напряжение ЦАП 9 уменьшается. При достижении равенства выходных напряжений ЦАП 9 и ЦАП 21 с учетом указанных погрешностей система переходит в автоколебательный режим, определяемый дискретностью обратной связи (ЦАП 9). Таким образом, в конце первого такта работы на выходе ЦАП 9 устанавливается напряжение

и,Ап и,П,(№)

ли + AUniuU n,

где ,, - установившееся значение напряжения на выходе ЦАП 21 при входном коде N2;

и

uUj., uU| - абсолютные погрешности преобразования соответственно сумматора напряжения и компаратора напряжения;

составляющая выходного напряжения ЦАП 9, отражающая автоколебательный процесс в установившемся режиме и рав- йая единице младшего значащего разряда (кванту) ЦАП 9.

Значение кванта легко сделать сколь угодно малым простым наращиванием разрядности иДЛ 9, поскольку он находится в цепи обратной связи и к нему не предъявляются высокие требования по линейности и долго-20 ет состояние выхода (фиг. 4б), при- временной стабильности, поэтому в дальнейшем эта составляющая выходного-напряжения ЦАП.9 ие рассматривается.

чем, если исследуемый сигнал входит в зону, сигнал на выходе компаратора -например, переходит из нулевого в единичное состояние. По этому перехо

Первый цикл измерения заканчивает- 25 ду осуществляется запись текущего

ся при следующем переполнении счетчика 5, выходной сигнал которого вновь сосчитывается счетчиком 22. При этом прекращается доступ импульсам тактовой частоты через элемент И 25 на вход реверсивного счетчика 24, фиксируя тем самьм в нем код обратной связи, пропорциональный установившемуся зиачению выходного напряжения коитролируемого ЦАП, к входам которого через коммутатор 3 подключается код № 1.

Второй цикл измерения начинается при очередном переполнении счетчика 5. Вновь на входе ЦАП 21 происходит смена кода N1 на N2, к входу компаратора 12 через аналоговый коммутатор 10 подключается шина -Uj и На выходе элемента И 26 формируется сигнал записи в регистр 7.

При смене входных кодов выходной сигнал контролируемого ЦАП также изменяет свое значение, причем это изменение сопровождается переходным процессом U(t), один из возможных вариантов которого приведен на фиг. 4а.

Выходное напряжение контролируемого ЦАП непрерывно в течение второго такта работы устройства сравнивается 55 с напряжением

г - &UK -Ufl Ua.

ицМуСкг)

ли.

332530

где

и - значение половины зоны установления выходного напряжения контролируемого ЦАП. g Из приведенного выражения видно, что зона установления выходного напряжения ЦАП задается относительно установившегося значения его выходного напряжения, измеренного в первом 10 такте, следовательно, в нем отсутствует составляющая погрешности, обусловленная неточным заданием зоны. Кроме того, наличие в выражении для и,, составляющих Д U,- и Д U свидетель- 15 ствует о компенсации этих составляющих погрешности во втором такте работы устройства.

В момент равенства напряжения U(t) и напряжения -U, компаратор 12 меняет состояние выхода (фиг. 4б), при-

чем, если исследуемый сигнал входит в зону, сигнал на выходе компаратора, -например, переходит из нулевого в единичное состояние. По этому перехо0

5

0

5

0

5

значения кода из счетчика 5 в регистр 7 при каждом вхождении исследуемого сигнала в зону установившегося значения. Поскольку смена кода N1 и N2 происходит при переполнении счетчика 5, то последний в момент подачи кода N2 на вход ЦАП 21 находится в нулевом состоянии. Следовательно, во втором такте Т. в счетчике 5 фиксируется код текущего времени с момента начала этого такта, а в регистр 7 при каждом срабатывании компаратора напряжения Ьереписьшается код, пропорциональный интервалу времени с момента подачи кода N2 на вход контролируемого ЦАП до момента вхождения исследуемого сигнала в зону установившегося значения. В момент t (фиг.46) компаратор 12 срабатывает последний раз и в регистре 7 записывается код, пропорциональный времени вхождения выходного напряжения ЦАП 21 в зону

LQ .

Третий цикл измерения протекает аналогично второму, однако к входу компаратора 12 напряжений через коммутатор 10 подключается шина 19 , а на выходе элемента 27 запрета формируется сигнал записи текущего времени из счетчика 5 в регистр 8, Элемент запрета использован для того, чтобы запись кода производилась по нулевому перепаду выходного напряжения компаратора 12. По истечении тре51

тьего цикла p.,, в регистре 8 фиксируется irijT, проп трциональный време ни вхождения выходного напряжения НЛП 21 ,; ,-1,7 -П.. На этом нроцесс измерения заканчинается. Блок 14 сравнивает коды, поступающие с выходов регистров 7 и 8, и через группы элементов И-ИЛИ 15 и б пропускает больши из этих КОДОВ, пропорциональ ный времени установления выходного напряжения контролируемого ЦАП 21, па блок 13 дешифрации и индикации.

Форму ,;i а и ч о б р е т е и и я

1 . Ус rj) ;jji,4 игзмерения време ни усгачовления выходного напряжения ци фоаналогопьгх преобразователей, со держсидск ко:-я- угатор кодов, первые и вторые информационные входы которого соедш1сны соотиетственно с выходами первого и второго блоков задания ко- доп, а вькоды являются выходной ин- форм 1циопно11 шиной, счетчик импУль- гон, счетный нход которого подключен к ныходу генераюра ю-тульсов, а выходы соединены соответственно с ин- 11)Ормацион}1ь&1И входами первого регист Г), 1, 1:и(Ьроапалогоц,1Й преобразователь, компаратор напряжени; И блок дешиф- рпцчп и индикагиш, которого яnлмlrJтcя кыходно/ ип1ной результата, о т л и ч а 10 щ е е с я тем, что, с тюлыо повышения точности, в него вве ,чены аналоговый коммутатор, блок сравнения кодов, две группы элементов Н-ИЛИ и сумматор напряженки, пер- вьй вход которого является входной информационной шиной, второй вход подключен к выходу цифроаналогового преобразователя, а выход - к первому входу компаратора папряжений, второй вход которого подключен к выходу аналогового коммутатора, а выход под- ключе к первому входу формирователя циклов измерения, второй вход которого является шиной Пуск и подключен к входу сброса сче-1 Ч1жа, выходы кото- pV.ro соединены соответственно с ин- фирмационны .1И входами второго регистра, третий и че гп р Г111Й входы формирователя циклов ичме)эения подключены к вьс .оду переполнения счетчика импульсов и к генератора импульсов соответственно, первый и второй выходы П Г/ .ьJf:oi;(i(;i к управляющим входам iicpiiOTO и рторого регистров соответ- , выходы которых соединены со

325306

ответственно с первыми и вторыми входами блока сравнения кодов и с первыми входами элементов И-ИЛИ первой и второй групп соответственно, вторые входы элементов И-ИЛИ каждой из которых объединены и подключены к первому и второму выходам блока сравнения кодов соответственно, а выходы соеди- 10 йены соответственно с входами блока дешифрации и индикации, третий выход формирователя циклов измерения соединен с управляющим входом коммутатора кодов, четвертые выходы соединены

15 соответственно с входами цифроаналогового преобразователя, а пятый, щес- той и седьмой выходы соединены с пер- .вым, вторым и третьим управляющими входами аналогового коммутатора, пер20 вый, второй и третий информационные входы которого подключены к шине нулевого потенциала, к шинам напряжения отрицательной и положительной полярностей соответственно.

25 2. Устройство по п. 1, отличающееся тем, что формирователь циклов изменения выполнен на реверсивном счетчике, дешифраторе, двух элементах И, элементе запрета и

30 счетчике импульсов, первый счетный вход которого является третьим входом формирователя, второй счетный вход соединен с первым выходом дешифратора, вход сброса объединен с входом сброса реверсивного счетчика и является вторым входом формирователя, а выходы соединены соответственно с входами дешифратора, второй, третий и четвертый выходы которого являются

д соответственно пятым, шестым и седьмым выходами формирователя и соединены с первыми входами первого, второго элементов И и информационным входом элемента запрета соответственно, выходы второго элемента И и элемента запрета являются соответственно вторым и первым выходами формирователя, второй вход второго элемента И объединен с управляющими входами реверсивного счетчика и элемента запрета и является первым входом формирователя, второй вход первого элемента И является четвертым входом формирователя, а выход соединен со счетным входом реверсивного счетчика, выходы которого являются четвертыми выходами формирователя, выход младшего раз- ряда счетчика импульсов является тоетьим выходом формирователя.

35

45

50

55

CPU г. г

gllilHliiliHIIIIHiHilllllllillinilllllllinillililllillllllilll

D

6 ППППППППППППППППППППППППППППППП

г I I-I

(Pi/г.з

Редактор H.HHKOjiapiqyK

Составитель З.Моисеенко

Техред Л.Сердюкова Корректор С.Шекмар

Заказ 3848/55

Тираж . Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фиг4

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель характеристик аналого-цифровых преобразователей | 1985 |

|

SU1282324A1 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1990 |

|

SU1716601A2 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Устройство для измерения времени установления цифроаналогового преобразователя | 1986 |

|

SU1432776A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Измеритель мощности переменного тока | 1980 |

|

SU883764A1 |

| Устройство для контроля аналого-цифрового преобразователя | 1986 |

|

SU1585897A1 |

| Устройство контроля цифро-аналоговых преобразователей | 1980 |

|

SU949801A1 |

| Устройство для измерения времени установления цифроаналоговых преобразователей | 1984 |

|

SU1223366A1 |

| Следящий преобразователь угла поворота вала в код | 1983 |

|

SU1116446A1 |

Изобретение относится к измерительной технике и может быть использовано для технологического контроля цифроаналоговых преобразователей (АЦП). Цель изобретения - повышение точности. Устройство содержит блоки задания кодов, коммутатор кодов, формирователь циклов измерения, счетчик импульсов, генератор импульсов, регистры ЦАП, аналоговый коммутатор, сумматор напряжений, компаратор напряжени, блок дешифрации и индикации, блок сравнения кодов, группы элементов И-ИЛИ, входную информационную шину, шину Пуск, выходную информационную шину и выходную шину результата. В процессе измерения, состоящем из трех циклов, при меняющихся кодах на входах контролируемого ЦАП сначала отслеживается установившееся значение его выходного напряжения, а затем на первом входе компаратора напряжений выделяется составляющая выходного напряжения ЦАП, обусловленная переходным процессом, которая последовательно сравнивается компаратором с уровнями напряжений -U и +Ua, задающими зону установления выходного напряжения ЦАП. Циклы измерения задаются формирователем. Повышение точности измерения достигается за счет уменьшения погрешностей от задания зоны установления выходного напряжения ЦАП и от смещения порогов срабатывания компаратора напряжений. 1 з.п. ф-лы, 4 ил. (Л

Авторы

Даты

1987-08-23—Публикация

1986-04-29—Подача