(54) УСТРОЙСТВО КОНТРОЛЯ ЦИФРОАНАЛОГОВЫХ ПРЕОБРАЗОВАТЕЛЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель нелинейности цифро-аналоговых преобразователей | 1983 |

|

SU1112547A1 |

| Устройство для контроля электрических параметров полупроводниковых диодов | 1983 |

|

SU1138768A1 |

| Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления | 1987 |

|

SU1494216A1 |

| Аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1667246A1 |

| Лазерное устройство для контроля непараллельности | 1987 |

|

SU1682777A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Способ измерения нелинейности цифроаналогового преобразователя и устройство для его осуществления | 1987 |

|

SU1631723A1 |

| Устройство для измерения времени установления цифроаналогового преобразователя | 1986 |

|

SU1432776A1 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1990 |

|

SU1716601A2 |

Изобретение относится к измерительной технике и может быть использовано для измерения дифференциальной нелинейности цифроаналоговых преобразователей (ЦАП).

Известно устройство для измерения погрешности цифроаналогового преобразователя, содержащее задающий генератор, два счетчика, контролируемый и эталонный цифроаналоговые преобразователи, блок сравнения кодов, элемент вычитания и усиления, аналоговое запоминающее устройство и индикатор 1 .

Недостатком известного устройства является большое время измерения, обусловленное большим числом циклов измерения.

Наиболее близким к предлагаемому по технической сущности является устройство контроля цифроаналоговых преобразователей, содерх ащее два формирователя кодов, контролируемый и эталонный цифроаналоговые преобразователи, измерительный прибор и дифференциальный усилитель, первый вход которого соединен с выходом контролируемого цифроаналогового преобразователя, выход дифференциального усилителя подключен к входу

измерительного прибора, выход первого формирователя кодов соединен с входом контролируемого цифроаналогового преобразователя, выход второго формирователя кодов подключен к входу эталонного цифроаналогового преобразователя 2.

Недостатками данного устройства являются большое время измерения и

10 невысокая точность контроля.

Большое время измерения обусловлено тем, что для определения дифференциальной нелинейности Дд„ контролируемого ЦАП с помощью данного

15 устройства нeoбxoди ю приборам измерить значение ) для всех 2 значений входного кода (в случае п разрядного ЦАП) и выбрать максимальное из них, которое и будет искомой

20 характеристикой ЦАП.

Низкая точность измерения обусловлена тем, что при контроле, вследствие наличия таких погрешностей конт25ролируемого ЦАП, как смещение нуля, погрешности усиления,интегральной нелинейности, выходные сигналы эталонного YO (N-1) и контролируемого YX(N-I) при коде (N-1) не равны друг

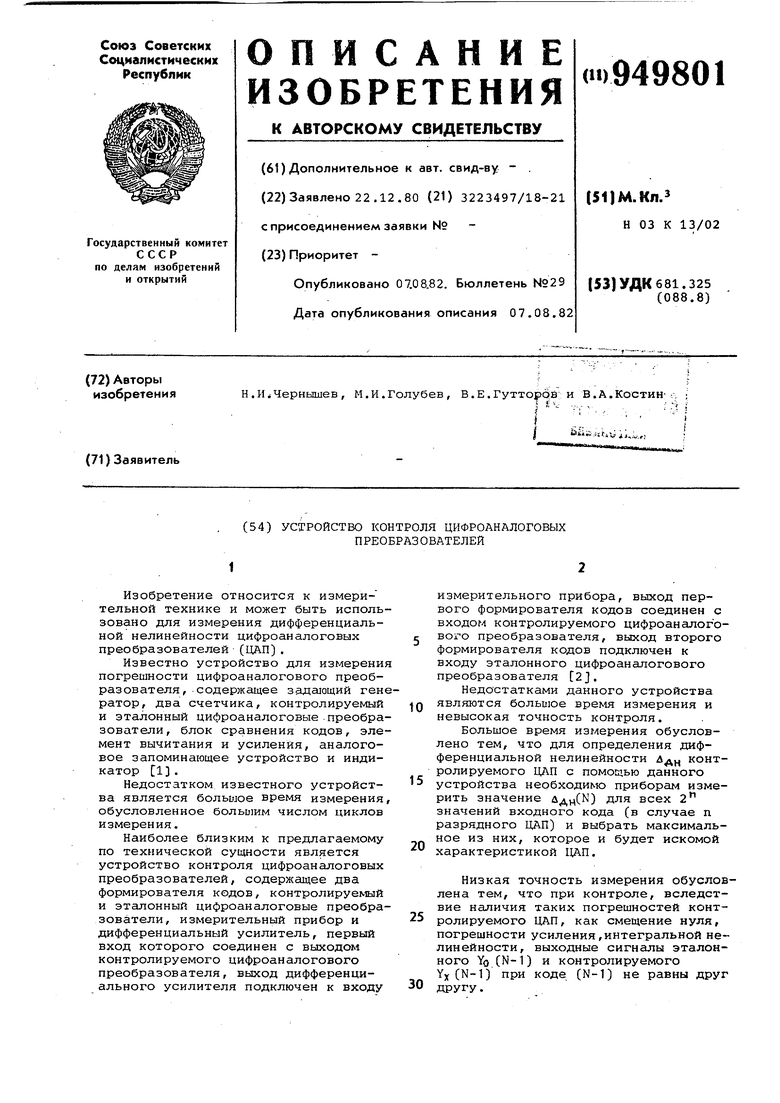

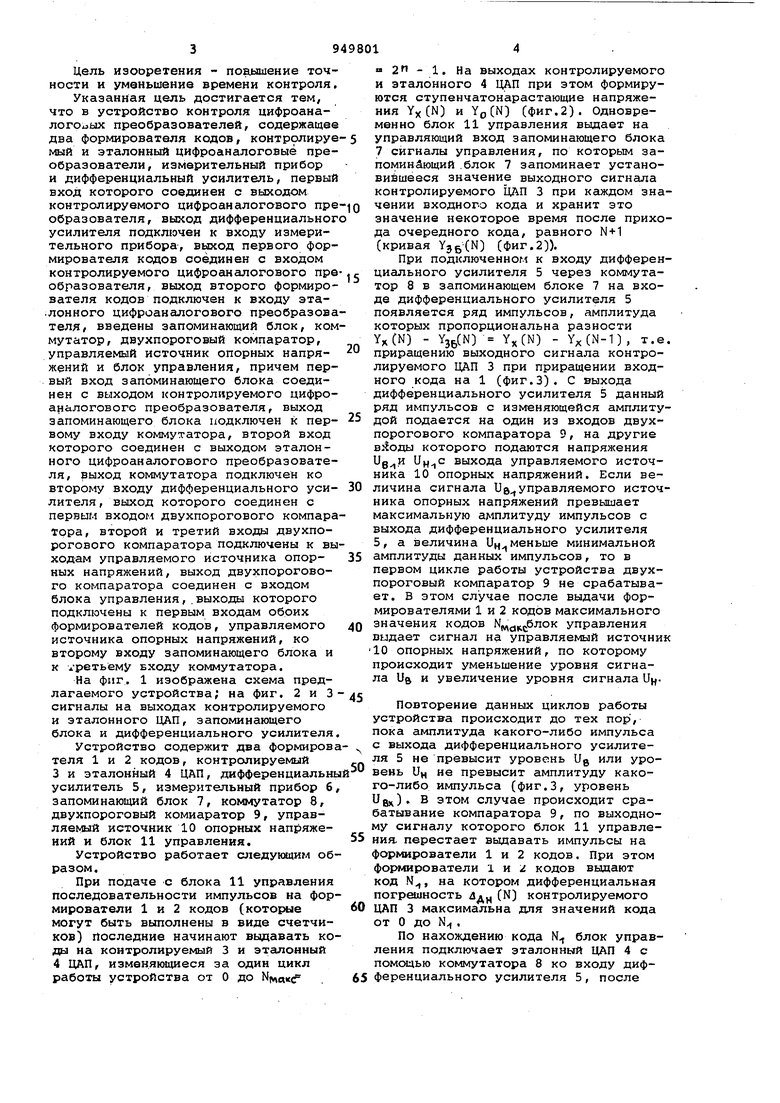

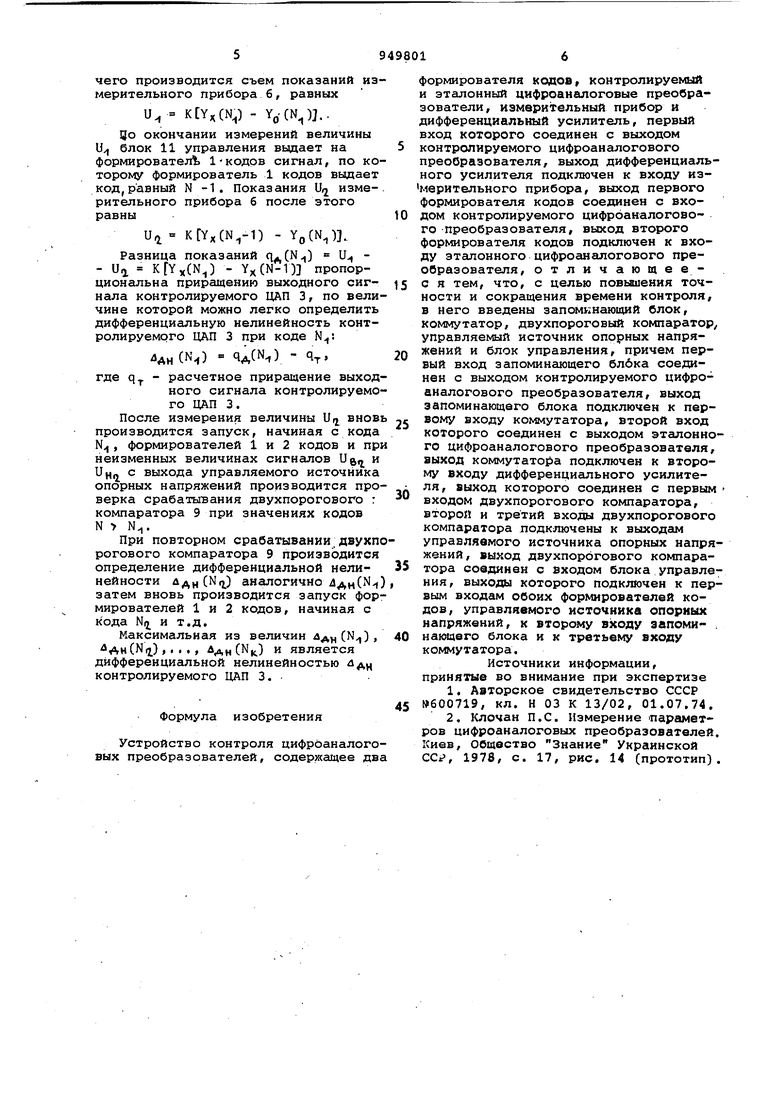

30 другу. Цель иэооретения - повышение точности и уменьшение времени контроля, Указанная цель достигается тем, что в устройство контроля цифроаналого ых преобразователей, содержащее два формирователя кодов, контролируе мый и эталонный цифроаналоговые преобразователи, измерительный прибор и дифференциальный усилитель, первый вход которого соединен с выходом контролируемого цифроаналогового пре образователя, выход дифференциальног усилителя подключен к входу измерительного прибора, выход первого формирователя кодов соединен с входом контролируемого цифроаналогового пре образователя, выход второго формирователя кодов подключен к входу эта.лонного цифроаналогового преобразова теля, введены запоминающий блок, ком мутатор, двухпороговый компаратор, управляемый источник опорных напря жений и блок управления, причем первый вход запоминающего блока соединен с выходом контролируемого цифроаналогового преобразователя, выход запоминающего блока подключен к первому входу коммутатора, второй вход которого соединен с выходом эталонного цифроаналогового преобразователя, рыход коммутатора подключен ко второму входу дифференциального усилителя, выход которого соединен с первым входом двухпорогового компара тора, второй и третий входы двухпорогового компаратора подключены к вы ходам управляемого источника опорных напряжений, выход двухпорогового компаратора соединен с входом блока управления,.выходы которого подключены к первым входам обоих формирователей кодов, управляемого источника опорных напряжений, ко второму входу запоминающего блока и к третьему входу коммутатора. На фиг. 1 изображена схема предлагаемого устройства; на фиг. 2 и 3 сигналы на выходах контролируемого и эталонного ЦАП, запоминающего блока и дифференциального усилителя Устройство содержит два формирова теля 1 и 2 кодов, контролируемый 3и эталонный 4 ЦАП, дифференциальны усилитель 5, измерительный прибор 6 запоминающий блок 7, коммутатор 8, двухпороговый комиаратор 9, управляемый источник 10 опорных напряжений и блок 11 управления. Устройство работает следующим образом. При подаче с блока 11 управления последовательности импульсов на формирователи 1 и 2 кодов (которые могут быть выполнены в виде счетчиков) последние начинают выдавать коды на контролируемый 3 и эталонный 4ЦАП, изменяющиеся за один цикл работы устройства от О до Niy, 2 - 1. На выходах контролируемого и эталонного 4 ЦАП при этом формируются ступенчатонарастающие напряжения YX(N) и Y(,N) (фиг.2). Одновременно блок 11 управления выдает на управляющий вход запоминающего блока 7 сигналы управления, по которым запоминающий .блок 7 запоминает установившееся значение выходного сигнала контролируемого ЦАП 3 при каждом значении входного кода и хранит это значение некоторое время после прихода очередного кода, равного (кривая Y3g-(N) (фиг.2)). При подключенном к входу дифференциального усилителя 5 через коммутатор 8 в запоминающем блоке 7 на входе дифференциального усилителя 5 появляется ряд импульсов, амплитуда которых пропорциональна разности Yx(N) - Y36(N) Y(N) - Y;,(N-1), т.е. приращению выходного сигнала контролируемого ЦАП 3 при приращении входного кода на 1 (фиг.З). С выхода дифференциального усилителя 5 данный ряд импульсов с изменяющейся амплитудой подается на один из входов двухпорогового компаратора 9, на другие которого подаются напряжения Ug.H выхода управляемого источника 10 опорных напряжений. Если величина сигнала Ue управляемого источника опорных напряжений превышает максимальную амплитуду импульсов с выхода дифференциального усилителя 5, а величина U меньше минимальной амплитуды данных импульсов, то в первом цикле работы устройства двухпороговый компаратор 9 не срабатывает. В этом случае после выдачи формирователями 1 и 2 кодов максимального значения кодов управления видает сигнал на управляемый источник 10 опорных напряжений, по которому происходит уменьшение уровня сигнала Uft и увеличение уровня сигнала Uj. Повторение данных циклов работы устройства происходит до тех пор , пока амплитуда какого-либо импульса с выхода дифференциального усилителя 5 не превысит уровень Ug или уровень UH не превысит амплитуду какого-либо импульса (фиг.З, уровень UB). В этом случае происходит срабатывание компаратора 9, по выходному сигналу которого блок 11 управления, перестает вьвдавать импульсы на формирователи 1 и 2 кодов. При этом формирователи ц. и ; кодов выдают код N, на котором дифференциальная погрешность Лд (N) контролируемого ЦАП 3 максимальна для значений кода от О до N t По нахождению кода N блок управления подключает эталонный ЦАП 4 с помсядью кo Флyтaтopa 8 ко входу дифференциального усилителя 5, после чего производится съем показаний измерительного прибора б, равных и (N) - YO-(N).. Qo окончании измерений величины и блок 11 управления на формирователе. 1-кодов сигнал, по которому формирователь 1 кодов выдает код, равный N -1. Показания U,j измерительного прибора б после этого равны и KrY,() - YO(N,). Разница показаний q..CN) U - Ui KfYyCN) - YX(N-I) пропорциональна приращению выходного сигнала контролируемого ЦАП 3, по величине которой можно легко определить дифференциальную нелинейность контролируемого ЦАП 3 при коде ЛднС) qACN,) - Ят., где q. - расчетное приращение выходного сигнала контролируемого ЦАП 3. После измерения величины и, вновь производится запуск, начиная с кода N, формирователей 1 и 2 кодов и при неизменных величинах сигналов Ug,j, и иц„ с выхода управляемого источника опорных напряжений производится проверка срабатывания двухпорогового : компаратора 9 при значениях кодов N N. При повторном срабатывании,двухпо рогового компаратора 9 производится определение дифференциальной нелинейности ) аналогично Лдн(() затем вновь производится запуск формирователей 1 и 2 кодов, начиная с кода Nrj и т.д. Максимальная из величин Лд (N), AHCNi) , . . . , Ддн ) и является дифференциальной нелинейностью Лдц контролируемого ЦАП 3. . Формула изобретения Устройство контроля цифрЬаналоговых преобразователей, содержащее два формирователя кодов, контролируемый и эталонный цифроанапоговые преобразователи, измерительный прибор и дифференциальный усилитель, первый вход которого соединен с выходом контролируемого цифроаналогового преобразователя, выход дифференциального усилителя подключен к входу измерительного прибора, выход первого формирователя кодов соединен с входом контролируемого цифроаналогового преобразователя, выход второго формирователя кодов подключен к входу эталонного цифроаналогового преобразователя, отличающеес я тем, что, с целью повьпиения точности и сокращения времени контроля, в него введены запоминающий блок, коммутатор, двухпороговый компаратор, управляемый источник опорных напряжений и блок управления, причем первый вход запоминающего блбка соединен с выходом контролируемого цифроаналогового преобразователя, выход запоминающего блока подключен к первому входу коммутатора, второй вход которого соединен с выходом эталонного цифроаналогового преобразователя, выход коммутатора подключен к второму входу дифференциального усилителя, выход которого соединен с перВЕлм входом двухпорогового компаратора, втором и третий входы двухпорогового компаратора подключены к выходам управляемого источника опорных напряжений, выход двухпорогового компаратора соединен с входом блока управления, выходы которого подключен к первым входам Обоих формирователей кодов, управляемого источника опорных напряжений, к второму входу эапоми- . наюивго блока и к третьему входу коммутатора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №600719, кл. Н 03 К 13/02, 01.07.74. 2.Клочан П.С. Измерение параметров цифроаналоговых преобразователей. Киев, Общество Знание Украинской CCi, 1978, с. 17, рис, 14 (прототип).

иг

-

.

4 J

I I I I

1 I

.J

УаИ

YwW

Авторы

Даты

1982-08-07—Публикация

1980-12-22—Подача