(54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1988 |

|

SU1589414A2 |

| Устройство тактовой синхронизации | 1975 |

|

SU570210A1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ С НЕПРЕРЫВНОЙ ФАЗОЙ | 2006 |

|

RU2323536C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| Устройство тактовой синхронизации | 1988 |

|

SU1614122A2 |

| Устройство автоподстройки несущей частоты | 1984 |

|

SU1298946A1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2008 |

|

RU2374776C2 |

1

Изобретение относится к технике связи и может быть использовано в многоканальных системах радиосвязи, телеметрии, передачи данных.

Известно устройство по основному авт. св. № 570210, содержащее два квадратурных канала, дифференцирующий блок, блок управления, генератор тактовых импульсов, делитель частоты, дещифратор, эле менты задержки, перемножители, сумматоры 1.

Однако помехоустойчивость синхронизации такого устройства невелика.

Цель изобретения - повышение помехоустойчивости синхронизации.

Для достижения цели в устройство тактовой синхронизации содержащее два квадратурных канала, дифференцирующий блок, блок управления, генератор тактовых импульсов, делитель частоты, дешифратор, элементы задержки, перемножители, сумматоры, введены два канала, каждый из которых состоит из последовательно соединенных перемножителя и интегратора, а также два блока задержки и два блока вычитания, при этом выходы интеграторов обоих каналов подключены к входам первого блока

вычитания, выход которого подключен непосредственно и через блок задержки к входам второго блока вычитания, выход которого подключен к дополнительному входу блока управления, причем первый вход первого перемножителя, два входа второго перемножителя и вход второго блока задержки объединены со входом квадратурных каналов, а выход второго блока задержки подключен к второму входу перемножителя одного из каналов, при этом вторые входы интеграторов обоих каналов соединены с

10 выходом дешифратора.

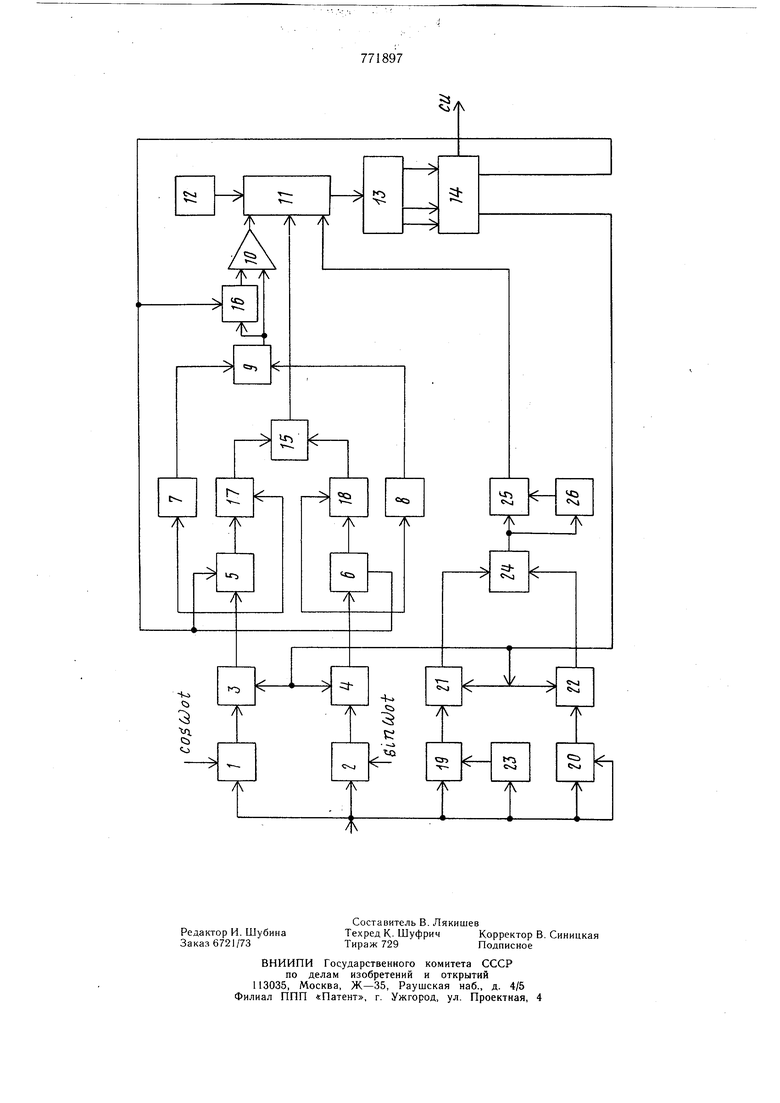

На чертеже представлена структурная электрическая схема описываемого устройства.

Данное устройство тактовой синхрониза15ции содержит два квадратурных канала, каждый из которых состоит из последовательно соединенных перемножителя 1 (2) и интеграторов 3(4). выход кото{)0) по;;к.-1ючен к входу элемента 5 (6) заде|.-;.к . и киа.л 20 ратора 7 (В) выход которого пол.ключен к соответствующему входу сумматора 9. выход которого через последовательк( соединенные диффере} цирующ1 й блок li.i. блок 1 управления, ко второму в.х(:, которош подключен выход генератора 12 тактовых импульсов, делитель 13 частоты и дешифратор 14 подключен соответственно к управляющим входам элементов 5, 6 задержки и интеграторов 3, 4, а также вспомогательный сумматор 15, выход которого подключен к третьему входу блока 11 управления, дополнительный элемент 16 задержки, в каждом квадратурном канале - дополнительный перемножитель 17(18), два канала, каждый из которых состоит из последовательно соединенных перемножителя 19(20) и интегратора 21(22), второй блок 23 задержки, первый и второй блоки 24, 25 вычитания и первый блок 26 задержки. В каждом квадратурном канале дополнительный перемножитель 17(18) включен между выходами соответственно интегратора 3 (4) и элемента 5 (6) задержки и соответствующими входами вспомогательного сумматора 15, а дополнительный элемент задержки .16 - между выходом сумматора 9 и вторым входом дифференцирующего блока 10. К управляющему входу дополнительного элемента 16 задержки подключен соответствующий выход дешифратора 14. Устройство тактовой синхронизации работает следующим образом. На первые входы перемножителей 1 и 2, на оба входа перемножителя 20 и на входы перемножителя 19, на первый вход непосредственно, а на второй - через блок 23 задержки, с величиной задержки равной одному (нескольким) периоду высокочастотного колебания частотой из канала поступает п-я посылка сигнала, состоящая из N ортогональных на интервале колебаний: )--| q cosCaJ,-t,- пг«ъ tni-i)r, где - длительность посылки сигнала; - амплитуда ортогональных переносчиков;i J --2-1-частота ортогональных переносчиков;Мд п-значение начальной фазы i-ro ортогонального переносчика сигналов относительной фазовой манипуляции. С интеграторов 3 и 4 по сигналу с выхода дешифратора 14 в моменты времени ( снимаются отсчеты постоянного пропорционального проекциям i-ой составляющей п-ой посылки сигналаза интервал интегрирования которые равны соответствен иn I . у%3. S (Псоащ. cU-- ц-тЧ) im J S itQ-c i,n )sinuU;tdtj-tdt-- -cos4,- п-с.т ц + 2.Т -2п J QoTc С помощью квадраторов 7 и 8 и сумматора 9 вычисляются квадраты модулей векторов посылок за каждый интервал интегрирования вида А - v2- . -i-z а§Т 4iH- ,2П На выходе дифференцирующего блока 10 формируется сигнал рассогласования по фазе импульсов тактовой синхронизации, равный разности модулей v4 2n- -iVin вектора посылки за интервал интегрирования nr - -T-tiC -i-2T И задержанного элементом 16 задержки на /2модуля Д„ и --А -А 10 ,2П приТ-Т -Т система находится в синхронизме (Up 0); Ai 0. Одновременно с выходов интеграторов 3 и 4 напряжениеХ;„„иУ.- „„ непосредственно, .,.,ajzn i X П .-л а Х., И через элементы 5 и о задержки поступает на перемножители 17 и 18 соответственно на выходах которых напряжения соответственно равны: Ц,-.-1р.оз.,,„, 1 1. . 9 Ll e--T- ™ f,,n На выходе сумматора 15 напряжение в этом случае равно i5- i- u eПри расстройках фазы/дС/ -2-напряжение на выходе сумматора 15 имеет положительный знак. Поступая на второй вход блока 11 управления, сигнал U. не изменяет величи .. „ ну и знак управляющего сигнала ,.-,.8 этом случае сигнал рассогласования начальных фаз формируется как %-и,4 При расстройках фазы - /ut:/ на пряжение на выходе сумматора 15 имеет отрицательный знак. Поступая на второй вход блока 11 управления отрицательный сигнал формирует управляющее фазой тактовых импульсов напряжение, равное |24о(т-)-и,о |2Цо(-|-УЩо Р и, В то же время с помощью перемножителей 19, 20, блока 23 задержки с постоянной памяти Т , равной времени существования периода частоты ортогонального переносчика, интеграторов 21, 22 и блока 24 вычитания на длительности каждой полупосылки вычисляется величина разности энергий, равная М-Гц-ьТ, ,-- J sJ(-b)dt-J s(t)Sj,(t-r,)dt, ITCnпГп и соответствующая разности значений корреляционных функций RC-t: 0)-R(C-t; ) На выходе блока 25 вычитания из величин с помощью блока 26 задержки, постоянная времени задержки которого равна , формируется величина приращений разностей энергий Q соседних полупосылок. характеризующая степень флуктуации параметров сигналов на длительности каждой посылки. В случае когда параметры сигналов а о, Ф . , не подвержены флуктуациям и уст1эойство находится в синхронизме, величины разности полупосылки к посылке будут оставаться равными О, что позволит получить на дополнительном запрещающем входе блока 11 управления величину и незначительно отличающуюся от нуля, если устройство не вощло в синхронизм дТЧ1 так как малая величина по сравнению с , что позволит по величине и знаку напряжения Up блоку 11 управления изменить фазу генератора 12 тактовых импульсов на величину лС . При синхронизме устройства флуктуации любого из параметров сигнала g j.(t} приводят к изменению величин ,А и и соответственнои А -А -д/0,чт6 должно через блок 11 управления вызвать изменение фазы генератора 12 тактовых импульсов и вывести устройство из синхронизации. Однако флуктуации параметров приводят к тому, что на дополнительный запрещающий вход блока 11 управления с выхода блока 25 вычитания поступает величина приращения разности энергий полупосылокв -Д -,,0, так как коррелятор, включающий в себя перемножитель 20 и интегратор 22, вычисляет энергию без учета влияния фазовых и частотных флуртуаций, в то времь, как коррелятор, включающий в себя перемножитель 19, блок 23 задержки и интегратор 21, вычисляет энергию с учетом этих флуктуации. Величина 6, Ослужит запрещающей блоку 11 управления на изменение фазы генератора тактовых импульсов и сохраняет синхронизм устройства, повыщая таким образом устойчивость синхронизации при флуктуации параметров сигнала. Формула изобретения Устройство тактовой синхронизации по авт. св. 570210, отличающееся тем, что, с целью повыщения помехоустойчивости синхронизации, в него введены два канала, каждый из которых состоит из последовательно соединенных перемножителя и интегратора, а также два блока задержки и два блока вычитания, при этом выходы интеграторов обоих каналов подключены к входам первого блока вычитания, выход которого подключен непосредственно и через блок задержки к входам второго блока вычитания выход которого подключен к дополнительному входу блока управления, причем первый вход первого перемножителя, два входа второго перемножителя и вход второго блока задержки объединены со входом квадратурных каналов, а выход второго блока задержки подключен к второму входу перемножителя одного из каналов, при этом вторые входы интеграторов обоих каналов соединены с выходом дешифратора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 570210, кл. Н 04 L 7/04 1975.

Авторы

Даты

1980-10-15—Публикация

1978-06-23—Подача