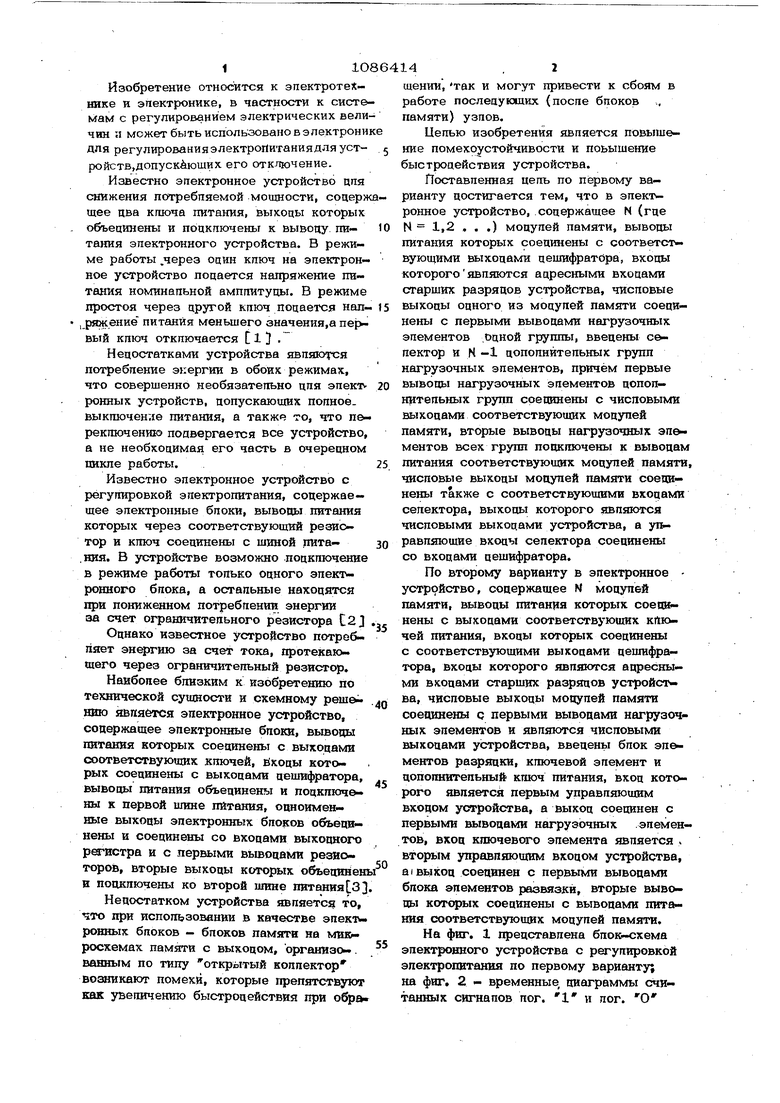

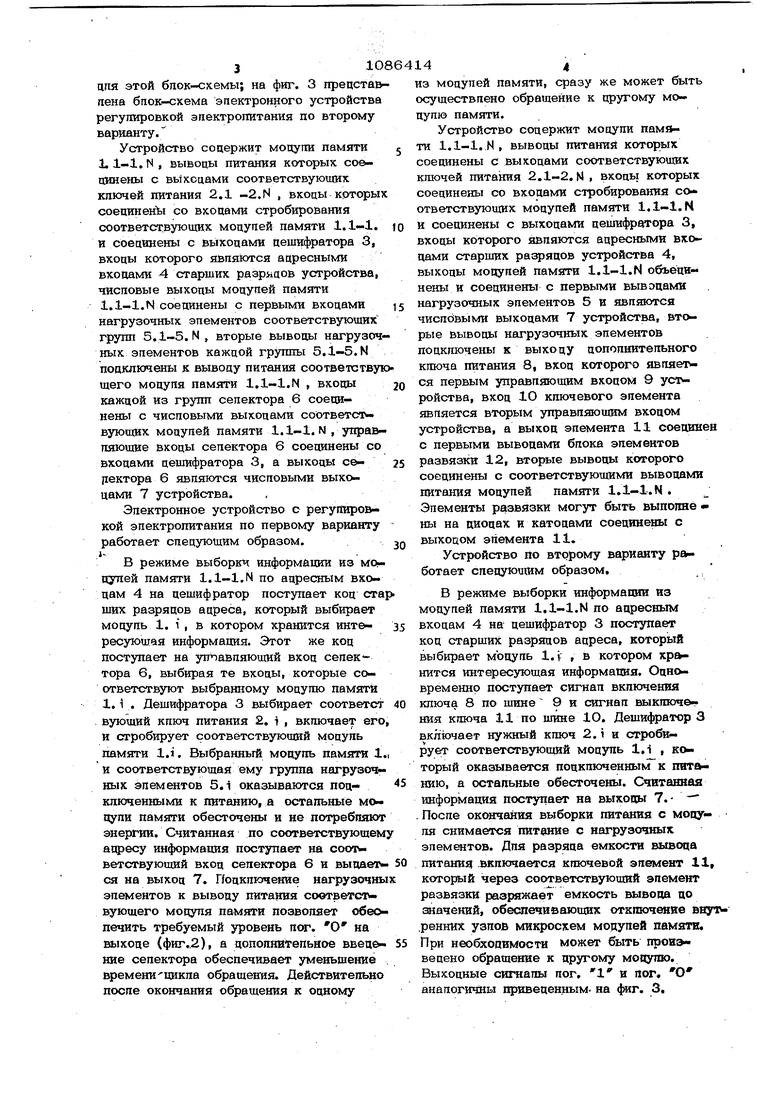

Изобретение относится к эпектротехнике и электронике, в частности к систе мам с регулированием электрических вели чин н может быть использовано в электрони для регулирования электропитания для устройств,допускйюших его отключение. Известно эпектронное устройство цпя снижения потребляемой мощности, содерж щее два кпюча питания, выходы которых объединены и подключены к выводу пи- тания электронного устройства. В режиме работы .через один ключ на электронное устройство подается напряжение питания номинальной амплитуды. В режиме простоя через другой ключ подается напI ряжение питания меньшего значения,а первый ключ отключается С1 3 . Недостатками устройства являются потребление энергии в обоих режимах, что совершенно необязательно для элект ровных устройств, допускающих полное. выключенле питания, а также то, что переключению подвергается все устройство, а не необходимая его часть в очередном пикле работы. Известно электронное устройство с регулировкой электропитания, соцержаещее электронные блоки, выводы питания которых через соответствующий резистор и ктпоч соединены с шиной пита- .ПИЯ. В устройстве возможно подключение в режиме работы только одного элекпронноюч) блока, а остальные находятся при пониженном потреблении энергии за счет ограничительного резистора t2J Однако известное устройство потребляет за счет тока, протекающего через ограничительный резистор. Наиболее близким к изобретению по технической сущности и схемному реша нию является эпектронное устройство, содержащее электронные блоки, выводы питания которых соединены с выходами соответствующих ключей, ёходы которых соединены с выходами дешифратора, выводы питания объединены и подключены к первой шине питания, оцноименные выходы электронных блоков обьедвнены и соединены со входами выходного регистра и с первыми выводами резисторов, вторые выходы которых объединен и подключены ко второй шине питания 33 Недостатком устройства является то, что при использовании в качестве эпектронных блоков - блоков пам51тн на мик росхемах памяти с выходом, организо-. ванным по типу открытый коллектор возникают помехи, которые препятствуют как увеличению быстродействия при обр щении, так и могут привести к сбоям в работе последующих (после блоков памяти) узлов. Целью изобретения является повышение помехоустойчивости и повышение быстродействия устройства. Поставленная цель по первому варианту достигается тем, что в элект ронное устройство, содержащее N (где N 1,2 , . .) модулей памяти, выводы питания которых соединены с соответствующими выходами дешифратора, входы которого являются адресными входами старших разрядов устройства, числовые выходы одного из модулей памяти соединены с первыми выводами нагрузочных элементов .одной группы, введены селектор и N -1 дополнительных групп нагрузочных элементов, причём первые выводы нагрузочных элементов дополнительных групп соединены с числовыми выходами соответствующих модулей памяти, вторые выводы нагрузочных эп&. ментов всех групп подключены к выводам питания соответствующих модулей памяти, числовые выходы модулей памяти соединены также с соответствующими входами селектора, выходы которого являются числовыми выходами устройства, а управляющие входы селектора соединены со входами дешифратора. По второму варианту в электронное устройство, содержащее N модулей пам51ти, выводы питания которых соединены с выходами соответствующих ключей питания, входы которых соединены с соответствующими выходами дешифратора, входы которого являются адресными входами старших разрядов устройства, числовые выходы модулей памяти соеоинены с первыми выводами нагрузочных элементов и являются числовыми выходами устройства, введены блок эл&ментов разрядки, ключевой элемент и дополнительный ключ питания, вход которого является первым управляющим входом устройства, а выход соединен с первыми выводами нагрузочных .элементов, вхоц ключевого элемента является , вторым управляющим входом устройства, а I выход соединен с первыми выводами бпока элементов развязки, вторые выводы которых соединены с выводами питания соответствующих модулей памяти. На фиг. 1 представлена блок-схема электронного устройства с регулировкой электропитания по первому варианту; на фиг. 2 - временные, диаграммы считаншлк сигналов лог. 1 и лог. О

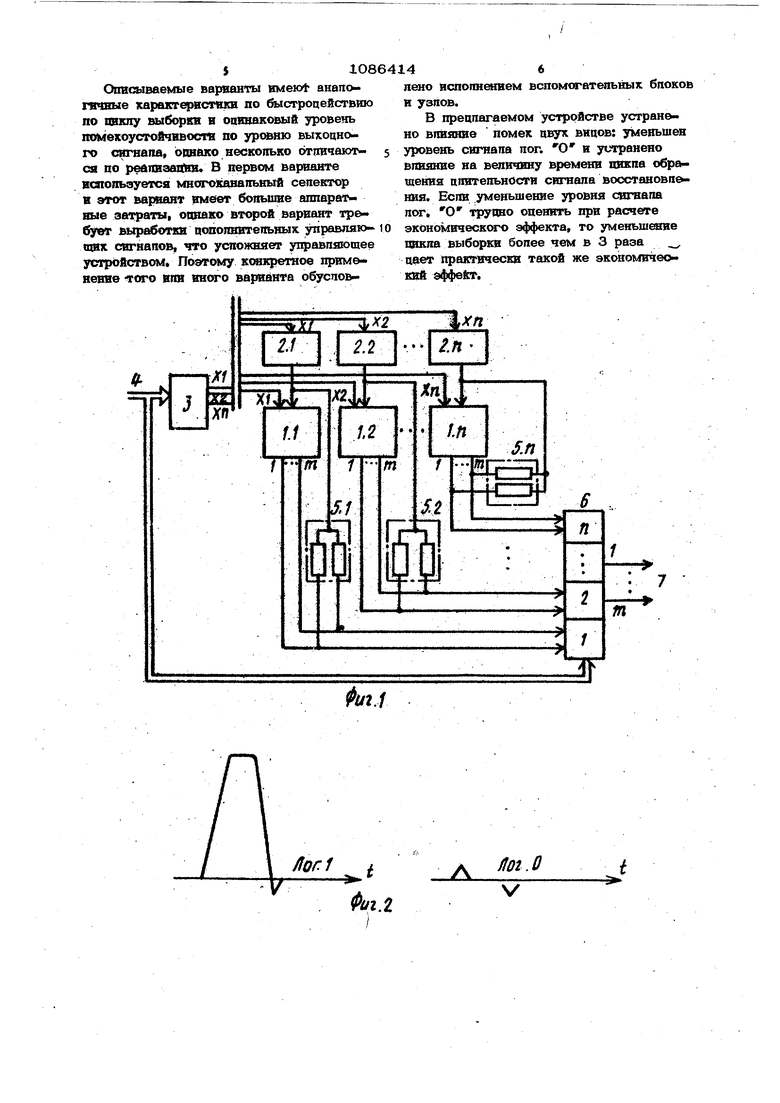

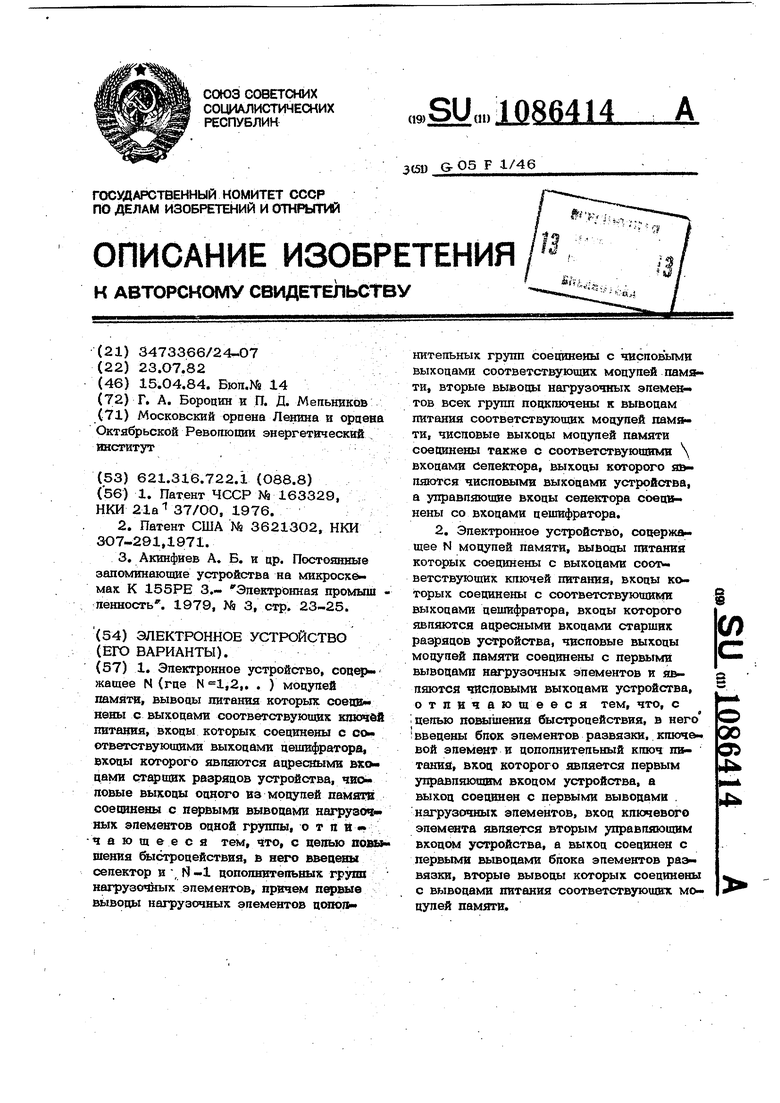

цпя этой блок-схемы; на фиг. 3 прецставпена бпок-скема эпектронного устройства регутфовкой электропитания по второму варианту,

Устройство соцержит модули памяти 1.1-1.N, выводы питания которых со цинены с выходами соответствующих ключей питания 2.1 -2.N , вкоцы которых соециненЪ, со входами стробирования соответствующих модулей памяти 1.1-1. и соединены с выходами дешифратора 3, входы которого являются адресными входами 4 старших разрядов устройства, числовые выходы модулей памяти 1.1-1.N соединены с первыми входами нагрузочных элементов соответствующих групп 5.. N , вторые выводы нагрузочных элементов каждой группы 5.1-5. N подключены к выводу питания соответствующего модуля памяти 1.1-1.N , входы каждой из групп селектора 6 соединены с числовыми выходами соответствующих модулей памяти 1.1-1. N .управляющие входы селектора 6 соединены со входами дешифратора 3, а выходы серектора 6 являются числовыми выходами 7 устройства.

Электронное устройство с peryitHpo&« кой электропитания по первому варианту работает следующим образом.

1В режиме выборки информации из модулей памяти 1.1-1.N по адресным входам 4 на дешифратор поступает код сташих разрядов адреса, который выбирает модуль 1. i , в котором хранится интересующая информация. Этот же код поступает на управляющий вход селектора 6, выбирая те входы, которые соответствуют выбранному модулю памяти 1.1 « Дешифратора 3 Выбирает соответст вующий ключ питания 2. i , включает его и стробирует соотвётствуюошй модуль зшмяти l.i. Выбранный модуль памяти 1. и соответствующая ему группа нагрузочных элементов 5.1 оказываются подкпюченными к питанию, а остапьные модули памяти обесточены и не потребпяют энергии. Считанная по соответствующем atgjecy информация поступает на соответствующий вход селектора 6 и выдает ся на выход 7. Подключение нагрузочны элементов к выводу питания соответст вующего модуля naMsrrH позволяет обео печить требуемый уровень лог. О на выходе (фиг..2), а допогенитепьное селектора обеспечивает уменьшение временицикла обращения. Действитепьно после окончания обращения к одному

из модулей памяти, сразу же может быть осуществлено обращение к другому модулю памяти.

Устройство содержит модули памяти 1.1-1. N , выводы питаний которых соединены с выходами соответствующих ключей питания 2.1-2. N , входы которых соединены со входами стробирования со ответствующих модулей памяти 1.1-1.14 и соединены с выходами дешифратора 3, входы которого являются адресньмн входами старших разрядов устройства 4, выходы модулей памяти 1.1-1.М объединены и соединены с первыми выводами нагрузочных элементов 5 и являются числовыми выходами 7 устройства, вторые выводы нагрузочных элементов подключены к выходу дополнительного ключа питания 8, вход которого является первым управляющим входом 9 уст ройства, вход 10 ключевого элемента является вторым управляющим входом устройства, а выход элемента 11 соедин с первыми выводами блока элементов развязки 12, вторые выводы которого соединены с соответствующими выводами питания модулей памяти 1.1-1.N . Элементы развязки могут быть выпопнё ны на диодах и катодами соединены с выходом элемента 11.

Устройство по второму варианту работает спедуюишм образом,

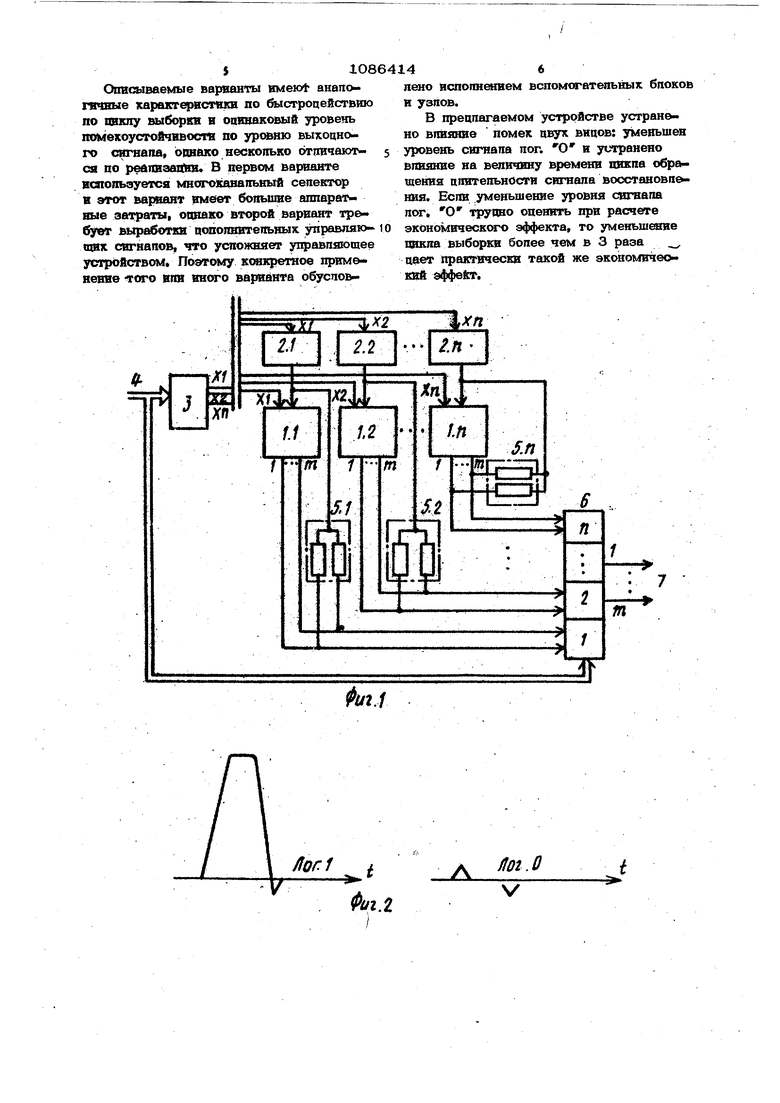

В режиме выборки информации из модулей памяти 1.1-1.N по адресным входам 4 на дешифратор 3 поступает код старших разрядов адреса, который выбирает модуль l.v , в котором хранится интересующая информация. Одновременно поступает сигнал включения ключа 8 по шине 9 и сигнал шлключения ключа 11 по шине 1О. Дешифраторе включает нужный ключ 2. i и строби- рует соответствующий модуль l.i , который оказывается подключенным к питанию, а остапьные обесточены. Считанная информация поступает на выхокы 7. . После окончания выборки питания с модуля снимается питание с нагрузочных элементов. Для разряда емкости вывода питания .включается ключевой элемент 11 который через соответствующий элемент развязки разряжает емкость вывода до значений, обеспечивающих откшочеяие вн.ренних узлов микросхем модулей памяти. При необходимости может быть прои ведено обращение к другому моцупю. Выходные сигналы лог. и аог. О аналогичны приведенным- на фиг. 3, Описываемые варианты вмеюф анапоппные характеристики по быстроцействию по пикпу выборвя и оциваковый уровень помехоустойчивосга по уровню выходного сигнала, опвако несколько сутдачаются по редпиааЦИв. В первом варванте испопьэуется многоканальный селектор и этот вариант имеет большие аппарат яые затраты, однако второй вариант тр&бует выработки пополнительных управляю щих сигналов что усложняет у1Ч)авляюще устройством Поэтому ктокретяое прим&иеиие -того или ижяо варианта обуспов If- ЛtiL

7 лено исполн геем вспомогательных блоков и узлов. В прецлагаемом устройстве устран но влияние помех цвух видов: утменьшен уровень сигнала лог. О и устранено влияние на величину времени пикла обращения цлительности силаала восстановл нвя. Если уменьшение уровня сигнала пог, О трудно оценить при расчете экономическотч эффекта, то уменьшение цикла выборки более чем в 3 раза дает практически такой же экономичеокий зффеКст 1дг/г

| название | год | авторы | номер документа |

|---|---|---|---|

| Электронное устройство | 1986 |

|

SU1334305A2 |

| Электронное устройство | 1987 |

|

SU1427518A2 |

| ЭЛЕКТРОИМПУЛЬСНОЕ ПРОТИВООБЛЕДЕНИТЕЛЬНОЕ УСТРОЙСТВО | 2013 |

|

RU2534102C1 |

| Устройство для программирования микросхем постоянной памяти | 1982 |

|

SU1134964A1 |

| Постоянное запоминающее устройство | 1981 |

|

SU1014037A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2130644C1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| Устройство для программирования микросхем постоянной памяти | 1985 |

|

SU1285535A1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1251260A1 |

| Постоянное запоминающее устрой-CTBO C АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU809366A1 |

1. Электронное устройство, сов ржащее N (где ,2,. . ) моцупей памяти, выводы питания которых соащм нены с выходами соответствующих кпкпдй питания, входы которых соединены с соответствующими выходами дешифратора, входы которого являются адресными входами старших разрядов устройства, чио повые выходы одного из модулей памяти соединены с первыми выводами нагрузоч ных элементов одной группы, о т п И чающееся тем, что, с цепью noBi# шения быстродействия, в него ввеоены селектор и , N-1 дополнительных групп нагрузочных элементов, причем первые выводь нагрузочных элементов цопог нитепьных групп соединены с числовыми выходами соответствующих модулей памяти, вторые выводы нагрузочных элеме тов всек групп подключены к выводам питания соответствующих модулей памяти, числовые выходы модулей памяти соединены также с соответствующими входами Селектора, выходы которого я&ляются числовыми выходами устройства, а управляющие входы сепектора соед. нены со входами дешифратора. 2. Электронное устройство, содержащее N модулей памяти, выводы питания которых соединены с выходами cooow ветствующих ключей питания, входы которых соединены с соответствующими 4S выходами дешифратора, входы которого являются адресными входами старших разрядов устройства, числовые выходы модулей памяти соединены с первыми выводами нагрузочных элементов и являются ЧИСЛОВЫМИ выходами устройства, отпйч ающееся тем, что, с i целью покушения быстродействия, в него 00 введены блок элементов развязки, ключеО) вой элемент и дополнительный ключ шьтаний, вход которого является первым управляющим входом устройства, а выход соединен с первыми выводами . нагрузочных элементов, вход ключевого элемента является вторым управляющим входш устройства, а выход соединен с первыми выводами блока элементов ра вязки, вторые выводы которых соединены с выводами питания соответствующих модулей памяти.

flot.O

1иг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0 |

|

SU163329A1 | |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Б | |||

| и цр | |||

| Канатное устройство для подъема и перемещения сыпучих и раздробленных тел | 1923 |

|

SU155A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1984-04-15—Публикация

1982-07-23—Подача