1

Изобретение относится к автоматике, измерительной и вычислительной технике и может быть использовано для онределения частотных характеристик динамических объектов.

Цель изобретения - повышение точности и расширение функциональных возможностей.

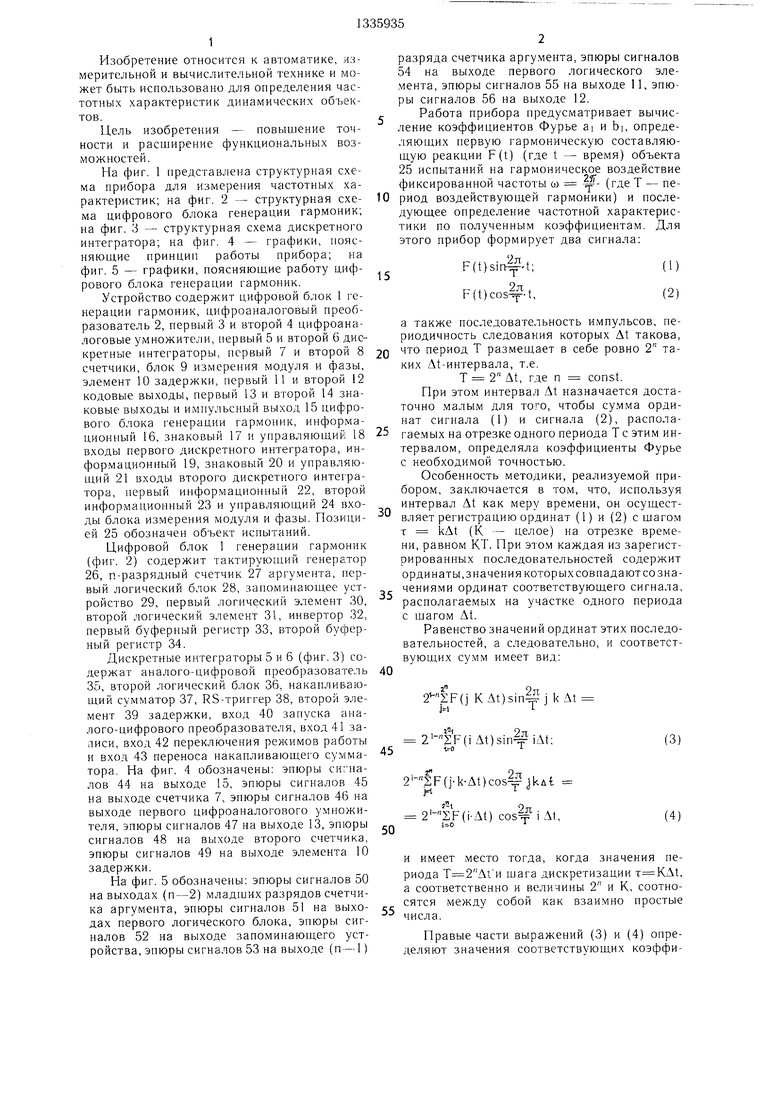

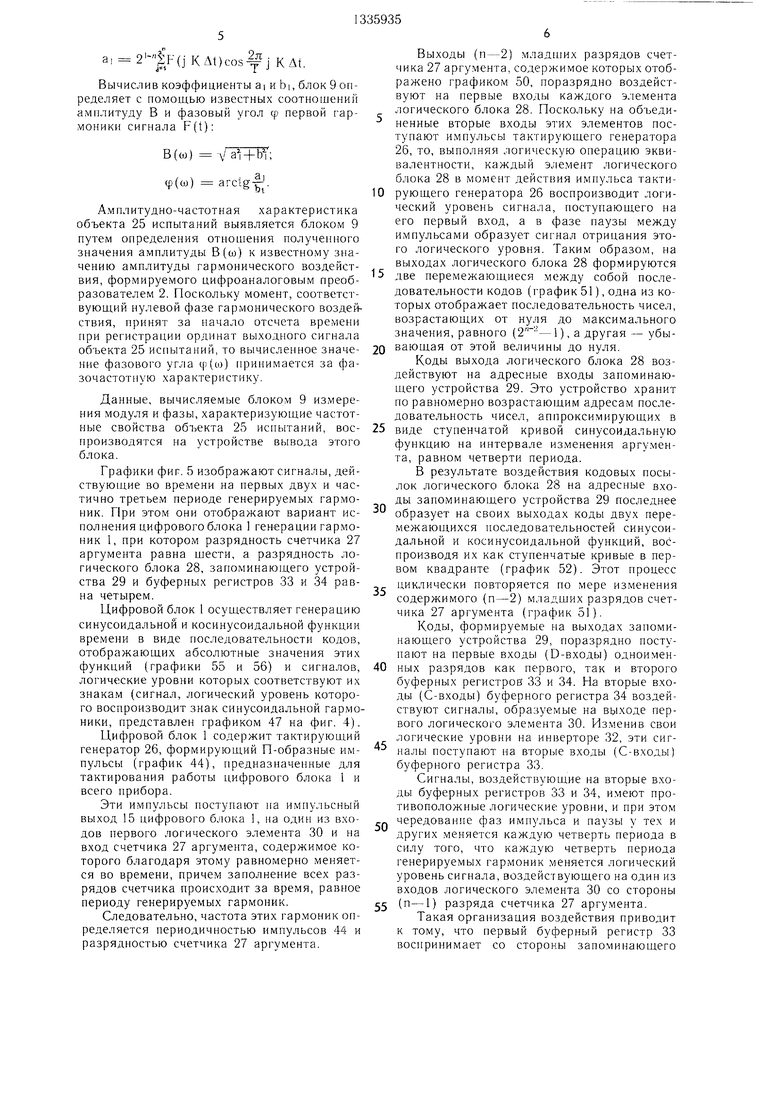

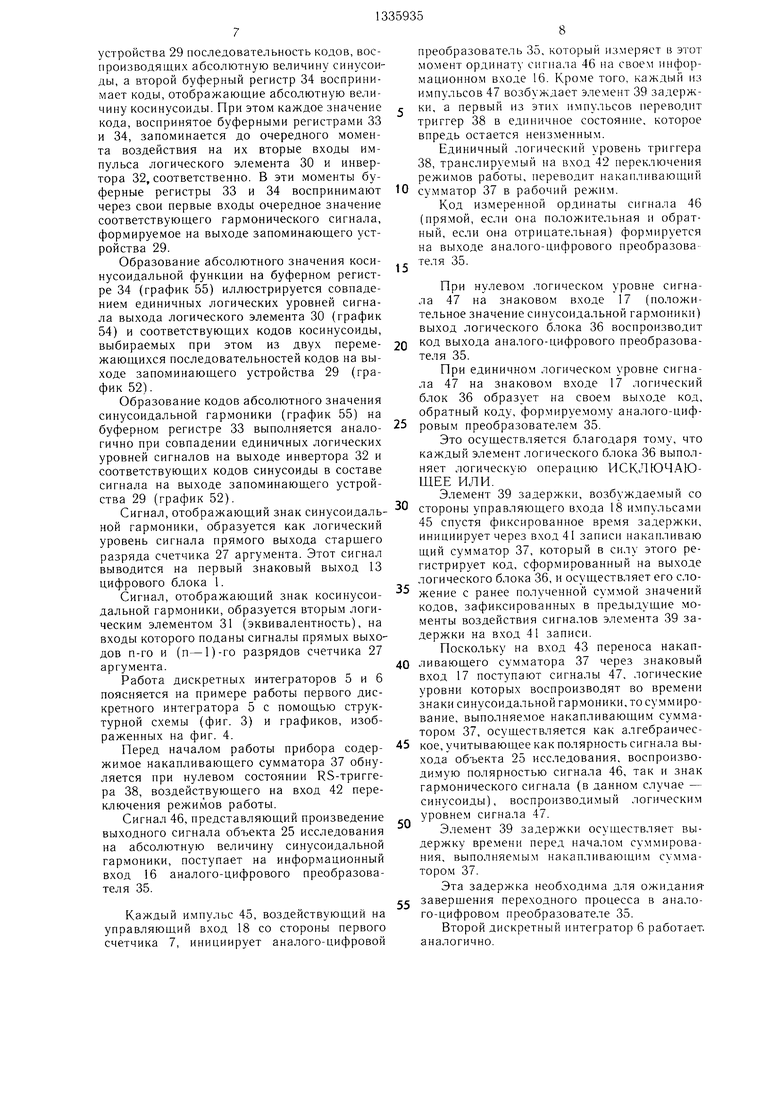

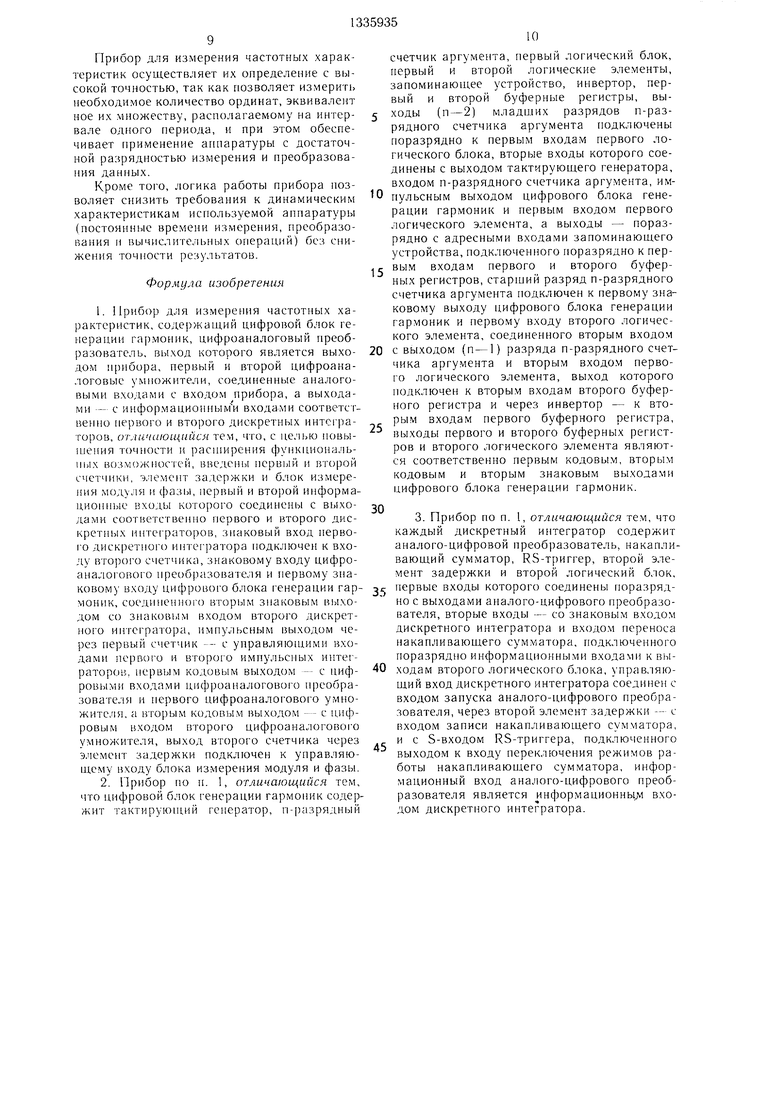

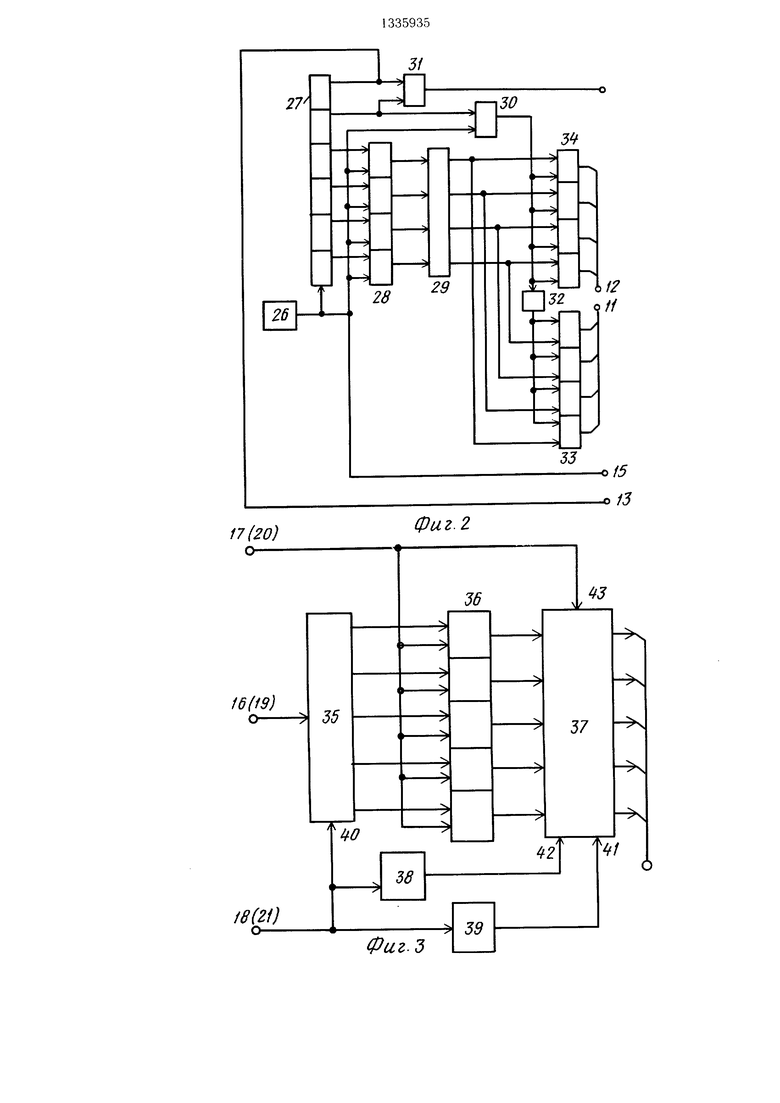

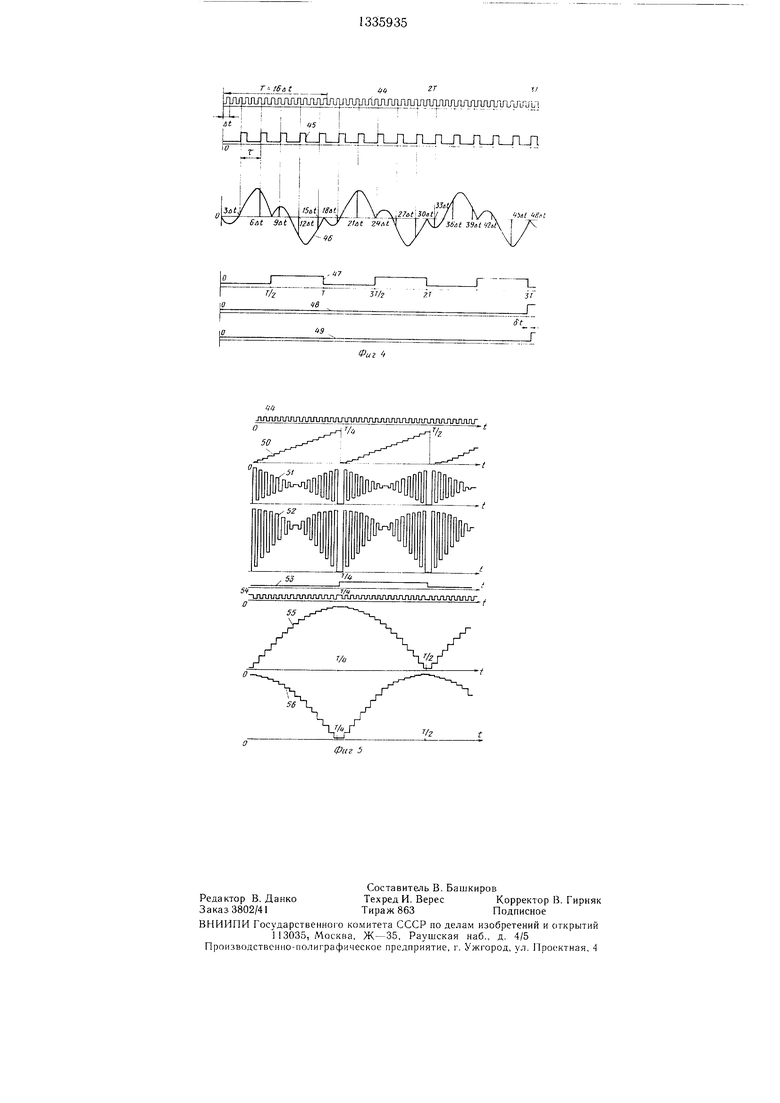

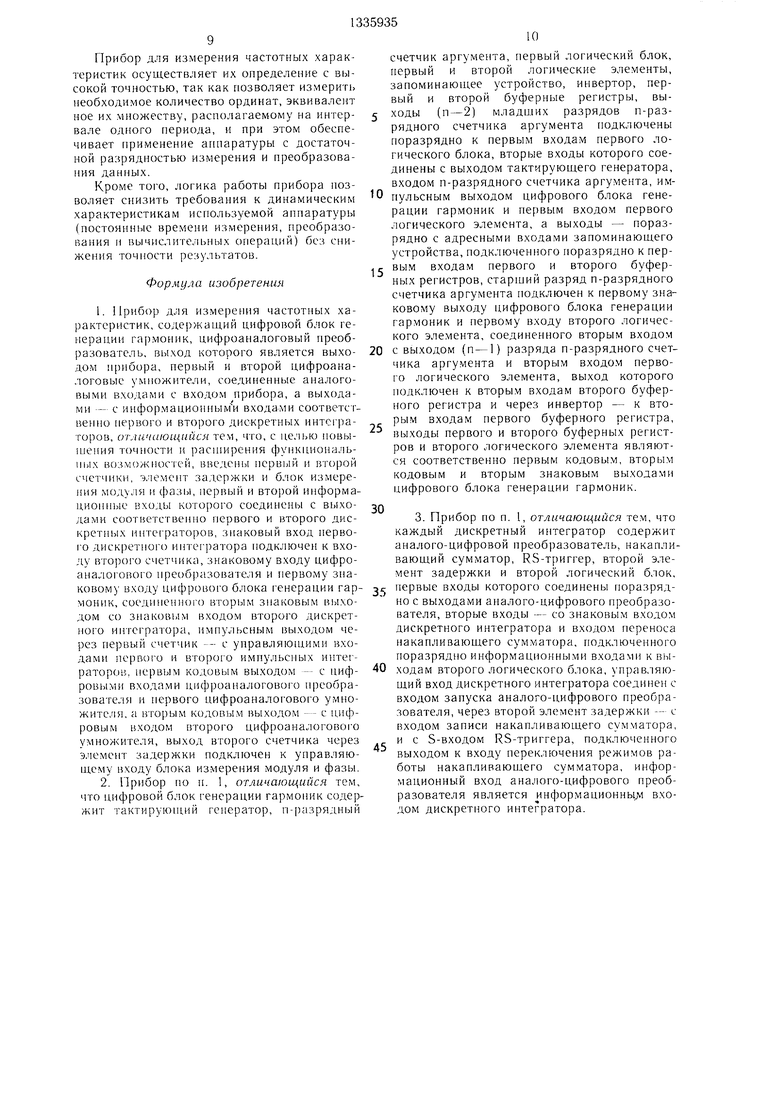

На фиг. 1 представлена структурная схема прибора для измерения частотных характеристик; на фиг. 2 - структурная схема цифрового блока генерации гармоник; на фиг. 3 - структурная схема дискретного интегратора; на фиг. 4 - графики, поясняющие принцип работы прибора; на фиг. 5 - графики, поясняющие работу цифрового блока генерации гармоник.

Устройство содержит цифровой блок 1 генерации гармоник, цифроаналоговый преобразователь 2, первый 3 и второй 4 цифроана- логовые умножители, первый 5 и второй 6 .аис- кретные интеграторы, первый 7 и второй 8 счетчики, блок 9 измерения модуля и фазы, элемент 10 задержки, первый 11 и второй 12 кодовые выходы, первый 13 и второй 14 знаковые выходы и импульсный выход 15 цифрового блока генерации гармоник, информационный 16, знаковый 17 и управляющий 18 входы первого дискретного интегратора, информационный 19, знаковый 20 и управляющий 21 входы второго дискретного интегратора, первый информационный 22, второй информационный 23 и управляющий 24 входы блока измерения модуля и фазы. Позицией 25 обозначен объект испытаний.

Цифровой блок 1 генерации гармоник (фиг. 2) содержит тактирующий генератор 26, п-разрядный счетчик 27 аргумента, первый логический блок 28, запоминающее устройство 29, первый логический элемент 30, второй логический элемент 31, инвертор 32, первый буферный регистр 33, второй буферный регистр 34.

Дискретные интеграторы 5 и 6 (фиг. 3) содержат аналого-цифровой преобразователь 35, второй логический блок 36, накапливающий сумматор 37, RS-триггер 38, второй элемент 39 задержки, вход 40 запуска аналого-цифрового преобразователя, вход 41 записи, вход 42 переключения режимов работы и вход 43 переноса накапливающего сумматора. На фиг. 4 обозначены: эпюры сигналов 44 на выходе 15, эпюры сигналов 45 на выходе счетчика 7, эпюры сигналов 46 на выходе первого цифроаналогового умножителя, эпюры сигналов 47 на выходе 13, эпюры сигналов 48 на выходе второго счетчика, эпюры сигналов 49 на выходе эле.мента 10 задержки.

На фиг. 5 обозначены: эпюры сигналов 50 на выходах (п-2) младших разрядов счетчика аргумента, эпюры сигналов 51 на выходах первого логического блока, эпюры сигналов 52 на выходе запоминающего устройства, эпюры сигналов 53 на выходе (п-1)

разряда счетчика аргу.мента, эпюры сигналов 54 на выходе первого логического элемента, эпюры сигналов 55 на выходе 11, эпюры сигналов 56 на выходе 12.

Работа прибора предусматривает вычисление коэффициентов Фурье ai и bi, определяющих первую гармоническую составляющую реакции F(t) (где t - время) объекта 25 испытаний на гармоническое воздействие фиксированной частоты ш (где Т - период воздействующей гармоники) и последующее определение частотной характеристики по полученным коэффициентам. Для этого прибор формирует два сигнала:

15

F(t)sin.t; F(t)cos%-t,

(2)

а также последовательность импульсов, периодичность следования которых Д1 такова,

что период Т размещает в себе ровно 2 таких Д1-интервала, т.е.

Т 2 At, где п const. При этом интервал At назначается достаточно малым для того, чтобы су.мма ординат сигнала (1) и сигнала (2), располагаемых на отрезке одного периода Т с этим интервалом, определяла коэффициенты Фурье с необходимой точностью.

Особенность методики, реализуемой прибором, заключается в том, что, используя интервал At как меру времени, он осуществляет регистрацию ординат (1) и (2) с щагом т kAt (К - целое) на отрезке времени, равном КТ. При этом каждая из зарегистрированных последовательностей содержит ординаты,значения которых совпадают со значениями ординат соответствующего сигнала, располагаемых на участке одного периода с щагом At.

Равенство значений ординат этих последовательностей, а следовательно, и соответствующих сум.м имеет вид:

(j KAt) k At

г Н

. 2л .,

(i At)sin4piAt;

(j-k-At)cos25 .kit .И

50

2 - SF(i-At) AI,

(4)

и имеет место тогда, когда значения периода шага дискретизации , а соответственно и величины 2 и К, соотносятся между собой как взаимно простые числа.

Правые части выражений (3) и (4) опре- ;1еляют значения соответствующих коэффициентов Фурье (bi и ai) первой гармоники периодического сигнала F(t), вычисляемых по приближенным формулам Бесселя.

Такая регистрация ординат сигналов (1) и (2), реализуемая предложенным прибором и их последующее суммирование обеспечивает получение необходимых данных для вычисления коэффициентов Фурье. При этом возможность выбора значения К, при котором шаг регистрации превышает постоянную времени применяемой аппаратуры, позволяет регистрировать необходимое количество слагаемых левых частей выражений (3) и (4) для определения коэффициентов Фурье с требуемой точностью.

Прибор работает следуюш.им образом.

Последовательность импульсов 44 формируется с периодичностью At на импульсном выходе 15 цифрового блока 1 генерации гармоник. На первом и втором кодовых выходах 11 и 12 этого блока образуются коды, аппроксимирующие абсолютные значения, соответственно, синусоидальной и коси- нусоидальной функций времени в виде ступенчатых кривых.

Код абсолютной величины синусоидального сигнала, образуемый на . выходе 11, и бинарный сигнал 47 первого знакового выхода 13, воздействуют на выходы цифроана- логового преобразователя 2, образующего синусоидальный аналоговый сигнал, возбуждающий объект 25 испытаний. Объект 25 испытаний реагирует на это возбуждение образованием периодического сигнала F(t) на своем выходе.

Этот периодический сигнал поступает на аналоговые входы цифроаналоговых умножителей 3 и 4, цифровые входы которых одновременно воспринимают коды абсолютных значений синусоидального и косинусои- дального сигналов, соответственно, с выходов 11 и 12 цифрового блока 1.

Благодаря этому на выходах первого и второго цифроаналоговых умножителей 3 и 4 образуются сигналы произведений

F(t) и F(t)

График 46 сигнала этого типа, образуемый на выходе первого цифроаналогового умножителя 3, изображен на фиг. 4.

Сигналы, образуемые цифроаналоговыми умножителями 3 и 4, транслируются, соответственно, на .информационные входы 16 и 19 дискретных интеграторов 5 и 6. На знаковые входы этих интеграторов со стороны знаковых выходов 13 и 14 цифрового блока 1 одновременно воздействуют сигналы, логические уровни которых воспроизводят знаки, соответственно, синусоидальной и ко- синусоидальной гармоник . Один из этих сигналов, а именно сигнал выхода ГЗ цифрового блока 1, определяющий знак синусоидальной гармоники, представлен графиком 47 на фиг. 4.

0

Дискретные интеграторы 5 и 6 при суммировании величин ординат сигналов, поступающих на их информационные входы 16 и 19. учитывают полярность этих сигналов, а также логические уровни сигналов на своих знаковых входах 17 и 20 ,(знаки гармоник).

Дискретные интеграторы 5 и 6 в момент воздействия на их управляющие вхОды 18 и 21 последнего, т.е. импульса счетчика 7, образуемого им на интервале времени К.Т (график 45), выполняют последнюю регистрацию ординат сигналов цифро- аналоговых умножителей 3 и 4, которые необходимы для вычисления коэффициентов Фурье. В этот момент времени по заднему фрон5 ту К-го импульса знакового выхода 13 цифрового блока 1 (график 47), т.е. по истечении К периодов длительностью Т, второй счетчик 8 образует на своем выходе сигнал 48. Этот сигнал, воздействуя на элемент 10 задержки, вызывает на его выходе через время 6t. появ0 ление сигнала 49.

Сигнал 49, поступая на управляющий вход 24 блока 9 измерения модуля и фазы, инициирует его для восприятия через информационные входы 22 и 23 кодов, сформиро5 ванных на выходах дискретных интеграторов 5 и 6 и воспроизводящих суммы ординат сигналов (1) и (2), зафиксированных с шагом дискретизации т КЛ1 на отрезке времени, равном К.Т.

Задержка возбужденияуправляющего вхо0 да 24 блока 9 измерения после появления сигнала 48 необходима для ожидания завершения переходных процессов в дискретных интеграторах 5 и 6., связанных с последним циклом суммирования.

Соответствие между значениями аргумен5 тов ординат, регистрируемых дискретными интеграторами 5 и 6, а также значениями аргументов ординат, располагаемых на участке одного периода для случая, когда и Т 16At (фиг. 4), иллюстрируется следующими соотношениями:

0

5

З.М З.Д(;

6.At 6.At;

9.At 9.At; 12.At 12.At; 15.At 15.At; 18.At 2.At + T: 21.At 5.At + T; 24.At 8.At + T;

27.At 11 .At + T;

30.At 14.At + T;

33.At l.At + 2T;

36.At 4.At + 2T;

39.At 7.At + 2T; 42.At 10.At + 2T; 45.At 13.At + 2T;

48.At O.At + 3T.

Блок 9 измерения модуля и фазы, зафиксировав через свои информационные вхо- 0 ДЬ1 22 и 23 коды чисел, определяющих суммы ординат сигналов (1) и (2), выполняет умножение зафиксированных сумм на масштабные множители , образуя этим коэффициенты Фурье первой гармоники сигнала реакции объекта 25 испытаний на гармоническое воздействие со стороны цифроаналогового преобразователя 2:

Ь, (j KAt).K-.t;

5

a, (jKAt)

К At.

Вычислив коэффициенты a nb, блок 9 определяет с помощью известных соотношений амплитуду В и фазовый угол ф первой гар- МОНИКИ сигнала F(t):

B(oj) Va1+bT;

(п((л) arcig-r- .

bi

Амплитудно-частотная характеристика объекта 25 испытаний выявляется блоком 9 путем определения отношения полученного значения амплитуды В(ы) к известному значению амплитуды гармонического воздействия, формируемого цифроаналоговым преобразователем 2. Поскольку момент, соответствующий нулевой фазе гармонического воздействия, принят за начало отсчета времени при регистрации ординат выходного сигнала объекта 25 испытаний, то вычисленное значе- ние фазового угла cp(co) принимается за фа- зочастотную характеристику.

Данные, вычисляемые блоком 9 измерения модуля и фазы, характеризующие частотные свойства объекта 25 испытаний, вое- производятся на устройстве вывода этого блока.

Графики фир. 5 изображают сигналы, дей- ствуюп 1ие во времени на первых двух и частично третьем периоде генерируемых гармоник. При этом они отображают вариант исполнения цифрового блока 1 ген-ерации гармоник 1, при котором разрядность счетчика 27 аргумента равна щести, а разрядность логического блока 28, запоминающего устройства 29 и буферных регистров 33 и 34 равна четырем.

Цифровой блок 1 осуществляет генерацию синусоидальной и косинусоидальной функции времени в виде последовательности кодов, отображающих абсолютные значения этих функций (графики 55 и 56) и сигналов, логические уровни которых соответствуют их знакам (сигнал, логический уровень которого воспроизводит знак синусоидальной гармоники, представлен графиком 47 на фиг. 4).

Цифровой блок 1 содержит тактирующий генератор 26, формирующий П-образные импульсы (график 44), предназначенные для тактирования работы цифрового блока 1 и всего прибора.

Эти импульсы поступают на импульсный выход 15 цифрового блока 1, на один из входов первого логического элемента 30 и на вход счетчика 27 аргумента, содержимое которого благодаря этому равномерно меняется во времени, причем заполнение всех разрядов счетчика происходит за время, равное периоду генерируемых гармоник.

Следовательно, частота этих гармоник определяется периодичностью импульсов 44 и разрядностью счетчика 27 аргумента.

5

0

0

5

0

5

0

5

0

Выходы (п-2) младших разрядов счетчика 27 аргумента, содержимое которых отображено графиком 50, поразрядно воздействуют на первые входы каждого элемента логического блока 28. Поскольку на объединенные вторые входы этих элементов поступают импульсы тактирующего генератора 26, то, выполняя логическую операцию эквивалентности, каждый элемент логического блока 28 в момент действия импульса тактирующего генератора 26 воспроизводит логический уровень сигнала, поступающего на его первый вход, а в фазе паузы между импульсами образует сигнал отрицания этого логического уровня. Таким образом, на выходах логического блока 28 формируются две перемежающиеся между собой последовательности кодов (график 51), одна из которых отображает последовательность чисел, возрастающих от нуля до максимального значения, равного ( ), а другая - убывающая от этой величины до нуля.

Коды выхода логического блока 28 воздействуют на адресные входы запоминающего устройства 29. Это устройство хранит по равномерно возрастающим адресам последовательность чисел, аппроксимирующих в виде ступенчатой кривой синусоидальную функцию на интервале изменения аргу.мен- та, равном четверти периода.

В результате воздействия кодовых посылок логического блока 28 на адресные входы запоминающего устройства 29 последнее образует на своих выходах коды двух перемежающихся последовательностей синусоидальной и косинусоидальной функций, воспроизводя их как ступенчатые кривые в первом квадранте (график 52). Этот процесс циклически повторяется по мере изменения содержимого (п-2) младших разрядов счетчика 27 аргумента (график 51).

Коды, формируемые на выходах запоминающего устройства 29, поразрядно поступают на первые входы (D-входы) одноименных разрядов как первого, так и второго буферных регистров 33 и 34. На вторые входы (С-входы) буферного регистра 34 воздействуют сигналы, образуемые на выходе первого логического элемента 30. Изменив свои логические уровни на инверторе 32, эти сигналы поступают па вторые входы (С-входы) буферного регистра 33.

Сигналы, воздействующие на вторые входы буферных регистров 33 и 34, имеют противоположные логические уровни, и при этом чередование фаз импульса и паузы у тех и других меняется каждую четверть периода в силу того, что каждую четверть периода генерируемых гармоник меняется логический уровень сигнала, воздействующего на один из входов логического элемента 30 со стороны (п-1) разряда счетчика 27 аргумента.

Такая организация воздействия приводит к тому, что первый буферный регистр 33 воспринимает со стороны запоминающего

7

устройства 29 последовательность кодов, воспроизводящих абсолютную величину синусоиды, а второй буферный регистр 34 воспринимает коды, отображающие абсолютную величину косинусоиды. При этом каждое значение кода, воспринятое буферными регистрами 33 и 34, запоминается до очередного момента воздействия на их вторые входы импульса логического элемента 30 и инвертора 32, соответственно. В эти моменты бупреобразователь 35, который из момент ординату сигнала 46 на мационном входе 16. Кроме тог импульсов 47 возбуждает элемен ки, а первый из этих импульс триггер 38 в единичное состоя впрвлТЬ остается неизменным.

Единичный логический уров 38, транслируемый на вход 42 п режимов работы, переводит нак

ферные регистры 33 и 34 воспринимают 10 сумматор 37 в рабочий режим.

через свои первые входы очередное значение соответствуюпдего гармонического сигнала, формируемое на выходе запоминающего устройства 29.

Образование абсолютного значения коси- нусоидальной функции на буферном регистре 34 (график 55) иллюстрируется совпадением единичных логических уровней сигнала выхода логического элемента 30 (график 54) и соответствующих кодов косинусоиды, выбираемых при этом из двух перемежающихся последовательностей кодов на выходе запоминающего устройства 29 (график 52).

Образование кодов абсолютного значения синусоидальной гармоники (график 55) на буферном регистре 33 выполняется аналогично при совпадении единичных логических уровней сигналов на выходе инвертора 32 и соответствующих кодов синусоиды в составе сигнала на выходе запоминающего устройства 29 (график 52).

15

Код измеренной ординаты сигнала 46 (прямой, если она положительная и обратный, если она отрицательная) формируется на выходе аналого-цифрового преобразова теля 35.

При нулевом логическом уровне сигнала 47 на знаковом входе 17 (положительное значение синусоидальной гармоники) выход логического блока 36 воспроизводит 20 код выхода аналого-цифрового преобразователя 35.

При единичном логическом уровне сигнала 47 на знаковом входе 17 логический блок 36 образует на своем выходе код, обратный коду, формируемому аналого-циф- 25 ровым преобразователем 35.

Это осуществляется благодаря тому, что каждый элемент логического блока 36 выполняет логическую операцию ИСКЛЮЧАЮЩЕЕ ИЛИ.

Элемент 39 задержки, возбуждаемый со

Сигнал, отображающий знак синусоидаль- стороны управляющего входа 18 импульсами

ной гармоники, образуется как логический уровень сигнала прямого выхода старшего разряда счетчика 27 аргумента. Этот сигнал выводится на первый знаковый выход 13 цифрового блока 1.

Сигнал, отображающий знак косинусои- дальной гармоники, образуется вторым логическим элементом 31 (эквивалентность), на входы которого поданы сигналы прямых выходов п-го и (п-1)-го разрядов счетчика 27 аргумента.

Работа дискретных интеграторов 5 и 6 поясняется на примере работы первого дискретного интегратора 5 с помощью структурной схемы (фиг. 3) и графиков, изображенных на фиг. 4.

35

45 спустя фиксированное время задержки, инициирует через вход 41 записи накапливаю щий сумматор 37, который в силу этого регистрирует код, сформированный на выходе логического блока 36, и осуществляет его сложение с ранее полученной суммой значений кодов, зафиксированных в предыдущие моменты воздействия сигналов элемента 39 задержки на вход 41 записи.

Поскольку на вход 43 переноса накап- 40 ливающего сумматора 37 через знаковый вход 17 поступают сигналы 47, логические уровни которых воспроизводят во времени знаки синусоидальной гармоники, то сум миро- ванне, выполняемое накапливающим сумматором 37, осуществляется как алгебраичесПеред началом работы прибора содер- 45 кое, учитывающее как полярность сигнала вы- жимое накапливающего сумматора 37 обну-хода объекта 25 исследования, воспроизволяется при нулевом состоянии RS-тригге-димую полярностью сигнала 46, так и знак

гармонического сигнала (в данном случае

ра 38, воздействующего на вход 42 пере ключения режимов работы.

Сигнал 46, представляющий произведение выходного сигнала объекта 25 исследования на абсолютную величину синусоидальной гармоники, поступает на информационный вход 16 аналого-цифрового преобразователя 35.

Каждый импульс 45, воздействующий на управляющий вход 18 со стороны первого счетчика 7, инициирует аналого-цифровой

синусоиды), воспроизводимый логическим уровнем сигнала 47.

Элемент 39 задержки осуществляет выдержку времени перед началом суммирования, выполняемым накапливающим сумматором 37.

Эта задержка необходима для ожидания- 55 заверщения переходного процесса в аналого-цифровом преобразователе 35.

Второй дискретный интегратор 6 работает, аналогично.

8

преобразователь 35, который измеряет в этот момент ординату сигнала 46 на своем информационном входе 16. Кроме того, каждый из импульсов 47 возбуждает элемент 39 задержки, а первый из этих импульсов переводит триггер 38 в единичное состояние, которое впрвлТЬ остается неизменным.

Единичный логический уровень триггера 38, транслируемый на вход 42 переключения режимов работы, переводит накапливаюп ий

сумматор 37 в рабочий режим.

Код измеренной ординаты сигнала 46 (прямой, если она положительная и обратный, если она отрицательная) формируется на выходе аналого-цифрового преобразова теля 35.

При нулевом логическом уровне сигнала 47 на знаковом входе 17 (положительное значение синусоидальной гармоники) выход логического блока 36 воспроизводит код выхода аналого-цифрового преобразователя 35.

При единичном логическом уровне сигнала 47 на знаковом входе 17 логический блок 36 образует на своем выходе код, обратный коду, формируемому аналого-циф- ровым преобразователем 35.

Это осуществляется благодаря тому, что каждый элемент логического блока 36 выполняет логическую операцию ИСКЛЮЧАЮЩЕЕ ИЛИ.

Элемент 39 задержки, возбуждаемый со

стороны управляющего входа 18 импульсами

стороны управляющего входа 18 импульсами

45 спустя фиксированное время задержки, инициирует через вход 41 записи накапливаю щий сумматор 37, который в силу этого регистрирует код, сформированный на выходе логического блока 36, и осуществляет его сложение с ранее полученной суммой значений кодов, зафиксированных в предыдущие моменты воздействия сигналов элемента 39 задержки на вход 41 записи.

Поскольку на вход 43 переноса накап- ливающего сумматора 37 через знаковый вход 17 поступают сигналы 47, логические уровни которых воспроизводят во времени знаки синусоидальной гармоники, то сум миро- ванне, выполняемое накапливающим сумматором 37, осуществляется как алгебраическое, учитывающее как полярность сигнала вы- хода объекта 25 исследования, воспроизвосинусоиды), воспроизводимый логическим уровнем сигнала 47.

Элемент 39 задержки осуществляет выдержку времени перед началом суммирования, выполняемым накапливающим сумматором 37.

Эта задержка необходима для ожидания- 5 заверщения переходного процесса в аналого-цифровом преобразователе 35.

Второй дискретный интегратор 6 работает, аналогично.

9

Прибор для измерения частотных характеристик осуществляет их определение с высокой точностью, так как иозволяет измерить необходимое количество ординат, эквивалент ное их множеству, располагаемому на интервале одного периода, и при этом обеспечивает применение аппаратуры с достаточной разрядностью измерения и иреобразова- ния данных.

Кроме того, логика работы прибора позволяет снизить требования к динамическим характеристикам используемой аппаратуры (постоянные времени измерения, преобразования и вычислительных операций) без снижения точности результатов.

Формула изобретения

1.Прибор для измерения частотных характеристик, содержащий цифровой блок генерации гармоник, цифроаналоговый преобразователь, выход которого является выходом прибора, первый и второй цифроана- логовые умножители, соединенные аналоговыми входами с входом прибора, а выходами - с информационпым и входами соответственно первого и второго дискретных интеграторов, отличающийся тем, что, с целью повы- 1пепия точности и )асп1ирення функпиональ- 1П)1х возм()жнос 1ей, введены первый и второй счетчики, э.:1емепт задержки и блок измерения модуля и фазы, первый и вто)ой ипформа- циопиые входы которого соединены с выходами соответственно первого и второго дискретных интег раторов, знаковый вход первого дискретного интегратора подключен к входу второго счетчика, знаковому входу цифро- ана.:101 ового нреобразователя и первому знаковому входу цифрового блока генерации гармоник, соединенного вторым знаковым В1згчо- дом со знаковым входом второго дискретного интегратора, импульсным выходом через первый счетчик - - с унравляюнгими входами первого и второго импульсных интеграторов, первым кодовым выходом -- с цифровыми входами цнфроапалогового ирсобра- зователя и первого цифроаналогового умножителя, а вторым кодовым выходом с цифровым входом второго цифроапалогового умножителя, выход второго счетчика через элемент задержки подключен к управляю- илему входу блока измерения модуля и фазы.

2.Прибор по н. 1, отличающийся тем, что цифровой блок генерации гармоник содержит тактируюпиж генератор, п-разрядный

К)

счетчик аргумента, первый логический блок, первый и второй логические элементы, запоминающее устройство, инвертор, первый и второй буферные регистры, выходы (п-2) младших разрядов п-раз- рядного счетчика аргумента подключены поразрядно к первым входам первого логического блока, вторые входы которого соединены с выходом тактирующего генератора, входом п-разрядного счетчика аргумента, им0 пульсным выходом цифрового блока генерации гармоник и первым входом первого логического элемента, а выходы - поразрядно с адресными входами запоминающего устройства, подключенного поразрядно к перг вым входам первого и второго буферных регистров, старщий разряд п-разрядного счетчика аргумента нодключен к первому знаковому выходу цифрового блока генерации гармоник и первому входу второго логического элемента, соединенного вторым входом

0 с выходом (п-1) разряда п-разрядного счетчика аргумента и вторым входом первого логического элемента, выход которого нодключеп к вторым входам второго буферного регистра и через инвертор - к вторым входам первого буферного регистра,

выходы первого и второго буферных регистров и второго логического элемента являются соответственно первым кодовым, вторым кодовым и вторым знаковым выходами цифрового блока генерации гармоник.

3. Прибор по п. 1, отличающийся те.м, что каждый дискретный интегратор содержит аналого-цифровой нреобразователь, накапливающий сумматор, RS-триггер, второй элемент задержки и второй логический блок,

i первые входы которого соединены поразрядно с выходами аналого-цифрового преобразователя, вторые входы - со знаковым входом дискретного интегратора и входом переноса накапливающего сумматора, подключенного поразрядно информационными входами к вы0 ходам второго логического блока, управляю- н|ий вход дискретного интегратора соединен с входом запуска аналого-цифрового преобразователя, через второй элемент задержки -- с входом записи накапливающего сумматора, и с S-входом RS-триггера, подключенного выходом к входу переключения режимов работы накапливаюпдего сумматора, информационный вход аналого-цифрового преобразователя является информационны 1 входом дискретного интегратора.

5

27

ш

54

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для поиска максимума корреляционной функции | 1990 |

|

SU1727135A1 |

| Цифровой генератор синусоидальных сигналов | 1984 |

|

SU1215162A1 |

| Устройство для воспроизведения функций | 1990 |

|

SU1732360A2 |

| Вероятностный коррелометр | 1986 |

|

SU1327121A1 |

| Устройство для воспроизведения функций | 1989 |

|

SU1644177A1 |

| Устройство для измерения ортогональных составляющих сигнала | 1982 |

|

SU1091082A1 |

| Устройство для поиска максимума корреляционной функции | 1977 |

|

SU696479A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1273944A1 |

| Усреднитель-анализатор спектра Фурье | 1980 |

|

SU955086A1 |

Изобретение относится к автоматике, из мерительной и вычислительной технике и может быть использовано для определения частотных характеристик динамических объектов. Цель изобретения - повышение точности и расширение функциональных возможностей. Прибор для измерения частотных характеристик содержит цифровой блок 1 генерации гармоник, цифроаналоговый преобразователь 2, первый 3 и второй 4 цифро- аналоговые умножители, первый 5 и второй 6 дискретные интеграторы, первый 7 и второй 8 счетчики, блок 9 измерения модуля и фазы, элемент 10 задержки. Блок 1 имеет первый и второй кодовые выходы, первый и второй знаковые выходы, импульсный выход. Первый дискретный интегратор имеет информационный, знаковый и управляющий входы. Второй дискретный интегратор имеет информационный, знаковый и управляющий входы. Блок 9 имеет первый, второй информационные и управляющий входы. Вход и выход объекта подключены к объекту испытаний. Цель изобретения достигается за счет введения первого 7 и второго 8 счетчиков, блока 9 и элемента 10 задержки. Прибор для измерения частотных характеристик осуществляет определение с высокой точностью, т.к. позволяет измерить необходимое количество ординат, эквивалентное их множеству, располагаемому на интервале одного периода, и при этом обеспечивает применение аппаратуры с достаточной разрядностью измерения и преобразования данных. 2 з.п. ф-лы, 5 ил. (Л оо оо СП СО оо сд

I

28

29

)// //

17(20)

16(19

О

J5

5J

-0/5 /5

фиг. 2

6

t

4 J

37

-

/

t8(2i о-

Фиг.Ъ

7 6ut

««2Гт/

l.aЛrlлгLaллляллллflЛJlJ шллJUL JlГJ LI

LTLR

if,ft

«4 ллплллллллллплл игяштшишлллллллпплллляг

5«f. f

пJuглдлллJVlлл uггunлJVUulnллллллляяJгдJгягuuгяг 0

55

Фиг 5

| Анализатор частотных характеристик | 1977 |

|

SU679944A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| АНАЛИЗАТОР ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 0 |

|

SU199535A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-07—Подача