го элемента ИЛИ, выход которого соединен со знаковым входом второго накапливающего сумматора и с вторым инвертором, седьмой выход блока управления соединен с вторым входом элемента И второй группы, первый вход которого соед1рен с прямым выходом знакового разряда, первого регистра, второй входдругого элемента И второй группы соединен с восьмым выходом блока управления, вход которого соединен с входом тактовых импульсов аналого-цифрового преобразователя и тактовыми входами накапливающих сумматоров, выход второго элемента ИЛИ соединен с вторыми входами тех элементов И пятой группы, к первым входам которых, через элементы И восьмой группы и

элементы ИЛИ второй группы подключены прямые выходы разрядов второго регистра, с вторыми входами остальных элементов И пятой группы соединен выход второго инвертора, выходы элементов

НИИ первой группы сбединены с первыми входами элементов И шестой группы, выходы которых соединены с входами первого накапливающего сумматора, вход первого инвертора соединен с вторыми входами тех элементов И шестой группы, к первым входам которых через элементы И четвертой группы и элементы ИЛИ первой группы подключены прямые выходы разрядов, кроме знакового,

первого регистра, выход первого инвертора соединен с вторыми входами остальных элементов И шестой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Устройство контроля качества канала связи | 1987 |

|

SU1499508A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для центрирования изображения | 1987 |

|

SU1513483A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1242936A1 |

| Устройство для сравнения двоичных чисел | 1978 |

|

SU748408A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для сравнения двоичных чисел | 1979 |

|

SU877522A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1988 |

|

SU1569983A1 |

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОРТОГОНАЛЬНЫХ СОСТАВЛЯЮЩИХ СИГНАЛА, содержащее аналого-цифровой преобразователь, состоящий из последовательна соединенных блока преобразования и первого регистра, прямые и инверсные выходы всех разрядов которого, кроме знакового, соединены с первыми входами логических элементов И первой группы, а выходы знакового разряда с первыми входами логических элементов И второй группы, выходы которых соединены с входами первого элемента ИЛИ, выход которого соединен с входом первого инвертора, и знаковым входом первого накапливающего сумматора, первую группу логических элементов ИЛИ и второй накапливающий сумматор, отличающееся тем, что, с целью повышения точности измерения ортогональных составляющих сигнала, в него введены фильтр, второй регистр, третья, четвертая, пятая, шестая, седьмая и восьмая группы логических элементов И, вторая группа логическюс элементов ИЛИ, второй логический элемент ИЛИ, второй инвертор и блок управления, причем выход фильтра соединен с входом аналого-цифрового преобразователя, выходы блока преобразования которого соединены с входами второго регистра, прямые и инверсные выходы которого соединены с первыми входами восьмой группы элементов И и первыми входами третьей группы элементов И, вторые входы элементов И восьмой группы соединены с первым выходом блока управления, второй выход которого соединен с вторыми входами элементов И первой группы, выходы которых соединены с первыми i входами элементов ИЛИ второй группы, вторые входы которых соединены с вы(Л ходами элементов И восьмой группы, а выходы - с первьми входами элементов И пятой группы, выходы которых соединены с входами второго накапливающего сумматора, первые входы элементов И четвертой группы соединены с первыми входами элементов И первой.группы, вторые входы - с третьим выходом блока управления, а выходы - с первыми со входами элементов ИЛИ первой группы, вторые входы которых соединены с вы.ходами элементов И третьей группы, эо вторые входы которых соединены с чет-вертым выходом блока управления, пятый выход которого соединен с вторым входом элемента И седьмой группы, первый вход которого соединен с прямым выхо дом знакового разряда первого регистра, а шестой - с вторым входом другого элемента И седьмой группы, перВ.ЫЙ вход которого соединен с инверсным выходом знакового разряда первого регистра, выходы элементов И седьмой группы соединены с входами второ

Изобретение относится к измеритель-г ной технике с применением цифровой фильтрации.

Известно устройство дпя измеренш ортогональных составляющих сигнала, 5 содержащее аналого-цифровой преобразователь, два регистра, два накапливающик сумматора, блок управления, соединенный с аналого-цифровым преоб разователем, блок сдвига информации, О блок анализа знака, три сумматора, два блока инверсных кодов, блок фор- мирования признака знака и два добавочных блока сдвига, причем информационный выход аналого-цифрового 5 преобразователя соединен с входами бло|са сдвига информации и блока формирования признака сдвига, выход которого соединен с управляющим входом блока сдвига информации через второй 20 регистр с управляющими входами первого и второго добавочных блоков сдвига, выход, блока сдвига информации через первый регистр соединен с первым входом первого сумматора, прямые 5 и инвертированные выходы первого и второго сумматоров соединены соответственно -с входами первого и второго блоков инверсии кодов, выходы которых подсоединены соответственно к 30 входам первого и второго добавочных блоков сдвига и первым входам первого

2

и второго сумматоров, выходы первого и второго добавочных блоков сдвига соединены соответственно с вторыми входами второго и первого сумматоров и информационными входами первого и второго накапливающих сумматоров, знаковый выход аналого-цифрового преобразователя присоединен к одному из входов блока анализа знака, второй вход которого соединен с вторым выходом блока управления, а выход подсоединен к знаковым входам первого и второго блоков инверсии кодов первог и второго накапливающих сумматоров, третий и четвертый выходы блока управления присоединены соответственно к управляющим входам второго регистр и через последовательно соединенные третий сумматор, выход которого соединен с входом, и блок формирования признака знака подсоединены к управляющим входам первого и второго блоков инверсии кодов 111. Недостатком устройства является высокая степень сложности.

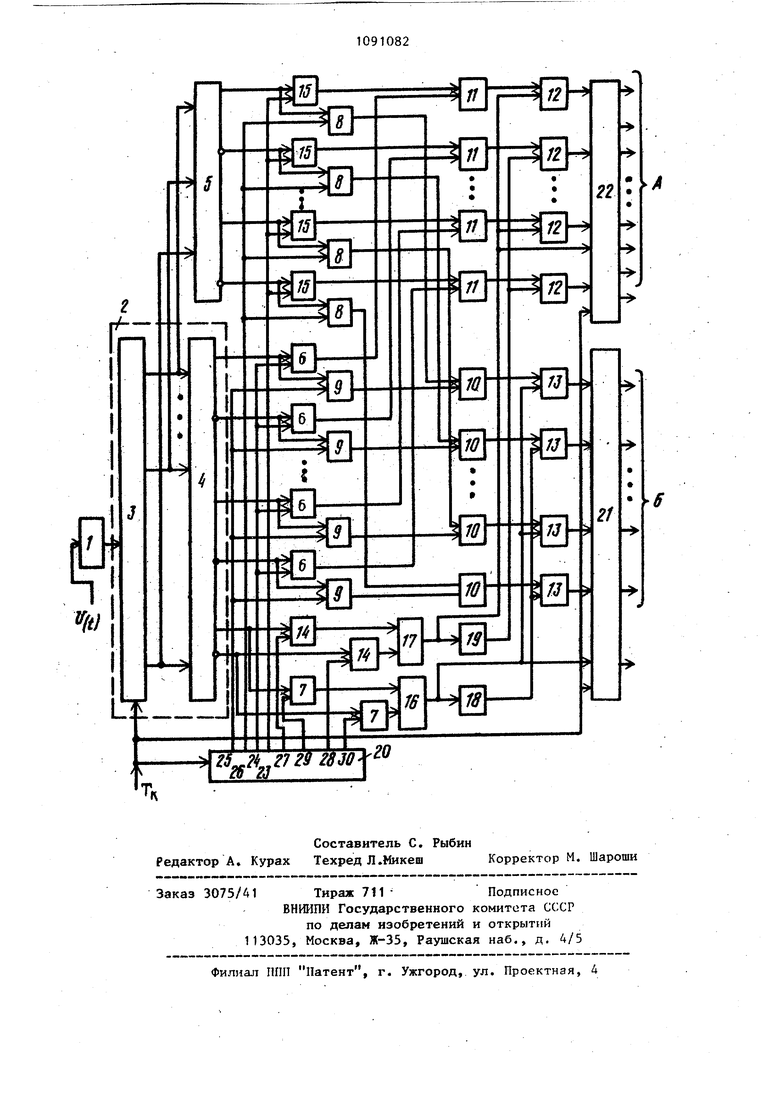

Наиболее близким по технической сущности к изобретению является устройство для измерения ортогональных составляющих сигнала, содержащее аналого-цифровой преобразователь, :состоящий из последовательно соединенных блока преобразования и регистра. два накапливаюилх сумматора, счетчик на двух триггерах, логические элементы ИЛИ по числу разрядов регистра и логические элементы И первой и второй групп по два на входе каждого элемента ИЛИ, соединенные первыми своими входами с прямыми и инверсными входами соответствующ1Х разрядов регистра, инвертор, включенный на выходе элемента ИЛИ второй группы, подключенный к прямому выходу знакового разряда, соединен с прямым выходом второго раз ряда счетчика, а другой элек1ент И вто рой группы - с инверсным выходом второго разряда счетчика, вторые входы всех элементов И первой группы, подключенных к прямым выходам остальных разрядов регистра, соединены с входом инвертора, а вторые входы остальных элементов И первой группы - с выходом инвертора, выходы всех элементов ИЛИ соединены с соответствующими входами обоих сумматоров, управляющий вход одного из которых соединен с прямьпч, а другого - с инверсным выходом первого разряда счетчика, причем счетный вход первого разряда счетчика соединен с входом тактовых импульсов аналого-цифрового преобразователя С21. Недостатком известного устройства является низкая точность измерения ортогональных составляющих сигнала, обусловленная тем, что исследуемый сигнал умножается не на гармонические а на знаковые функции и, следовательно, фильтрация высших нечетных гармоник устройством не производится. Цель изобретения - повьппение точности измерения ортогональных соетавляющих сигнала. Поставленная цель достигается тем что в устройство для измерения ортогональных составляющих сигнала, содержащее аналого-цифровой преобразователь, состоящийиз последовательно соединейных блока преобразования и первого регистра, прямые и инверсные выходь всех разрядов которого, кроме знакового, соединены с первыми входами логических элементов И первой груп пы, а выходы знакового разряда - с первыми входами логических элементов И второй группы, выходы которых соединены с входами первого элемента ИЛИ, выход которого соединен с входом первого инвертора, и знаковым входом первого накапливающего сумматора, первую группу логических элементов ИЛИ и второй накапливающий сумматор, введены фильтр, второй регистр, третья, четвертая, пятая, шестая, седьмая и восьмая группы логических элементов И, вторая группа логических элементов ИЛИ, второй логический элемент ИЛИ, второй инвертор и блок управления, причем выход фильтра соединен с входом аналого-цифрового преобразователя, выходы блока преобразования которого соединены с входами второго регистра, прямые и инверсные выходы которого соединены с первыми входами восьмой группы элементов И и первыми вкодами третьей группы элементов И, вторые входы элементов И восьмой группы сое- . Динены с первым выходом блока управ ления, второй выход которого соединен с вторыми входами элементов И первой группы, выходы которых соединены с первыми входами элементов ИЛИ второй группы, вторые входы которых соединены с выходами элементов И восьмой группы, а выходы - с первыми входами элементов И пятой группы, выходы коTopbjx соединены с входами второго накапливающего сумматора, первые входы элементов И четвертой группы соединены с первыми входами элементов И первой группы, вторые входы - с третьим выходом блока управления, а выходы - с первыми входами элементов ИЛИ первой группы, вторые входы которых соединены с выходами элементов И третьей группы, вторые входы которых соединены с четвертым выходом блока управления, пятый выход которого соединен с вторым входом элемента И седьмой группы, первый вход которого соединен с прямым выходом знакового разряда первого регистра, а шестой с вторым входом другого элемента И седьмой группы, первый вход которого соединен с инверсным выходом знакового разряда первого регистра, выходы I элементов И седьмой группы соединены с входами второго элемента ИЛИ, выход которого соединен с знаковым входом второго накапливающего сумматора и с вторым инвертором, седьмой выход блока управления соединен с вторым входом элемента И второй группы, первый вход которого соединен с прямым выходом знакового разряда первого регистра, второй вход другого элемента И второй группы соединен с восьмым выходом блока управления, вход которого Соединен с входом тактовых импульсов аналого-цифрового преобразователя и тактовыми входами накапливающие сумматоров, выход.второго элемента ИЛИ соединен с вторыми входами тех элементов И пятой группы, к первым входам которых череэ элементы И восьмой группы и элементы ИЛИ второй группы подключены прямые выходы разрядов второго регистра, с вторыми входами остальных элементов И пятой группы соединен выход второго инвертора, выходы элементов ИЛИ первой группы соединены с первыми входами элементов И шестой группы, выходы которых соединены с входами первого накапливающего сумматора, вход первого инвертора соединен с вторыми входами тех элементов И шестой группы, к первым входам которых через элементы И четвертой группы и элементы ИЛИ первой группы подключены прямые выходы всех разрядов, кроме знакового, первого регистра, выход первого инвертора соединен с вторыми входами остальных элементов И шестой группы. На чертеже приведена структурная электрическая схема устройства. Аппарат состоит из фильтра 1, выход которого соединен с входом аналого-цифрового преобразователя 2, с входящими в него последовательно сое диненными, блоком 3 преобразования и первым регистром 4, второго регистра 5, первой группы логических элементо И 6, второй группы логических элемен тов И 7, третьей группы логических элементов И 8, четвертой группы логи ческих элементов И 9, первой группы логических элементов ИЛИ 10, второй группы логических элементов ИЛИ 11, пятой группы логических элементов И 12, шестой группы логических элементов И 13, седьмой группы логических элементов И 14, восьмой группы логических элементов И 15, первого логического элемента ИЛИ 16, второго логического элемента ИЛИ 17, первого инвертора 18, второго инвертора 19, блока 20 управления, первого и второ го накапливающих сумматоров 21 и 22, причем выходы блока 3 преобразования соединены с входами второго регистра 5, прямые и инверсные выходы которого соединены с первыми входами эле ментов И 15 восьмой группы, вторые входы которых соединены с первым выходом 23 блока 20 управления, второй выход 24 которого соединен с вторыми входами элементов И 6 первой группы, первые входы которых соединены с прямыми и инверсными выходами первого регистра 4, а выходы - с вторыми входами второй группы элементов ИЛИ 11, первые входы которых соединены с выходами элементов И 15 восьмой группы, а выходы - с первыми входами элементов И 12 пятой группы, выходы которых соединены с входами второго накапливающего сумматора 21, третий выход 25 блока 20 управления соединен с вторыми входами элементов И 9 четвертой группы, первые входы которых соединены с первыми входами элементов И 6 первой группы, а выходы - с первыми входами элементов ИЛИ 10 первой группы, вторые входы которых соединены с выходами элементов И 8 третьей группы, первые входы которых соединены с первыми входами элементов И 15 восьмой группы, а вторые входы - с четвертым выходом 26блока 2d управления, пятый выход 27которого соединен с вторым входом элемента И 14 седьмой группы, первый вход которого соединен с прямым выходом знакового разряда, инверсный выход которого соединен с первым входом другого элемента И 14 седьмой группы, второй вход которого соединен с шестым выходом 28 блока 20 управле- ния, выходы элементов И 14 седьмой группы соединены с входами второго элемента ИЛИ 15, выход которого соединен с знаковым входом второго накапливающего сумматора 22 и входом второго инвертора 19, седьмой выход 29блока 20 управления соединен с вторым входом элемента И 7 второй группы, первый вход которого соединён с прямым выходом знакового разряда первого регистра 4, восьмой выход 30блока 20 управления соединен с вторым входом элемента И 7 второй группы, первый вход которого соединен с инверсным выходом знакового разряда первого регистра 4, выходы элементов И 7 второй группы соединены с входами первого элемента ИЛИ 16, выход которого соединен с знаковым входом первого накапливающего сумматора 21, ВХОДОМ первого инвертора 18, вход второго инвертора 19 соединен с вторыми входами тех элементов И 12 пятой группы, к первым входам которых через элементы И 15 восьмой группы и элементы ИЛИ 11 второй группы подключены прямые выходы второго регистра 5, выход второго инвертора 19 соединен с , вторыми входами остальных элементов И 12 пятой группы, выходы элементов ИЛИ 10 первой группы соединены с первыми входами элементов И 13 шестой группы, выходы которых соединены с входами первого накапливающего сумматора 21, с вторыми входами тех элементов И 13 шестой группы, к первым входам которых через элементы И 9 четвертой группы и элементы ИЛИ 10 первой группы подключены прямые выходы всех разрядов, кроме знакового, первого регистра 4 соединен вход первого инвертора 18, выход которого соединен с вторыми входами остальных элементов И 13 шестой группы, тактовый вход аналого-цифрового преобразователя соединен с тактовыми входами блока 20 управления и накапливающих сумматоров 21 и 22. Устройство работает следующим образом. На вход фильтра 1, в качестве которого можно использовать последова- 5 тельно- соединенные интеграторы, поступает сигнал U.tV После интегрирования этот сигнал поступает на вход аналого-цифрового преобразователя 2, на другой вход которого поступает серия импульсов Тц, определяющих моменты взятия выборок сигнала. Получаемый на выходе блока 3 преобразования п. разрядный код модуля Хц, соответствующий величине выборки сигнала и ее знаку, подается параллельно на первый 4 и второй 5 регистры, где запоминается на время .t. Причем на втором регистре 4 п -разрядный код сдвинут на один разряд в сторону младше- до го разряда. Такое соединение регистров 4 и 5 позволяет получить на прямых выходах регистра 4 прямой код числа Х(, на инверсных выходах регистра 4 - обратный код числа Ху, на выходах второго регистра 5 - прямой код числа -, а на инверсных выходах регистра 5 - обратный код числа . Последовательность импульсов одновременно подается и на вход блока 20 управления. Последний имеет восемь выходов. Появление сигнала на выходе 23 соответствует тому, что синусоидальный сигнал должен быть взят с весом 0,5, а появление сигнала на выходе 24 соответствует тому, что синусоидальный сигнал дожен быть взят с весом 1. Появление сигнала на выхону с хо ну с ра да зн ка сл в де 25 сбответстйует тому, что косисоидальный сигнал должен быть взят весом 1., а появление сигнала на выде 26 соответствует тому, что косисоидальный сигнал дожен быть взят весом 0,5. Выходы 27 и 28 блока упвления определяют знаки синусоильного сигнала, а выходы 29 и 30 аки косинусоидального сигнала. Чередование сигналов на выходе блоуправления в зависимости от поедовательности импульсов приведено таблице. Из таблицы ввдно, что гармонические функции заменены ступенчатыми и через 12 импульсов сигналы на выходе блока управления начинают повторяться. Чтобы устройство осуществляло только логические операции, введен регистр 5 и число на его выходе в два раза меньше, чем число на выходе регистра 4. Это позволяет учитывать весовые коэффициенты синуса и косинуса путем подключения логических элементов к регистру 4 или регистру 5, а на выходе блока 20 управления оперировать только двумя уровнями сигналов. По сравнению с прототипом, где уровни гармонических сигналов одинако вы, предлагаемое устройство првьшает точность измерения ортогональных составляющих сигнала. Действительно, разложение в ряд Фурье ступенчатого сигнала, который используется в прото типе, вносит ошибку за счет появления нечетных гармоник 3, 5, 7, 9 и т.д. При разложении в ряд Фурье двухуровневого сигнала, который осзществлен в предлагаемом устройстве, 3 и 9 .гармоники исчезают, что по сравнению с прототипом повивает точность определения ортогональных составляющих сигнала. Для уменьшения ошибок от 5 и более высоких гармоник служит фильтр 1, выполненньй на интеграторах. Коэффициент усиления интеграторов выбран так, чтобы он был равен 1 на частоте определения ортогональной составляющей сигнала. Поэтому ортогональная состав ляющая, подлежащая определению, проходит через фильтр 1 без амплитудных искажений, а более высокие гармоники ослабляются. Например, при однократном интегрировании пятая гармоника уменьшается в пять раз, а фаза исследуемого сигнала поворачивается в сторону отставания на 90 , при двух интеграторах пятая гармоника уменьшается в 25 раз, а фаза поворачивается на 180 Чтобы ошибки от высвшх гармоник сделать незначительными, а работу логического устройства более простой, фильтр 1 должен содержать четыре интегратора. Такое выполнение блока относительно опорных сигналов не вносит ни амплитудных, ни фа- 45 зовых искажений, а пятая гармоника ослабляется в 625 раз. Как было указано, на прямых выходах второго регистра 5 появляется „„ « V УО прямой код числа , а на инверсны выходах - обратный код числа Хк/2. Прямой код - подается на входы нечетных номеров логических элементов И 15 и И 8 восьмой и третьей групп, а обратный код числа подается на входы четных номеров логических эле. ментов И 15 и И 8 восьмой и третье групп. На второй вход логических элементов И 15 подается сигнал от выхода 23,блока 20 управления, а на второй вход логических элементов И 8 сигнал с выхода 26 блока управления. Таким образом, на. выходах нечетных номеров логических элементов И 15 формируется прямой код -ь-, а на выходах четных Номеров логических элементов И 15 - обратный код . Код с выхода логических элементов И 15 идет на определение синусоидальной составляющей гармонического сигнала. Нечетные номера логических элементов И 8 формируют прямой код т, а четные номера логических элементов И 8 - обратнь1й код -j, который идет на формирование косинусоидальной составляющей гармонического сигнала. Аналогичным образом работают логические элементы И. 6 и И 9 и первый регистр 4. Прямой код числа Х подается на входы нечетных номеров логических элементов И 6 и И 9, а обратный код числа - на входы четных номеров логических элементрв И 6 и И 9. На второй вход логических элементов И 6 подается сигнал от входа 24 блока управления, а на второй вход логических элементов И 9 - сигнал с выхода 25 блока управления. Присутствие сигналов на выходах 24 и 25 блока управления свидетельствует о том, что выборку сигнала следует, брать с весом, равным единице, а появление сигналов на выходах 23 и 26 блока управления свидетельствует о том,, что выборку сигнала следует брать с весом 0,5. Таким образом на выходах нечетных номеров логических элементов И 6 формируется прямой код Xv, а на выходах четных номеров логических элементов И 6 - обратньш код числа Х«, который идет на определение синусоидального сигнала. Нечетные номера логических элемё нтов И 9 формируют прямой код Хк,, а четные номера логических элементов И 9 - обратный код числа Yit, который идет на определение косинусоидальных составляющих сигнала, Выходы логических элементов И 15 и И 6 объединены логическими элементами ИЖ 11, а выходы логических элементов И 8 и И 9 - логическими элементами ИЛИ 10. Такое объединение позволяет сформировать в зависимости от сигналов блока управления прямой код чисел Хк или X,,/2, или обратный 1110 код этих же чисел на выходе логичеЬких элементов ИЛИ 11, которые формируют синусоидальную составляющую сигнала, или сформировать эти же сиг налы на выходе логического элемента ИЛИ 10, которые формируют косинусоидальную составляющую сигнала. Ввод синусоидальной составляющей сигнала в накопительный сумматор 22 осуществляется через пятую группу логических элементов И 12, а ввод Косинусоидальной составляющей сигнал в накапливающий сумматор 21 - через шестую группу логических элементов И 13. На вход нечетных номеров логических элементов И 12 подается признак знака от второго логического элемента ИЛИ 17, а на входы четных номеров логических элементов И 12 .инвертированный признак знака, т.е. сигнал с выхода логического элемента ИЛИ 17 подается на инвертор 19, а затем на входы четньпс номеров логиче ких элементов И 12. Логические элементы И 14 и логический элемент ИЛИ 17-реализуют операцию равнозна ;ности для синусоидальной составляюще сигнала, а логические элементы И 7 и логический элемент ИЛИ 16 - операцию равнозначности для косинусондаль ного сигнала. Таким образом, если знаки синусои дального и анализируемого сигнала совпадают, то на выходе логического элемента ИЛИ 16 появляется сигнал. Это значит, что прямой код числа Ху и t вводится в нака:пливающий сумма тор 22 после прихода импульса f на управляющий вход сумматора. Если зна ки синусоидального и анализируемого 2 сигнала разны, то появляется сигнал на выходе инвертора 19 и в накапливающий суьматор 22 вводится обратный код после прихода управляющего импульса. Следует учесть, что на выходе 27 блока 20 управления появляется логическая единица, когда синусоидальный сигнал положительный, а на выходе 28 блока 20 управления - сигнал, когда синусоидальный сигнал отрицательный. Аналогично работает блок равнозначности для определений косинусои:дальной составляющей сигнала. «На логические элементы И 15 кроме кода знака исследуемого сигнала по выходу 29 и 30 блока 20 управления подаются знаки косинуса. При одинаковых знаках исследуемого сигнала и косинуса на выходе логического элемента ИЛИ 16 появляется логическая единица, а при разных знаках - единица на выходе инвертора 18. С игналы с выхода логического элемента ИЛИ 16 и инвертора 18 управляют логическими элементами И 13. При появлении сигнала HSI выходе элемента ИЛИ 16 в накапливающай сумматор 22 вводится прямой код числа Хк или , а при появлении сигнала на выходе инвертора 18 в это же сумматор под действием импульсной последовательности вводится обратный код. Таким образом, в предлагаемом устройстве точность измерения ортогональных составляю1цих сигнала значительно увеличивается, при этом конструкция аппарата осталась достаточно несложной.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 759968, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство измерения ортогональных составляющих сигнала | 1976 |

|

SU646262A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-05-07—Публикация

1982-08-05—Подача