код ,, mod 3, дополнительрплй мультиплексор 20 выделяет n-j кодов 3 и К код z mod 3, уточняемый на сумматоре 22 по модулю три, формируемый узлом свертки 18 и дополните1

Изобретение относится к области вычислительной техники и является усовершенствованием устройства по

авт.св. № 1208551.

Целью изобретения является повьпиение достоверности функционирования устройства.

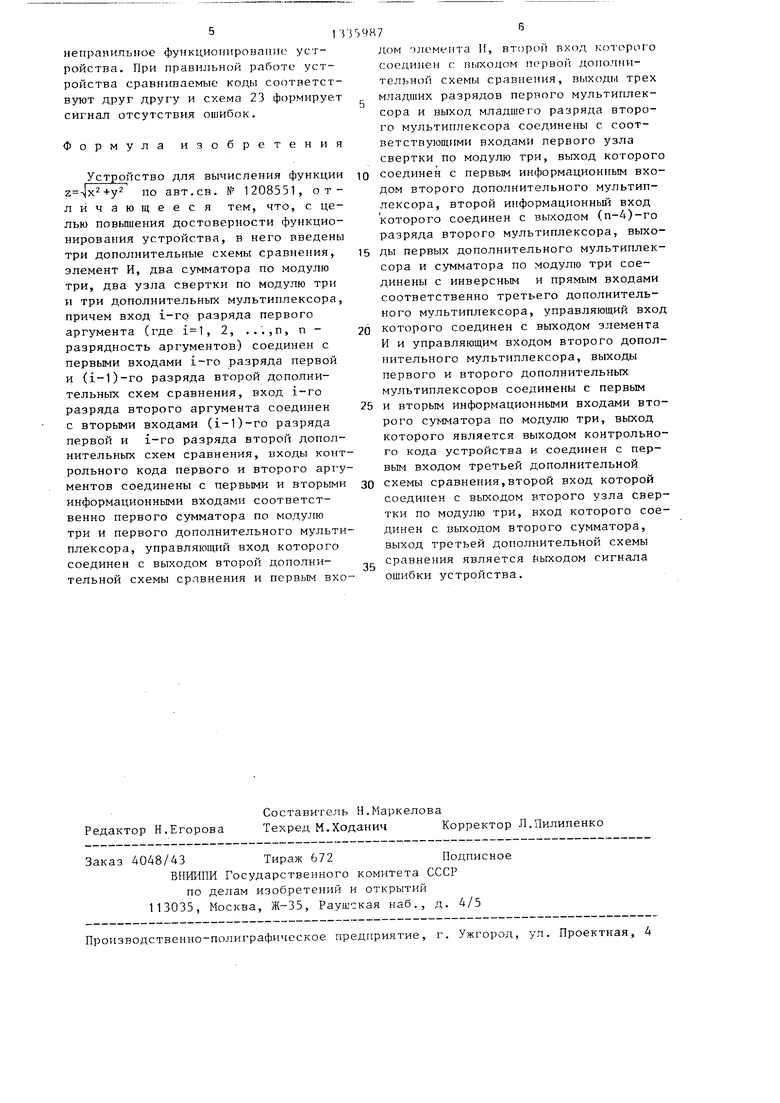

На чертеже приведена функциональная схема устройства.

Устройство содержит входы 1-2 первого и второго аргументов, первую и вторую схемЕ 1 3 и 4 сравнения, четыре мультиплексора 5-8, сумматоры 9 и 10 вычитатель 11, выход 12 значения фун- кции, первую и вторую дополнительнЕ 1е схемы 13 и 1А сравнения, первый сумматор 15 по модулю три, элемент И 16 первьш дополнительный мультиплексор 17, первый узел 18 свертки по модулю три, второй и третий дополнительные мультиплексоры 19 и 20, второй узел 21 свертки по модулго три, второй сумматор 22 по модулю три, третью дополнительную схему 23 сравнения, входы 24 и 25 контрольного кода первого и второго аргументов, вьжод 26 сигнала ошибки, выход 27 контрольного кода.

Устройство вычисляет функцию z

, аппроксимируя ее в соответ- зо ствии с формулой

А„„,,+ (2-з+2-) А.

если 2А„ц„ А.

+ 2 А.

если 2А„,

.()Л,„„,, -.,„„

1 Де (1х , |у| ) ;

А„,„ min ( 1x1 , iyl ) . Устройство работает следующим образом.

В начальный момент времени прямые коды первого х и второго у аргументов поступают через входы 1 и 2 на первьш вход схемы 3 сравнения, nepBbni информационный вход первого мультиплексора 5, второй информационный вход в то- рого мультиплексора 6 и второй вход

Jlbllliir-f МУЛЬ ГППЛСЬ 1-. t Xf M. l 24

срапнинлет утч)Ч11 м1иы; 1 ьол. /: пик 3 с .) )ii кода , il f- f Py - мс й узлом 21 сг ертки по м(хчу. ;1о ч ри, и ныраба- TF.maeT . i ошибки. I нл.

схемы 3 сравнения, второй информационный вход первог о ,yльтиплeкcopa 5, первЕ)1Й информациоиньБ вход мультиплексора 6. При этом схема 3 сравнения вырабатывает сигнал., определяющий своим значением бо льший из сравниваемых кодов. Этот сигнал поступает на управляющие входы мультиплексоров 5 и 6, в результате чего на их выходы транслируются соответствен1 о макси- мальньш ,., и минимальный А из кодов аргументов.

Код поступает с выхода мультиплексора 5 на первую и, с монтажным сдвигом на три разряда в сторону младших разрядов, на вторую (вычитающую) 1 руппу входов вычитателя 1 1 . При этом на выходе вычитателя 11 формируется код а() .

Код А„„н поступает с выходов мультиплексора , 6 на первую и вторую группы входов сумматора 9 с монтажным сдвигом соответственно на 3 и 4 разрядов в сторону младших разрядов. При этом на выходе сумматора 8 формируется код Ь( ) А.

Кроме того, коды А и поступают также на вход1л схемы 4 сравнения соответственно на первую группу входов и, с монтажным сдвигом на один разряд в сторону старших разрядов, на вторую группу входов. При этом схема 4 сравнивает между собой коды А , и 2А.. . Результат этого сравне Сд U, И

НИН с выхода схемы 4 поступает на управляющие входы мультиплексоров 7 и 8.

На информационные входы мультиплексора 7 поступают соответственно код с выхода первого сумматора 9 и сдвинутый монтажно на один разряд в сторону младших разрядов код А, с выходов второго мультиплексора 6. Под действием управления на выход мультиплексора 13 транслируется код

Ь ПР 2 Л,,„, Л„.,.

Ч.,-.

ГГ 5 }87

код присумматор 15 контрольный

код К(|х|+ |у1 ) mod 3.

На первый и второй информацнонн 1е входы мультиплексора 8 поступают соКроме того, контрольные коды kx и ky поступают на информационные в ды мультиплексора 17, на управляющ вход которого поступают сигнал с хода схемы 14 сравнения.

с выхода мульOTBeTCTBcmfo код Л „ типлексора 5 и код а с выхода вычита- теля 8. Под действием управления на выход мультиплексора 16 транслируется

код при 2А„ „ьА„„ или код а при 2А, А .

Коды с выходов мультиплексоров 7 и 8 поступают на входы сумматора 17, который определяет результат ,+ (2-з+2 ) А

или 2(Ь2-з).

Код результата поступает на выход 1 2.

Проверка функционирования устройства осуществляется путем контроля по модулю три. Из выражения (1) следует, что

н А„„

А„,„ для 2А, А„,.

,jmod 3, если 2А

WHH - Mate

н-Д

ин мак

)mod 3,если А, mod 3

(A

Действительно, поскольку 2 1, а 2 mod или, что то же самое: 2 mod (п - целое число), то () mod и b mod 3 0, т.е. для 2А„ „ёА„а г„, A, , mod 3, В случае 7 А„ц( 1-2 ) mod и 3, следовательно 2„.-(А„,н-А.,..,.)mod 3 или.

мин

- (Ixl + |yj);

шосЗ т ма1;о

что то же самое, X mod 3.

Для контроля функционирования устройства прямые коды аргументов к и у поступают с входов устройства . 1 и 2 также на входы схем 13 и 14 сравнения. Причем на первые группы входов схем 13 и 14 поступают соответственно прямые коды аргументов х и у, а на вторые группы входов этих схем приходят прямые коды аргументов х и

у, монтажно сдвинутых на один разряд 45 младший). Под действием сигнала с

в сторону старших разрядов. Схемы 13 и 14 вырабатывают на выходе единичное значение соответственно при и |у| и ноль в противных случаях. Сигналы с выходов схем 13 и 14 сравнения поступают на входы элемента И, на выходе которого формируется единичное значение сигнала, если ,„ ,j, и нулевое значение в противном случае.

50

55

выхода элемента 7 на выход мультип лексора 19 транслируется код попра ки, соответствующий соотношению ве личины 2А„, и А„.

Код поправки с выхода мультипле сора 19 и код с выхода мультиплекс ра 20 поступают на входы сумматора 22 по модулю три, формирующего кон рольный код результата.

Схема 23 сравнивает поступающие на ее входы коды и формирует на вы ходе сигнал контроля. Этот сигнал принимает значение Ошибка при не соответствии кодов, что указывает

Через входы 24 и 25 на входы сумматора 15 поступают контрольные коды mod 3, ky |у| mod 3. При этом

0

5

0

5

0

5

0

Кроме того, контрольные коды kx и ky поступают на информационные входы мультиплексора 17, на управляющий вход которого поступают сигнал с выхода схемы 14 сравнения.

Для случая 2А этот сигнал принимает нулевое значение при 1у| |х| и единичное значение при , а выход мультиплексора 17 принимает значение контрольного кода kx или ky, равного 3.

Код К с выхода сумматора 15 по модулю три и код 3 с выхода мультиплексора 17 поступают на информационные соответственно инверсньпй и прямой выходы мультиплексора 20, на управляющий вход которого поступает сигнал с выхода элемента 18.. При этом выход мультиплексора 20 принимает значение кода - К, если и значение кода А mod 3, если 2А„,„ fcA.

Полученный код может быть отличен от кода Z д, в силу отбрасывания . младших разрядов при сдвиге чисел.

Отбрасываемые разряды учитываются для случая 2А,, узлом 18 свертки по модулю три, на входы которого поступают три младших разряда кода макс младший разряд кода А . Узел 18 формирует код поправки Л1

-(АМИН Г1 - Амакс{1 - 3 2-з)х xmod 3.

Для случая поправка на отбрасываемые разряды определяется как

(A„, , 1 «mod (, 1 4 -А„„, 1 т 3) mod 3

-АМИЧ (. ™od 3,

т.е. поправка д2 образуется четвертым разрядом кода А.,. (1 разряд младший). Под действием сигнала с

выхода элемента 7 на выход мультиплексора 19 транслируется код поправки, соответствующий соотношению величины 2А„, и А„.

Код поправки с выхода мультиплексора 19 и код с выхода мультиплексора 20 поступают на входы сумматора 22 по модулю три, формирующего контрольный код результата.

Схема 23 сравнивает поступающие на ее входы коды и формирует на выходе сигнал контроля. Этот сигнал принимает значение Ошибка при несоответствии кодов, что указывает на

г

непранильное фулкциоииронание устройства. При правильной работе устройства сравниваемые коды соответствуют друг друг у и схема 23 фо1)мирует сигнал отсутствия ошибок.

Формула изобретения

Устройство для вычисления функции 2 л|х2+у2 по авт.св. № 1208551, отличающееся тем, что, с целью повышения достоверности функционирования устройства, в него введены три дополнительные схемы сравнения, элемент И, два сумматора по модулю три, два узла свертки по модулю три и три дополнительных мультиплексора, причем вход i-ro разряда первого аргумента (где , 2, ...,п, п - разрядность аргументов) соединен с первыми входами i-ro разряда первой и (i-l)-ro разряда второй дополнительных: схем сравнения, вход i-ro разряда второго аргумента соединен с вторыми входами (i-l)-ro разряда первой и i-ro разряда второй дополнительных схем сравнения, входы контрольного кода первого и второго аргументов соединены с первыми и вторыми информационными входами соответственно первого сумматора по модулю три и первого дополнительного мультиплексора, управляющий вход которого соединен с выходом второй дополнительной схемы сравнения и первым вхоРедактор Н.Егорова

Составитель Н.Маркелова

Техред М.Ходанич Корректор Л.Пилипенко

Заказ 4048/43 Тираж 672Подписное

В 1ИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5487

дом .элемента И, второй вход коп орог о соединен с п.гходом первой дополнительной схемы сравнения, выходы трех

младших разрядов первого мультиплексора и выход младшего разряда второго мультиплексора соединены с соответствующими входами первого узла свертки по модулю три, выход которого

10 соединен с первым информационным входом второго дополнительного мультиплексора, второй информационньп вход которого соединен с выходом (п-А)-го разряда второго мультиплексора, вьгхо15 ДЬ1 первых дополнительного мультиплексора и сумматора по модулю три соединены с инверсным и прямым входами соответственно третьего дополнительного мультиплексора, управляющий вход

20 которого соединен с выходом злемента И и управляющим входом второго дополнительного мультиплексора, выходы первого и второго дополнительных мультиплексоров соединены с первым

25 и вторым информационными входами второго сумматора по модулю три, ВЬЕХОД которого является выходом контрольного кода устройства и соединен с первым входом третьей дополнительной

30 схемы сравнения,второй вход которой соединен с выходом второго узла свертки по модулю три, вход которого соединен с выходом второго сумматора, выход третьей дополнительной схемы сравнения является йькодом сигнала

35

ошибки устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1987 |

|

SU1425678A1 |

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1332321A2 |

| Устройство для контроля по модулю три умножения комплексных чисел | 1987 |

|

SU1434438A1 |

| Устройство для контроля по модулю умножения комплексных чисел | 1985 |

|

SU1285479A1 |

| Устройство для определения модуля трехмерного вектора | 1986 |

|

SU1388854A2 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1444750A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1608653A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

Изобретение относится к области вычислительной техники, является усовершенствованием изобретения по а.с. № 1208551 и позволяет вычислить функцию -jx +у , аппроксимируя ее в соответствии с формулой ГА ..,„( 2-3+2- )-А watc v - )

| Устройство для вычисления функции @ | 1984 |

|

SU1208551A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-16—Подача