Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях автономно или в качестве функционального расширителя в составе больших ЭВМ.

Цель изобретения - сокращение аппаратных затрат за счет формирования контрольных сигналов без использования контрольньк разрядов аргументов.

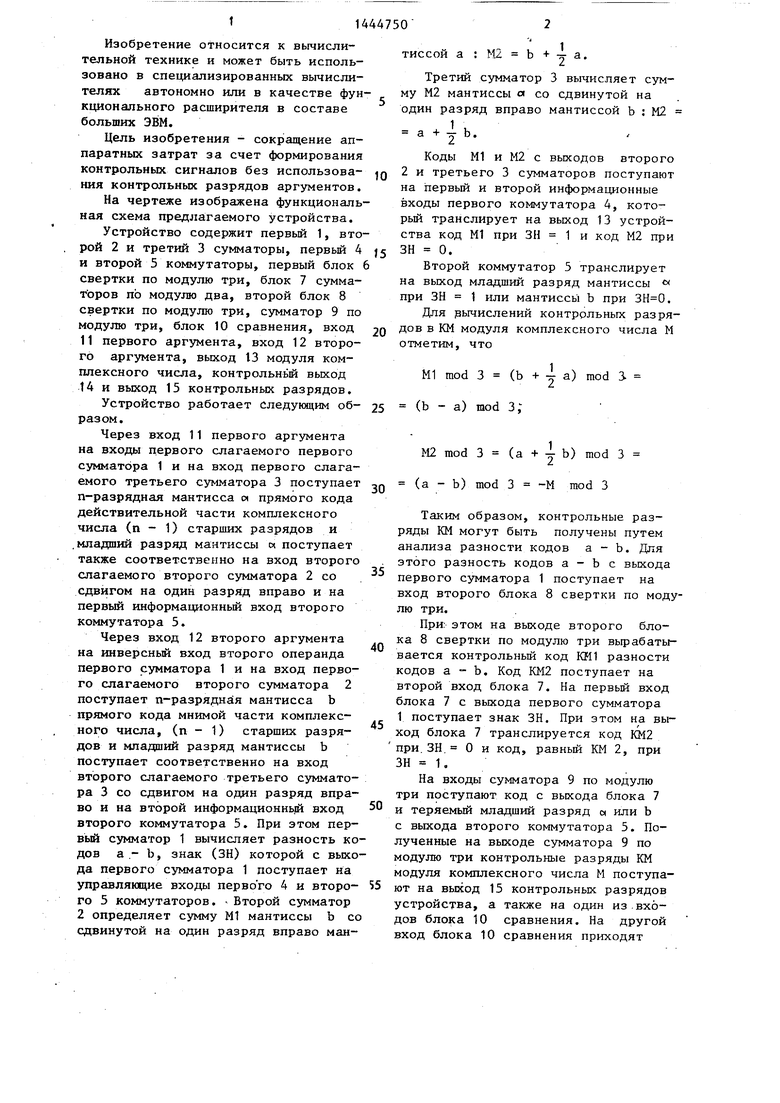

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит первьй 1, второй 2 и третий 3 сумматоры, первый 4 и второй 5 коммутаторы, первый блок свертки по модулю три, блок 7 сумматоров по модулю два, второй блок 8 свертки по модулю три, сумматор 9 по модулю три, блок 10 сравнения, вход 11 первого аргумента, вход 12 второго аргумента, выход 13 модуля комплексного числа, контрольной выход 14 и выход 15 контрольных разрядов.

Устройство работает следующим образом.

Через вход 11 первого аргумента на входы первого слагаемого первого сумматора 1 и на вход первого слагаемого третьего сумматора 3 поступает п-разрядная мантисса « прямого кода действительной части комплексного числа (п - 1) старших разрядов и .младший разряд мантиссы w поступает также соответственно на вход второго слагаемого второго сумматора 2 со сдвигом на один разряд вправо и на первый информационньй вход второго коммутатора 5.

Через вход 12 второго аргумента на инверсньй вход второго операнда первого сумматора 1 и на вход первого слагаемого второго сумматора 2 поступает п-разрядная мантисса b прямого кода мнимой части комплексного числа, (п - 1) старших разрядов и младший разряд мантиссы b поступает соответственно на вход второго слагаемого третьего сумматора 3 со сдвигом на один разряд вправо и на второй информационньй вход второго коммутатора 5. При этом первый сумматор 1 вычисляет разность кодов а.- Ь, знак (ЗН) которой с выхода первого сумматора 1 поступает на управляющие входы перво го 4 и второго 5 коммутаторов. - Второй сумматор 2 определяет сумму Ml мантиссы b со сдвинутой на один разряд вправо мантиссой а : М2 b + у а.

Третий сумматор 3 вычисляет сумму М2 мантиссы а со сдвинутой на один разряд вправо мантиссой b ; М2

а + Y Ь.

Коды Ml и М2 с выходов второго 2 и третьего 3 сумматоров поступают на первьш и второй информационные входы первого коммутатора 4, кото- рьй транслирует на выход 13 устройства код Ml при ЗН 1 и код М2 при ЗН 0.

Второй коммутатор 5 транслирует на выход младший разряд мантиссы при ЗН 1 или мантиссы b при .

Для рычислений контрольных разря- Дов в КМ модуля комплексного числа М отметим, что

М1 mod 3 (b + - а) mod 3- (b - а) mod 3;

30

М2 mod 3 (а + -J b) mod 3 (а - b) mod 3 -М mod 3

Таким образом, контрольные разряды КМ могут быть получены путем анализа разности кодов а - Ь. Для этого разность кодов а - b с выхода первого сумматора 1 поступает на вход второго блока 8 свертки по модулю три.

При: этом на выходе второго блока 8 свертки по модулю три вьфабаты- вается контрольньш код КМ1 разности кодов а - Ь. Код КМ2 поступает на второй вход блока 7. На первьй вход блока 7 с выхода первого сумматора 1 поступает знак ЗН. При этом на выход блока 7 транслируется код Ш2 при.ЗН. О и код, равный КМ 2, при ЗН 1.

На входы сумматора 9 по модулю три поступают код с выхода блока 7 и теряемый младший разряд о или b с выхода второго коммутатора 5. Полученные на выходе сумматора 9 по модулю три контрольные разряды КМ модуля комплексного числа М поступают на выход 15 контрольных разрядов устройства, а также на один из входов блока 10 сравнения. На другой вход блока 10 сравнения приходят

ного числа М.

Блок 10 сравнения сравнивает контрольные разряды модуля комплексного

бами, и вырабатывает сигнал контроля, свидетельствующий о правильности функционирования устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1287151A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1193662A1 |

| Устройство для вычисления модуля комплексного числа | 1982 |

|

SU1104505A2 |

| Устройство для вычисления модуля комплексного числа | 1987 |

|

SU1508206A1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для контроля по модулю три умножения комплексных чисел | 1987 |

|

SU1434438A1 |

| Устройство для контроля умножения чисел по модулю | 1985 |

|

SU1259269A1 |

| Устройство для вычисления функции @ | 1986 |

|

SU1335987A2 |

| Устройство для вычисления модуля комплексного числа | 1982 |

|

SU1104505A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1193662A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1985-11-14—Подача