123314

Изобретение относится к вычисительной технике и может быть использовано в специализированных преобразователях координат с повышенной надежностью,5

Цель изобретения - повьппение достоверности вычисления модуля комплексного числа за счет, возможности аппаратного исправления константных одиночных неисправностей. 10

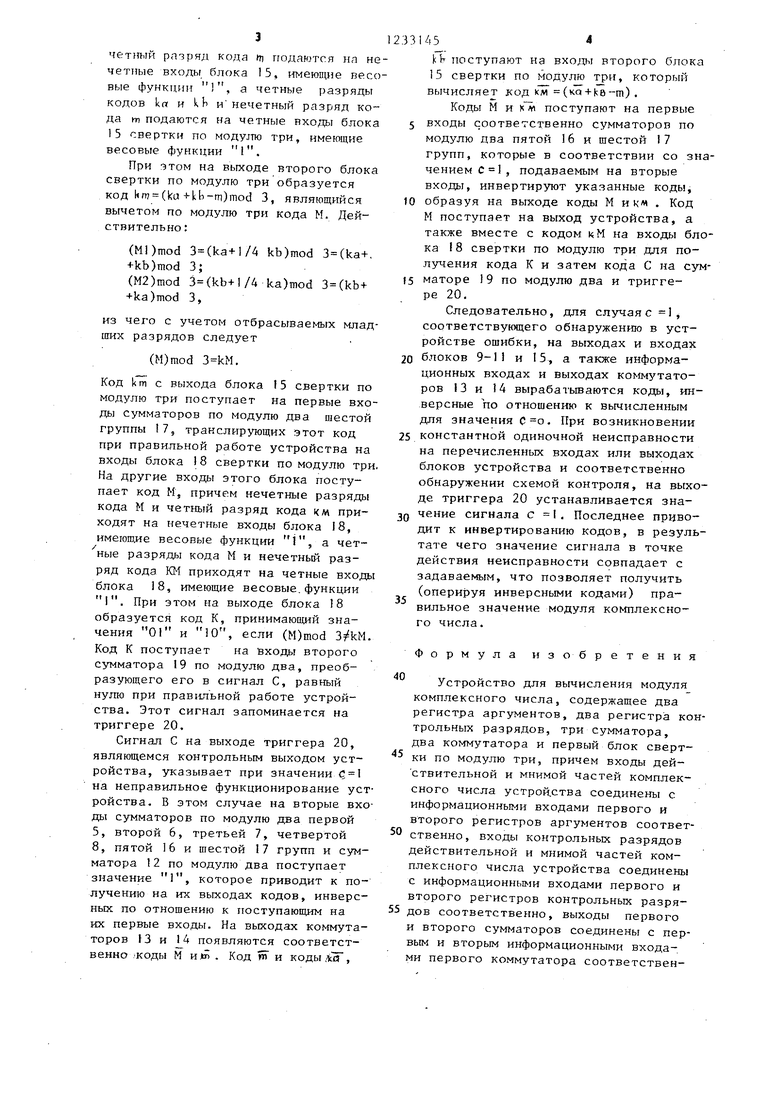

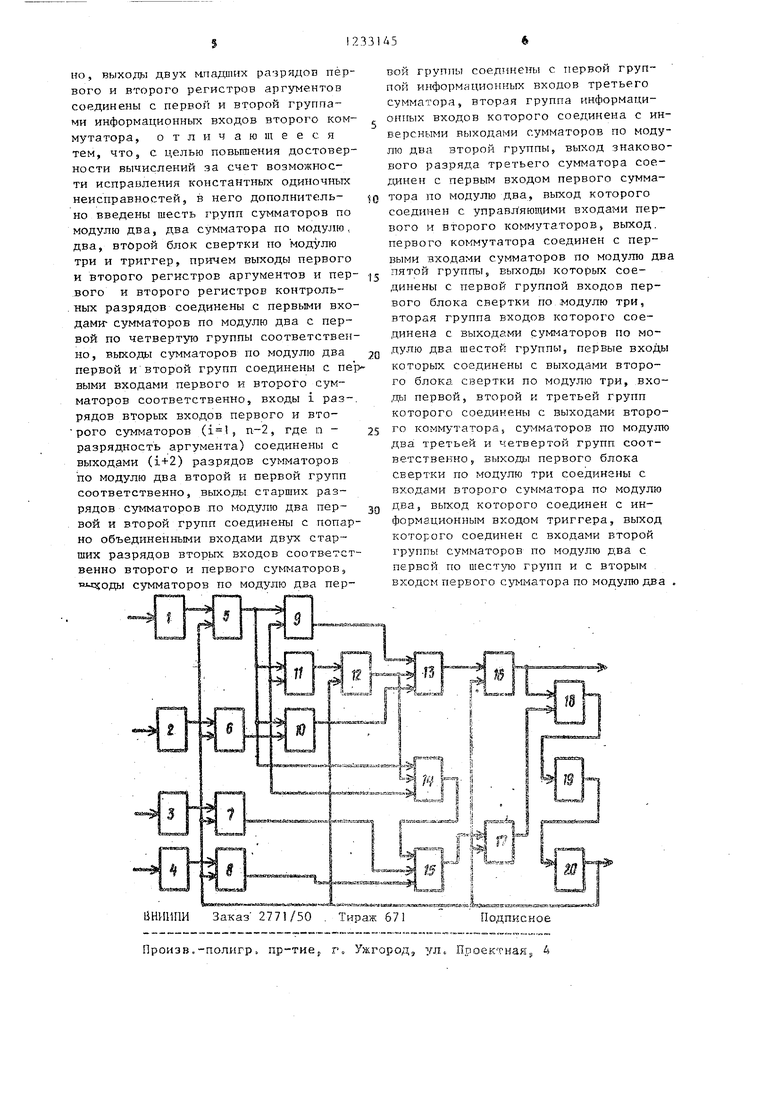

Устройство содержит первый 1 и второй 2 регистры аргументов, первый 3 и второй 4 регистры контрольных разрядов, первую 5, вторую 6, третью 7 и четвертую 8 группы сумма- )5 торов по модулю два, первый 9, второй 10 и третий 11 сумматоры, первый сумматор 12 по модулю два, первый 13 и второй 14 коммутаторы, второй блок 15 свертки по модулю 20 три, пятую 16 и шестую 17 группы сумматоров по модулю два, первый блок 18 свертки по модулю три, второй сумматор 19 по модулю два и 7 риг- гер 20.25

Устройство работает следующим образом s

В начальный момент времени в первый 1 и второй 2 регистры аргументов, первый 3 и второй 4 регистры зо контрольных разрядов заносятся соответственно п-разрядные мантиссы прямых кодов действительной С и мнимой Ъ составляющих комплексного числа и контрольные разряды по модулю три , Этих мантисс ka и kb. С выходов ре- гистров 1-4 коды а,Ь,ka и kb поступают на первые входы сумматоров по модулю два соответственно первой 5, второй 6, третьей 7 и четвертой В д групп. На вторые входы сумматоров по модулю два первой 5, второй 6, третьей 7, четвертой 8, пятой 16, тестой 17 групп и сумматора 12 по модулю два поступает сигнал контроля С ,с с выхода триггера 20. Группа сумматоров по модулю два состоит из сумматоров по модулю два, первые входы которых являются первыми входами . блока, вторые входы - вторыми .входами блока, а выходы - выходами группы. .

При этом на первьй и второй вход первого сумматора 9 поступают соответственно код действительной составляющей и (п-2) старших разрядов кода мнимой составляющей. На выходе первого сумматора 9 опредапяется

52

результат М сложения кола действительной состав11яющей со сдвинутым вправо на два разряда кодом мнимой составляющей, т.е.

М1-а-И/4Ь.

Два младших разряда Ь кода Ь подаются на первый информадионный вход второго коммутатора 14.

На первый и второй входы второго сумматора 0 поступают соответственно код мнимой составляющей и (п-2) старших разрядов кода действительной составляющей. На выходе второго сумматора 10 определяется результат М2 сложения кода мнимой составляющей со сдвинутым вправо на два разряда кодом действительной составляющей, т, е,

М2 Ь+1/4а.

Два млад1иих разряда а кода а подаются на второй информационный вход второго KONflviyTaTopa 4,

На первый и второй входы третьего сумматора 1i поступают соответственно коды действительной и инверс- iftie коды мнимой составляющих комплексного числа. При этом на выходе третьего сумматора 11 вычисляется разность кодов а и Ь .

Сигнал с выхода разряда Зн поступает на первый вход сумматора 1 2 по модулю два, транслирующего этот сиг- при правильной работе устройства, т.е. (сжимаемым с выхода триггера),на управляющие входы первого 13 и второго 14 комг-гутаторов.

На выходе первого коммутатора 13 определяется приближенное значение М модуля комплексного числа:

М

а- -1/4Ь., если а Ь Ь+1/4а, если Ь а .

Код М поступает на первые входы сумматоров по модулю два пятой груп- m.i 16; транслирующих этот код при правильной работе устройства (т.е. сигнале контроля ) на выход уст- ройства

Второй коммутатор 14 пропускает на выход младшие разряды меньшего из кодов а и Ь.

Коды с выходов второго коммутатора 14 и сумматоров по модулю два групп 7 и 8 поступают на входы блока 15 свертки по модулю три, причем нечетные разряды кодов и kb и

четш,й разряд кода tn подаются на нечетные входы блока 15, 11меющие весовые функции , а четные разряды кодов ka и kb и нечетный разряд кода m подаются на четные рходы блока 15 свертки по MOAyjra три, имеющие весовь е функции 1.

При этом на выходе второго блока свертки по модулю три образуется код ltm (ka-t-kb-m)mod 3, являющийся вычетом по модулю три кода М, Действительно :

(Ml)mod3(ka+l/4 kb)mod 3(ka+,

-kb)mod3;

(M2)mod3(kb+I/4 ka)mod 3(kb-t- -ka)mod3,

из чего с учетом отбрасываемых младших разрядов следует

(M)mod ,

Код km с выхода блока 15 свертки по модулю три поступает на первые входы сумматоров по модулю два шестой группы 17, транслирующих этот код при правильной работе устройства на входы блока 18 свертки по модулю три На другие входы этого блока поступает код М, причем нечетные разряды кода М и четный разряд кода км приходят на нечетные входы блока 18, имеющие весовые функции 1, а четные разряды кода М и нечетный разряд кода КМ приходят на четные входы блока 18, имеющие весовые, функции 1. При этом на выходе блока 18 образуется код К, принимающий значения 01 и 10, если (M)mod . Код К поступает на входы второго сумматора 19 по модулю два, преобразующего его в сигнал С, равный нулю при правильной работе устройства. Этот сигнал запоминается на триггере 20.

Сигнал С на выходе триггера 20, являющемся контрольным выходом устройства, указывает при значении 1 на неправильное функционирование устройства. В этом случае на вторые входы сумматоров по модулю два первой 5, второй 6, третьей 7, четвертой 8, пятой 16 и шестой 17 групп и сумматора 12 по модулю два поступает значение , которое приводит к получению на их выходах кодов, инверс- ньк по отношению к поступающим на их первые входы. На выходах коммутаторов f3 и появляются соответственно КОДЫ М ) . Код ГП и КОДЫ,1сй,

33 Ki5

|сЬПоступают на входы второго блока 15 свертки по модулю три, который вычисляет код км (KQ-bfce-m) .

Коды М и |(/У1 поступают на первые 5 входы соответственно сумматоров по модулю два пятой 16 и шестой 17 групп, которые в соответствии со значением С 1, подаваемым на вторые входы, инвертируют указанные коды,

10 образуя на выходе коды М и K« . Код М поступает на выход устройства, а также вместе с кодом кМ на входы блока 8 свертки по модулю три для получения кода К и затем кода С на сум15 маторе 19 по модулю два и триггере 20.

Следовательно, для случая с 1 соответствующего обнаружению в устройстве ошибки, на выходах и входах

20 блоков 9-11 и 15, а также информационных входах и выходах коьмутато- ров 13 и 14 вырабатьшаются коды, инверсные по отношению к вычисленным для значения . При возникновении

25 константной одиночной неисправности на перечисленных входах или выходах блоков устройства и соответственно обнаружении схемой контроля, на выходе триггера 20 устанавливается зна3Q чение сигнала с I. Последнее приводит к икаертированию кодов, в результате чего значение сигнала в точке действия неисправности совпадает с задаваемым, что позволяет получить (оперируя инверсными кодами) правильное значение модуля кo mлeкcнo- го числа.

35

Формула изобретения

Устройство для вычисления модуля комплексного числа, содержащее два регистра аргументов, два регистра контрольных разрядов, три сумматора, два коммутатора и первый блок свертки по модулю три, причем входы дей- ствительной и мнимой частей комплексного числа устрой.ства соединены с информационными входами первого и второго регистров аргументов соответственно, входы контрольных разрядов действительной и мнимой частей комплексного числа устройства соединены с информационными входами первого и второго регистров контрольных разрядов соответственно, выходы первого и второго сумматоров соединены с первым и вторым информационными входами первого коммутатора соответствен

но, выходы двух ипадшнх разрядов первого и второго регистров аргументов соединены с первой и второй группами информационных входов второго коммутатора,

отличающееся

тем, что, с целью повышения достоверности вычислений за счет возможности исправления константных одиночных неисправностей, в него дополнитель- но введены шесть групп сумматоров по модулю два, два сумматора по модулю, два, второй блок свертки по модулю три и триггер, причем выходы первого и второго регистров аргументов и пер- .вого и второго регистров контрольных разрядов соединены с первыми входами- сумматоров по модулю два с первой по четвертую группы соответственно, выходы сумматоров по модулю два первой и второй групп соединены с первыми входами первого и второго сумматоров соответственно, входы i разрядов вторых входов первого и вто- рого сумматоров (, п-2, где п - разрядность аргумента) соединены с выходами (i+2) разрядов сумматоров по модулю два второй и первой групп соответственно, выходы старших разрядов сумматоров ло модулю два пер- вой и второй групп соединены с попарно объединенными входами двух старших разрядов вторых входов соответственно второго и первого сумматоровэ сумматоров по модулю два первой группы соедпнень с первой группой информационных входов третьего сумматора, вторая группа информационных входов которого соединена с ин Б:ерсными выходами сумматоров по модулю два второй группы, выход знаково вого разряда третьего сумматора сое- с первым входом первого сумматора по модулю два, выход которого соединен с управляющими входами первого и второго коммутаторов, выход, первого коммутатора соединен с первыми входами сумматоров по модулю дв пятой группы, выходы которых соединены с первой группой входов первого блока свертки по модулю три, вторая группа входов которого соединена с выходами сумматоров по модулю два шестой группы, первые входы которых соединены с выходами второго блока свертки по модулю три, входа первой, второй и третьей групп которого соединены с выходами второго коммутатора, сумматоров по модулю два третьей и четвертой групп соответственно, выходы первого блока свертки по модулю три соединены с входами BTopo.ro сумматора по модулю два, вьжод которого соединен с информационным входом триггера, выход которого соединен с входами второй группы сумматоров по модулю два с первой по групп и с вторым входом первого ci ttMaTopa по модулю два

ВНИИПИ Заказ 2771/50 . Тираж 671 Подписное Произв.-полигр, пр-тие г. Ужгород, ул. Проектная А

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1193662A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1287151A1 |

| Устройство для вычисления модуля комплексного числа | 1982 |

|

SU1104505A2 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1254478A1 |

| Устройство для контроля по модулю три умножения комплексных чисел | 1987 |

|

SU1434438A1 |

| Устройство для деления чисел | 1989 |

|

SU1711151A1 |

| Устройство для контроля умножения чисел по модулю | 1985 |

|

SU1259269A1 |

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1332321A2 |

| Устройство для контроля по модулю умножения комплексных чисел | 1985 |

|

SU1285479A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1444750A1 |

Изобретение относится к вычислительной технике и позволяет повысить достоверность вычислений модуля комплексного числа путем аппаратного исправления одиночных неисправностей. Устройство содержит первый и второй регистры аргументов, первый и второй регистры контрольных разрядов, с первой по шестую группы сумматоров по модулю два, с первого по третий сумматоры, первый и второй сумматоры по модулю два, первый и второй коммутаторы, первый и второй блоки свертки по модулю три, триг. гер. Состояние I выхода триггера указывает на неправильное функционирование устройства.. Код вычисленного значения модуля М по приближенным вьфажениям Га+1/4Ь, 1ь-И/4а, b а транслируется через пятую группу сумматоров на выход устройства при правильной работе устройства. I ил. § (Л

| Устройство для вычисления квадратногоКОРНя | 1979 |

|

SU842806A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления модуля комплексного числа | 1981 |

|

SU1001085A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1984-05-11—Подача