Изобретение относится к цифровой ычислительной технике и может быть спользовано при построении двоично- есятичных преобразователей с исправением информации.

ЦелЫо изобретения является повышение достоверности преобразования за чет исправления ошибок.

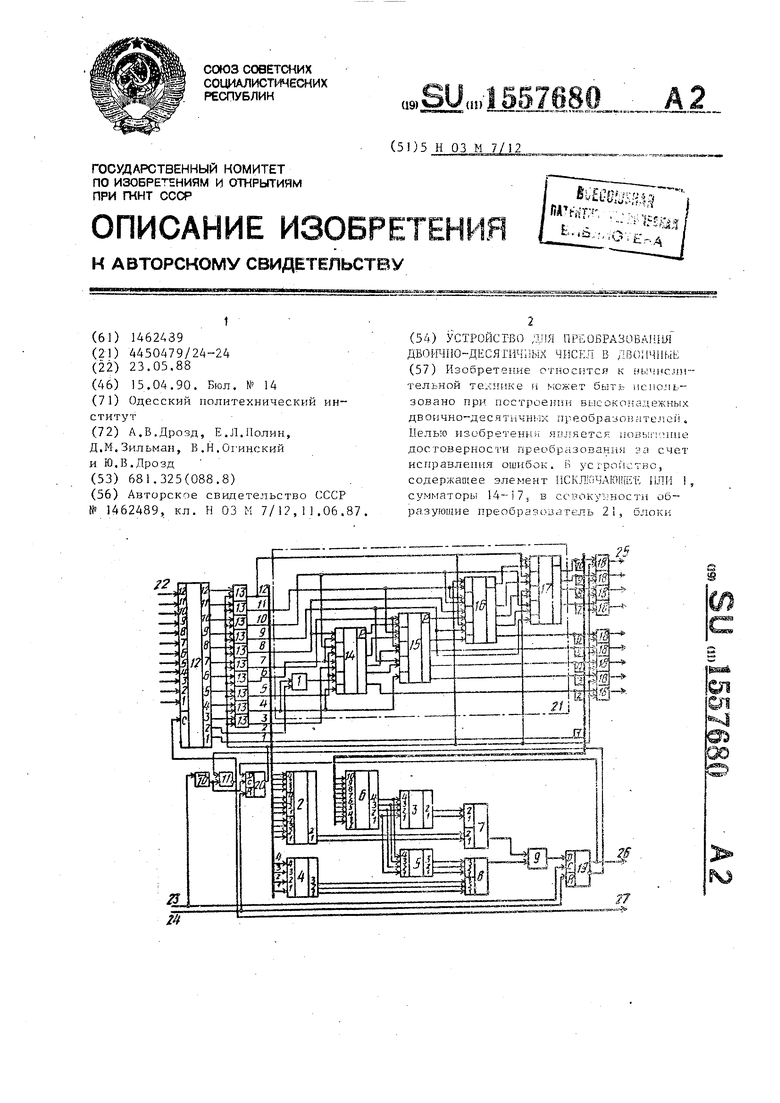

На чертеже приведена структурная схема устройства.

Устройство содержит элемент ИСКЛЮАЮЩЕЕ ИЛИ 1, первый 2 и второй 3 локи свертки по модулю три, первый 4 и втгрой 5 блоки свертки по модулю ггять, блок 6 свертки по модулю пятнадцать, первая 7 и вторая 8 схемы сравнения, элемент ИЛИ 9, элемент 10 заержки, элемент И-НЕ 11, регистр 12, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 13, первый-четвертый сумматоры 14- 17, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 18, первый 19 и второй 20 триггеры. Сумматоры 14-17 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ в совокупности образуют преобразователь 21, осуществляющий преобразование двоично-десятичного кода в двоичный без контроля. На преобразователь поступают информа- ционные входы 22 синхровход 23, вход 24 сброса. Преобразователь формирует информационные выходы 25, контрольный выход 26 и тактовый выход 27.

Устройство работает следующим образом.

В начале работы на вход 24 сброса поступает сигнал, устанавливающий пер1 вый 19 и второй 20 триггеры в нулевое состояние. На синхровход 23 поступает синхроимпульс СИ типа меандр, тактирующие работу устройства. Синхроимпульсы СИ поступают на синхровход 19 и через элемент 10 задержки на первый вход элемента И-НЕ, который пропускает их инверсные значения СИ на синхро вход регистра 12 под действием единичного значения с выхода первого триггера 19.

На информационные входы регистра 12 через входы 22 устройства поступает двоично-десятичный код А2(() числа записываемый в регистр по задержан0

5

0

5

0

5

0

5

0

5

ному фронту синхроимпульса СИ. С выходов регистра 12 разряды кода A2,fo поступают на первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы

13,на вторые их входы подается нулевое значение с выхода второго триггера 20, которое обеспечивает трансляцию разрядов кода Аг(0 на выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 13 без изменения, С выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 13 код А4.(0 поступает на вход преобразователя 21, который переводит двоично-десятичное число А )t в двоичное путем вычисления взвешенной суммы разрядов тетрад двоично- десятичного числа. Для этого разряды тетрад подаются на входы разрядов двоичных сумматоров 14-17, суммы весов которых равны весам этих разрядов тетрад. Разряд 2 тетрады 1 посту- пае-т на вход разряда сумматора 14

с весом 21 (через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ I), разряд 3 тетрады I поступает на вход разряда с весом 2 сумматора 14, разряд 4 тетрады 1 поступает непосредственно и через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 1 на вход разряда с весом 21 сумматора 14 и на вход переноса сумматора 15. Разряд 1 тетрады 2 имеет вес 10 и поступает на входы разрядов с весами 23 и 21 сумматора

14.Разряд 2 тетрады 2 имеет вес 20 и поступает на входы разрядов с весами 2г и 2я сумматора 14. Разряд 3 тетрады 2 имеет вес 40 и поступает на входы разрядов с весами 23 и 2 сумматора 14. Разряд 4 тетрады 2 имеет вес 80 и пЪступает на входы разрядов с весами 24 и 2 сумматоров 14 и-16 соответственно. Разряды 1-4 тетрады 3 имеют веса 100, 200, 400,800

и поступают на входы трех разрядов сумматоров каждый, соответственно на входы разрядов с весами 2Э, 2 вход переноса сумматоров 15-17, на входы разрядов с весами 23, 27 и 2е сумматоров 14, 16 и 17, на входы разрядов с весами 24, 21 и 28 сумматоров 15, 16 и 17, на входы разрядов с весами 2s, 2 и 29 сумматоров 16,

17 и 17, Разряд 1 тетрады поступает на выход преобразователя с весом 2°. Сумма, вычисляемая двоичными сумматорами 14-17, определяет двоичное число на выходе преобразователя 21, с выходов которого разряды двоичного числа Вг, начиная со второго разряда, поступают на первые входы соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 18, на вторые входы которых поступает нулевое значение с выхода второго триггера 20. С выходов первого разряда и выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 18 двоичное число В поступает на выходы 25 устройства.

Кроме того, двоично-десятичный код числа с выхода элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 13 поступает также на вход первого блока свертки по модулю три 2, а разряды младшей тетрады этого кода - на вход первого блока свертки по модулю пять 4, которые определяют остатки от деления двоично-десятичного кода Аi-ю соответственно на три и на пять

С выхода преобразователя 21 двоичный код BJL поступает также на вход блока 6 свертки по модулю пятнадцать, который определяет четырехразрядный остаток от деления двоичного кода В5 на пятнадцать. Полученный остаток поступает далее на входы вторых блоков свертки по модулю три 3 и по модулю пять 5, которые определяют остатки от деления двоичного кода Ег соответственно на три и на пять.

Остатки по модулю три с выхода первого 2 и второго 3 блоков свертки по модулю три поступают на входы первой схемы 7 сравнения, а остатки по модулю пять с выходов первого 4 и второго 5 блоков свертки по модулю пять поступают на входы второй схемы 8 сравнения.

Поскольку число в двоично-десятичном коде А 10 и в двоичном коде В имеет одинаковую делимость на три, а также на пять, то при правильной работе устройства сравниваемые остатки совпадут, первая 7 и вторая 8 схемы сравнения выработают на выходах нулевые значения. Эти значения объединяются по ИЛИ на элементе 9, который формирует сигнал контроля, записываемый в триггер 19 по заднему фронту синхроимпульсов СИ. С выхода элемента. И-НЕ 11 заданный и проинвертиро1557680

0

ванный синхроимпульс СИ поступает на тактовый выход устройства, определяя момент приема результата по заднему фронту.

С прямого выхода триггера 19 сигнал контроля поступает на контрольный ныход 26 устройства. При несовпадении сравниваемых остатков, что возможно в неисправном устройстве, одна или обе схемы 7, 8 сравнения устанавливают на своем выходе, а следовательно, на контрольном выходе единичное значение. При этом нулевой 5 сигнал с инверсного выхода триггера

19запрещает прохождение синхроимпульса СИ через элемент И-НЕ.

Кроме того, сигнал контроля с выхода первого триггера 19 поступает на 0 информационный вход второго триггера

20по переднему фронту сигнала с выхода элемента задержки. Сигнал контроля с выхода триггера 20 подается на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

5 первой 13 и второй 18 групп, а также на вход четвертого разряда второго слагаемого третьего сумматора 16 и вход второго разряда второго слагаемого четвертого сумматора 17.

0 При этом инвертируются выходы всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 13, выходы элемента ИСКЛЮЧАЮ- ШЕЕ ИЛИ 1, а соответственно все входы и выходы сумматоров 14-17. Это приводит к маскированию одиночной ошибки, проявившейся на прямом значении кода A,j.10 . На первых входах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 18 образуется инверсное значение кода Вг, которое инвертируется этими элементами и поступает на выходы 25 устройства.

5

0

5

0

Инверсные коды Аг

В

1 поступают также на блоки свертки 2, 4 и 6 соответственно, которые в совокупности с блоками 3, 5, 7, 8 и 9 осуществляют контроль инверсного значе- ния кода В2 аналогично тому, как это выполняется для прямого значения. При этом с первого триггера 19 снимается сигнал контроля, определяющий факт.исправления ошибки.

В качестве примера рассмотрим преобразование числа А 50370 5 0101000000 П(4.„. Первоначально выполняется счет на прямом значении числа А. На сумматорах 14-17 выполняются соответственно следующие операции сложения

0001 + 0001 + 0000 -f 1001ь 01 10

ooog oioi oioo oooo ooooT 677oT 55777

Блоки 2 и 4 определяют 503 mod 3 210 IO.J и 503 mod 5 310 01 1. Блок 6 определяет 503 mod 15 8Ш 1000.2, Блоки 3 и 5 определяют ,8 mod 3 2 t9 102 и 8 mod 5 3fe 01 Ц. Блоки 7 и 8 и далее элемент 9 определяют правильность работы устройства.

При ошибке, например, вход второго разряда первого слагаемого оказался оборванным, т.е. преобразователь на прямом значеш и числа определит число В 50710 , а блоки 2 и 4, 6, 3 и 5 определят г коды, Юг, 01 12, 1100,, 00 и 2 и триггер 19 установится в единичное значение. Инвертируется число A2.fo на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 13.

При этом на сумматорах 14-17 выполнятся следующие операции сложения

11О

+1111 +0110 + 1001

JO10 .JQLL 1111 77о7о TooTo TTooo

Будет получено число 1000001000-2, которое при инвертировании на элементах 18 группы определяет результат преобразования 0111110111г . Таким образом маскируется ошибка.

Формула изобретения

Устройство для преобразования двоично-десятичных чисел в двоичные по авт.св. V 1462489, отличающееся тем, что, с целью повышения достоверности преобразования за счет исправления ошибок, в него вве

1

1 ПО

Ш1

1И10

5

0

5

0

5

0

дены первая и вторая группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй триггеры, регистр, элемент задержки и элемент И-ПЕ, выход которого соединен с синхровходом регистра и с тактовым выходом устройства, информационные входы которого соединены с информационными входами регистра, выходы которого, кроме выходов двух младших разрядов , соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, вторые входы которого соединены с выходом второго триггера и с входами второго и четвертого разрядов второго слагаемого третьего и четвертого сумматоров и ,первыми входами элементов ИСКЛЮЧАЮЩЕЕ .ИЛИ второй группы, выходы которых являются информационными выходами устройства, синхровход которого соединен с синхровходом первого триггера и через элемент задержки с синхровходом второго триггера и первым входом элемента И-НЕ, второй вход которого соединен с инверсным выходом первого триггера, информационный вход которого соединен с выходом элемента ИЛИ, а прямой выход первого триггера соединен с информационным входом второго триггера и является контрольным выходом устройства,, вход сброса которого соединен с входами сброса первого и второго триггеров, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы соответственно соединены с информационными выходами преобразователя, выход второго разряда регистра соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход первого разряда регистра является выходом младшего разряда устройства и соединен с входом младшего разряда блока свертки по модулю пятнадцать.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1987 |

|

SU1425678A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1987 |

|

SU1462489A2 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943702A2 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Устройство для деления чисел на константу типа 2 @ + 1 | 1990 |

|

SU1791813A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высоконадежных двоично-десятичных преобразователей. Целью изобретения является повышение достоверности преобразования за счет исправления ошибок. В устройство, содержащее элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 1, сумматоры 14 - 17, в совокупности образующие преобразователь 21, блоки свертки по модулю три 2, 3, блоки свертки по модулю пять 4, 5, блок свертки по модулю пятнадцать 6, схемы сравнения 7, 8, элемент ИЛИ 9, дополнительно введены регистр 12, группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 13, 18, триггеры 19, 20, элемент задержки 10 и элемент И-НЕ 11. 1 ил.

Составитель М.Аршавский Редактор О.СпесивыхТехред А.КравчукКорректор Т.Палий

Заказ 724

Тираж 659

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКН1 СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1987 |

|

SU1462489A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-04-15—Публикация

1988-05-23—Подача