1

Изобретение относится к автоматике, вычислительной и измер гте1гь} ой технике и может быть применено в системах программного управления технологическими процессами, устройствах цифровой линеаризации первичных измерительных преобразователей, устройствах электронного моделирования, специализированных вычислительных комплексах и т.д.

Цель изобретения - расширение клас са решаемых задач за счет одчовременk,x ного вычисления функций у х е ;

xi 2m

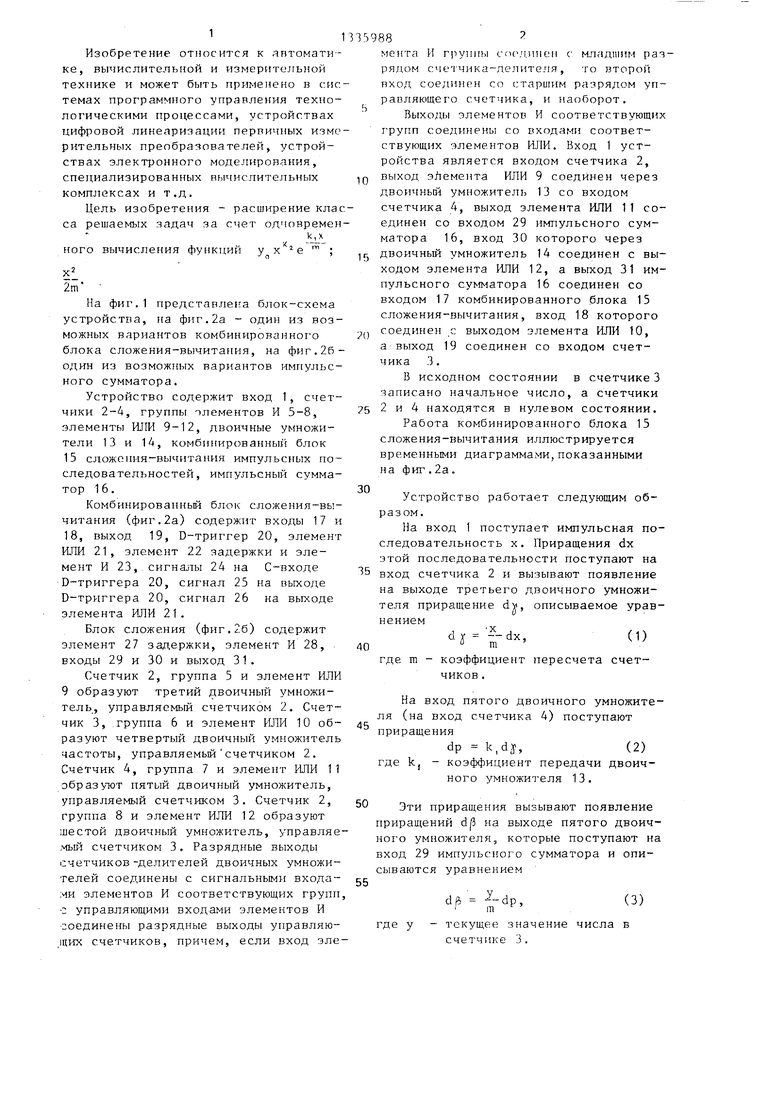

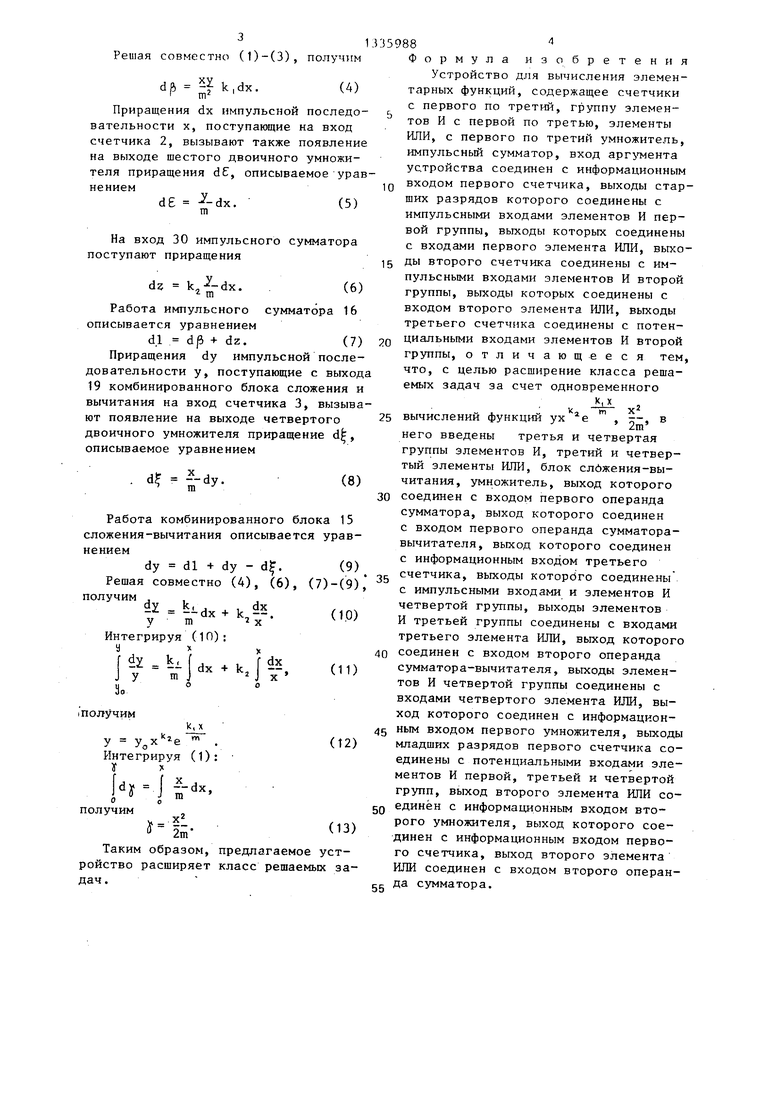

На фиг.1 представле1 а блок-схема устройства, на фиг.2а - один из возможных вариантов комбинированного блока сложения-вычитания, на фиг.26- один из возможных вариантов импульсного сумматора.

Устройство содержит вход 1, счетчики 2-4, группы тлементов И 5-8, элементы ИЛИ 9-12, двоичные умножители 13 и 14, комбинированный блок 15 сложения-вычитания импульсных последовательностей, импульсный сумматор 1 6.

Комбинированньй блок сложения-вычитания (фиг.2а) содер :ит входы 17 и 18, выход 19, D-триггер 20, элемент ИЛИ 21, элемент 22 задержки и элемент И 23, сигналы 24 на С-входе D-триггера 20, сигнал 25 на выходе D-триггера 20, сигнал 26 на выходе элемента ИЛИ 21.

Блок сложения (фиг.2б) содержит элемент 27 задержки, элемент И 28, входы 29 и 30 и выход 31.

Счетчик 2, группа 5 и элемент ИЛИ 9 образуют третий двоичный умножитель, управляемый счетчиком 2. Счетчик 3, .группа 6 и элемент ИЛИ 10 образуют четвертый двоичный умножитель частоты, управляемьй счетчиком 2. Счетчик 4, группа 7 и элемент ИЛИ 11 образуют пятый двоичный умножитель, управляемый счетчиком 3. Счетчик 2, группа 8 и элемент ИЛИ 12 образуют шестой двоичный умножитель, управляемый счетчиком 3. Разрядные выходь счетчиков-делителей двоичных умножителей соединены с сигнальными входами элементов И соответствующих групп с управляющими входами элементов И соединены разрядные выходы управляю- jKKX счетчиков, причем, если вход эле35988

мента И группы со(ч.ииен с- младшим разрядом счетчика-делителя, то второй вход соединен со старшим разрядом управляющего счетчика, и наоборот.

Выходы элементов И соответствующих г рупп соединены со входами соответствующих элементов ИЛИ. Вход 1 устройства является входом счетчика 2,

д выход, элемента ИЛИ 9 соединен через двоичньо умножитель 13 со входом счетчика 4, выход элемента ИЛИ 11 соединен со входом 29 импульсного сумматора 16, вход 30 которого через

IT, двоичный умножитель 14 соединен с выходом элемента ИЛИ 12, а выход 31 импульсного с.умматора 16 соединен со входом 17 комбинированного блока 15 сложения-вычитания, вход 18 которого

.;(, соединен с выходом элемента ИЛИ 10, а выход 19 соединен со входом счетчика 3.

В исходном состоянии в счетчике 3 записано начальное число, а счетчики

5 2 и А находятся в нулевом состоянии.

Работа комбинированного блока 15 сложения-вычитания иллюстрируется временными диаграммами,показанными на фиг.2а.

30 ,, „ «

Устройство работает следующим образом.

На вход 1 поступает импульсная последовательность X. Приращения dx этой последовательности поступают на 5 вход счетчика 2 и вызывают появление на выходе третьего двоичного умножителя приращение dv, описываемое уравнением

где m - коэффициент пересчета счетчиков ,

45

На вход, пятого двоичного умножителя (на вход счетчика 4) поступают приращения

dp k,d)f,(2)

где k, - коэффициент передачи двоичного умножителя 13.

Эти приращения вызывают появление приращений dp на выходе пятого двоичного умножителя, которые поступают на вход 29 импульсного сумматора и описываются уравнением

55

(3)

d, i-dP

где у - текущее значение числа в

счетчике 3.

Решая совместно (1)-(3), получим dft Ц k,dx.(4)

f m

т

Приращения dx импульсной последовательности X, поступающие на вход счетчика 2, вызывают также появление на выходе шестого двоичного умножителя приращения d5, описываемое уравнением

d .(5)

tn

На вход 30 импульсного сумматора поступают приращения

dz k- . m

Работа импульсного сумматора описывается уравнением

dl d + dz.(7)

Приращения dy импульсной последовательности у, поступающие с выхода 19 комбинированного блока сложения и вычитания на вход счетчика 3, вызывают появление на выходе четвертого двоичного умножителя приращение d, описываемое уравнением

d --dy.

га Работа комбинированного блока 15 сложения-вычитания описывается уравнением

dy dl + dy - d. (9) Рещая совместно (4), (6), (7)-(9), получим

(1.0)

Формула изобретения Устройство для вычисления элементарных функций, содержащее счетчики с первого по третий, группу элементов И с первой по третью, элементы ИЛИ, с первого по третий умножитель, импульсньй сумматор, вход устройства соединен с информационным

д входом первого счетчика, выходы старших разрядов которого соединены с импульсными входами элементов И первой группы, выходы которых соединены с входами первого элемента ИЛИ, вьгхо15 Ды второго счетчика соединены с импульсными входами элементов И второй группы, выходы которых соединены с входом второго элемента ИЛИ, выходы третьего счетчика соединены с потен2Q циапьными входами элементов И второй группы, отличающееся тем, что, с целью расширение класса решаемых задач за счет одновременного

к, X

- :,J I i 5

25 вычислении функцрш ух е ,

него введены третья и четвертая группы элементов И, третий и четвертый элементы ИЛИ, блок слбжения-вы- (8) читания, умножитель, выход которого 30 соединен с входом первого операнда сумматора, выход которого соединен с входом первого операнда сумматора- вычитателя, выход которого соединен с информационным входом третьего

(6) 16

х 2Ш

dy k, , , . dx i i.(jx + k. -.

у m X Интегрируя (in):

a

Do ( получим

(11)

J у m JMX

11оо

k,x

25 счетчика, выходы которого соединены с импульсными входами и элементов И четвертой группы, выходы элементов И третьей группы соединены с входами третьего элемента ИЛИ, выход которого

40 соединен с входом второго операнда сумматора-вычитателя, выходы элементов И четвертой группы соединены с входами четвертого элемента ИЛИ, выход которого соединен с информацион45 ным входом первого умножителя, выходы младших разрядов первого счетчика соединены с потенциальными входами элементов И первой, третьей и четвертой групп, выход второго элемента ИЛИ соединён с информационным входом второго умножителя, выход которого соединен с информационным входом первого счетчика, выход второго элемента ИЛИ соединен с входом второго операн

(1)

(Т2)

получим

(13)

предлагаемое усткласс решаемых за

х 2Ш

счетчика, выходы которого соединены с импульсными входами и элементов И четвертой группы, выходы элементов И третьей группы соединены с входами третьего элемента ИЛИ, выход которого

соединен с входом второго операнда сумматора-вычитателя, выходы элементов И четвертой группы соединены с входами четвертого элемента ИЛИ, выход которого соединен с информационным входом первого умножителя, выходы младших разрядов первого счетчика соединены с потенциальными входами элементов И первой, третьей и четвертой групп, выход второго элемента ИЛИ соединён с информационным входом второго умножителя, выход которого соединен с информационным входом первого счетчика, выход второго элемента ИЛИ соединен с входом второго операн

55

да сумматора.

17

17

г

25

21

гб.

гз

Л

irij

| название | год | авторы | номер документа |

|---|---|---|---|

| Измерительный функциональный преобразователь | 1981 |

|

SU983704A1 |

| Цифровой аппроксиматор | 1981 |

|

SU1010619A1 |

| Измерительный функциональный преобразователь | 1981 |

|

SU984042A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1045227A1 |

| Цифровой преобразователь элементарных функций | 1984 |

|

SU1193669A1 |

| Число-импульсный функциональный преобразователь | 1981 |

|

SU997040A1 |

| Логарифмический преобразователь | 1986 |

|

SU1383346A1 |

| Вычислительное устройство | 1983 |

|

SU1083187A1 |

| Число-импульсное устройство для вычисления обратного тригонометрического тангенса | 1983 |

|

SU1092498A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1003094A1 |

Цель изобретения - расширение класса решаемых задач путем обеспечения возможности одновременного вычис ления функций ; , Известно устройство для вычисления зле- ментарных функций, содержащее первый, второй и третий счетчики, первую и вторую группы элементов И, первый и второй злементы ИЛИ, первый и второй двоичные умножители, : импульсный сумматор, первый вход которого соединен с выходом первого элемента.ИЛИ, входами соединенного с выходами элементов И первой группы, сигнальные входы которых соединены с выходами соответствующих разрядов первого счетчика, управляющие входы - с выходами соответствующих разрядов второго счетчика и сигнальными входами элементов И второй группы, выходы которой соединены с входами второго элемента Ш1И, а управляющие входы - с выходами соответствующих разрядов третьего счетчика. Для достижения поставленной цели в устройство введены третья и четвертая группы элементов И, третий и четвертый элементы ИЛИ и комбиниро- ванньш блок сложения-вычитания. Выход последнего соединен с входом второго счетчика, выходы которого соединены с управляющими входами-соответствующих элементов И третьей группы, выходами соединенной с входами третьего элемента ИЛИ. Выход третьего элемента ИЛИ через первый двоичный умножитель соединен с втор-ым входом импульсного сумматора, выход которого соединен с первым входом комбинированного блока сложения-вычитания, второй вход которого соединен с выходом второго элемента И. Сигнальные входы элементов И третьей и четвертой групп соединены соответственно с выходами третьего .счетчика и с управляющими входа1чи соответствующих элементов И четвертой группы, выходы которой соединены с входами четвертого элемента ИЛИ, выходом соединенного через второй двоичный умножитель с входом первого счетчика. Вход третьего счетчика является входом устройства. 2 ил. (Л 00 со. СД Г 00 00

Фиг.2

Редактор Н.Егорова

Составитель З.Шершиева Техред М.Холанич

Заказ 4048/43 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, л. Проектная, 4

Корректор С.Шекмар

| Цифровой функциональный преобразователь | 1982 |

|

SU1037270A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1045227A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1985-06-07—Подача