Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения процессоров быстрого преобразования Фурье (БПФ), в которых необходимо выполнять операцию вида (С А.+ В; .

LD. (A-B)-w,. (1)

где )-jC2; A ai+ja2; B bi-fjb2; P di + jd2 - комплексные числа; -комплексный коэффициент Фурье (фазовый множитель).

Цель изобретения - повышение быстродействия.

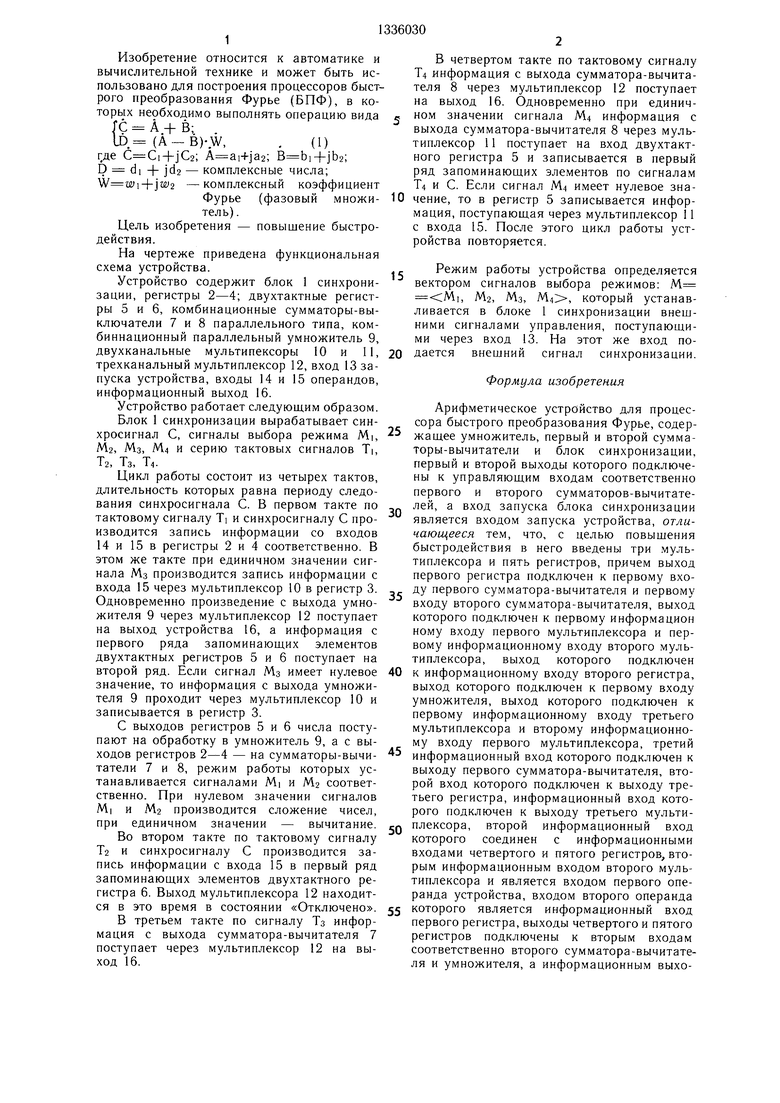

На чертеже приведена функциональная схема устройства.

Устройство содержит блок 1 синхронизации, регистры 2-4; двухтактные регистры 5 и 6, комбинационные сумматоры-выключатели 7 и 8 параллельного типа, ком- биннационный параллельный умножитель 9, двухканальные мультипексоры 10 и 11, трехканальный мультиплексор 12, вход 13 запуска устройства, входы 14 и 15 операндов, информационный выход 16.

Устройство работает следующим образом.

Блок 1 синхронизации вырабатывает синхросигнал С, сигналы выбора режима Mi, М2, Мз, М4 и серию тактовых сигналов Ti,

Т2, Тз, Т4.

Цикл работы состоит из четырех тактов, длительность которых равна периоду следования синхросигнала С. В первом такте по тактовому сигналу Т| и синхросигналу С производится запись информации со входов 14 и 15 в регистры 2 и 4 соответственно. В этом же такте при единичном значении сигнала Мз производится запись информации с входа 15 через мультиплексор 10 в регистр 3. Одновременно произведение с выхода умножителя 9 через мультиплексор 12 поступает на выход устройства 16, а информация с первого ряда запоминающих элементов двухтактных регистров 5 и 6 поступает на второй ряд. Если сигнал Мз имеет нулевое значение, то информация с выхода умножителя 9 проходит через мультиплексор 10 и записывается в регистр 3.

С выходов регистров 5 и 6 числа поступают на обработку в умножитель 9, а с выходов регистров 2-4 - на сумматоры-вычи- татели 7 и 8, режим работы которых устанавливается сигналами Mi и М2 соответственно. При нулевом значении сигналов М| и М2 производится сложение чисел, при единичном значении - вычитание.

Во втором такте по тактовому сигналу Т2 и синхросигналу С производится запись информации с входа 15 в первый ряд запоминающих элементов двухтактного регистра 6. Выход мультиплексора 12 находится в это время в состоянии «Отключено.

В третьем такте по сигналу Тз информация с выхода сумматора-вычитателя 7 поступает через мультиплексор 12 на выход 16.

В четвертом такте по тактовому сигналу Т4 информация с выхода сумматора-вычитателя 8 через мультиплексор 12 поступает на выход 16. Одновременно при единичном значении сигнала М4 информация с выхода сумматора-вычитателя 8 через мультиплексор 11 поступает на вход двухтактного регистра 5 и записывается в первый ряд запоминающих элементов по сигналам Т4 и С. Если сигнал М4 имеет нулевое значение, то в регистр 5 записывается информация, поступающая через мультиплексор 11 с входа 15. После этого цикл работы устройства повторяется.

5

0

5

0

5

0

5

0

5

Режим работы устройства определяется вектором сигналов выбора режимов: М , М2, Мз, М4, который устанавливается в блоке 1 синхронизации внещ- ними сигналами управления, поступающими через вход 13. На этот же вход подается внещний сигнал синхронизации.

Формула изобретения

Арифметическое устройство для процессора быстрого преобразования Фурье, содержащее умножитель, первый и второй сумма- торы-вычитатели и блок синхронизации, первый и второй выходы которого подключены к управляющим входам соответственно первого и второго сумматоров-вычитате- лей, а вход запуска блока синхронизации является входом запуска устройства, отличающееся тем, что, с целью повышения быстродействия в него введены три мультиплексора и пять регистров, прячем выход первого регистра подключен к первому входу первого сумматора-вычитателя и первому входу второго сумматора-вычитателя, выход которого подключен к первому информацион ному входу первого мультиплексора и первому информационному входу второго мультиплексора, выход которого подключен к информационному входу второго регистра, выход которого подключен к первому входу умножителя, выход которого подключен к первому информационному входу третьего мультиплексора и второму информационному входу первого мультиплексора, третий информационный вход которого подключен к выходу первого сумматора-вычитателя, второй вход которого подключен к выходу третьего регистра, информационный вход которого подключен к выходу третьего мультиплексора, второй информационный вход которого соединен с информационными входами четвертого и пятого регистров, вторым информационным входом второго мультиплексора и является входом первого операнда устройства, входом второго операнда которого является информационный вход первого регистра, выходы четвертого и пятого регистров подключены к вторым входам соответственно второго сумматора-вычитателя и умножителя, а информационным выхо1336030

34

дом устройства является выход первогорого подключен к шестому выходу блока

мультиплексора, при этом управляющие вхо-синхронизации, седьмой выход которого подды второго и третьего мультиплексоровключен к входу разрешения выдачи пятого

подключены соответственно к третьему ирегистра, вход разрешения выдачи второго

четвертому выходам блока синхронизации,г регистра соединен с третьим управляющим

пятый выход которого подключен к входамвходом первого мультиплексора и подклюразрешения записи первого, второго, тре-чен к восьмому выходу блока синхронизатьего, четвертого и пятого регистров, пер-ции, девятый выход которого подключен

вому управляющему входу первого мульти-к тактовым входам первого, второго, треплексора, второй управляющий вход кото-тьего, четвертого и пятого регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Устройство для вычисления скользящего спектра | 1988 |

|

SU1527642A1 |

| Устройство для реализации быстрого преобразования Фурье | 1989 |

|

SU1672469A1 |

| Устройство для быстрого действительного преобразования Фурье | 1986 |

|

SU1476488A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения процессоров быстрого преобразования Фурье. Цель изобретения - повышение быстродействия. Поставленная цель достигается за счет того, что устройство имеет блок синхронизации 1, регистры 2, 3, 4, 5, 6, сумматоры - вычита- тели 7, 8, умножитель 9, мультиплексоры 10, 11, 12, вход 13 запуска устройства, входы 14, 15 операндов, информационный выход 16 устройства и соответствующие связи между узлами устройства. 1 ил. S (Л ;} 12 ТТ 16 ( со со О5 о оо

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сержанович Д | |||

| С., Фуфин С | |||

| В | |||

| Электрический конденсатор переменной емкости | 1925 |

|

SU1815A1 |

| - Белорусский НИИ научно-технической информации | |||

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-01—Подача