Изобретение относится к радиотехнике и может быть использовлно для формирования гармонического сигнала с изменяющейся фазой.

Цель изобретения - упрощение путем уменьшения объема .блока памяти.

На фиг.1 представлена электрическая структурная схема дескретного

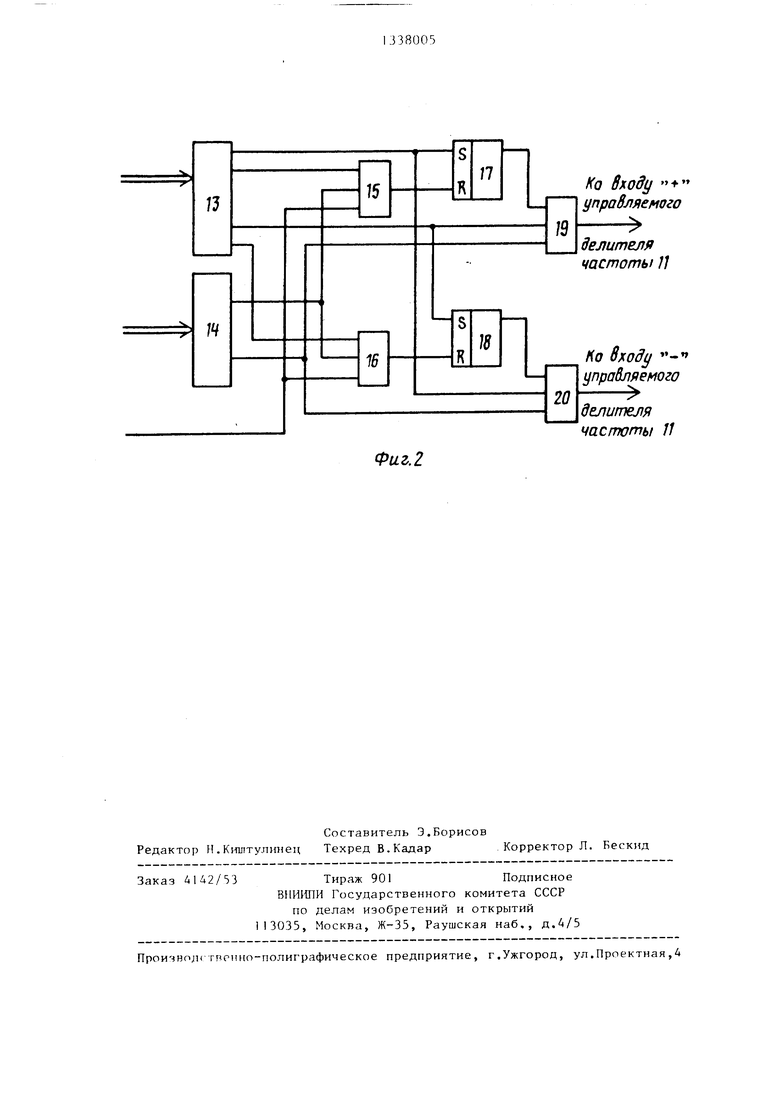

азовращателя; на фиг.2 - схема блока ю даваемые на

могут быть функции, на W|(д), где ции; 9 t/ щее время t сигнала. По 2 формир функций фор

(8-1)-(8-4) ся коды про коэффициент быть вычисл 15 Фурье синус ным фазовым

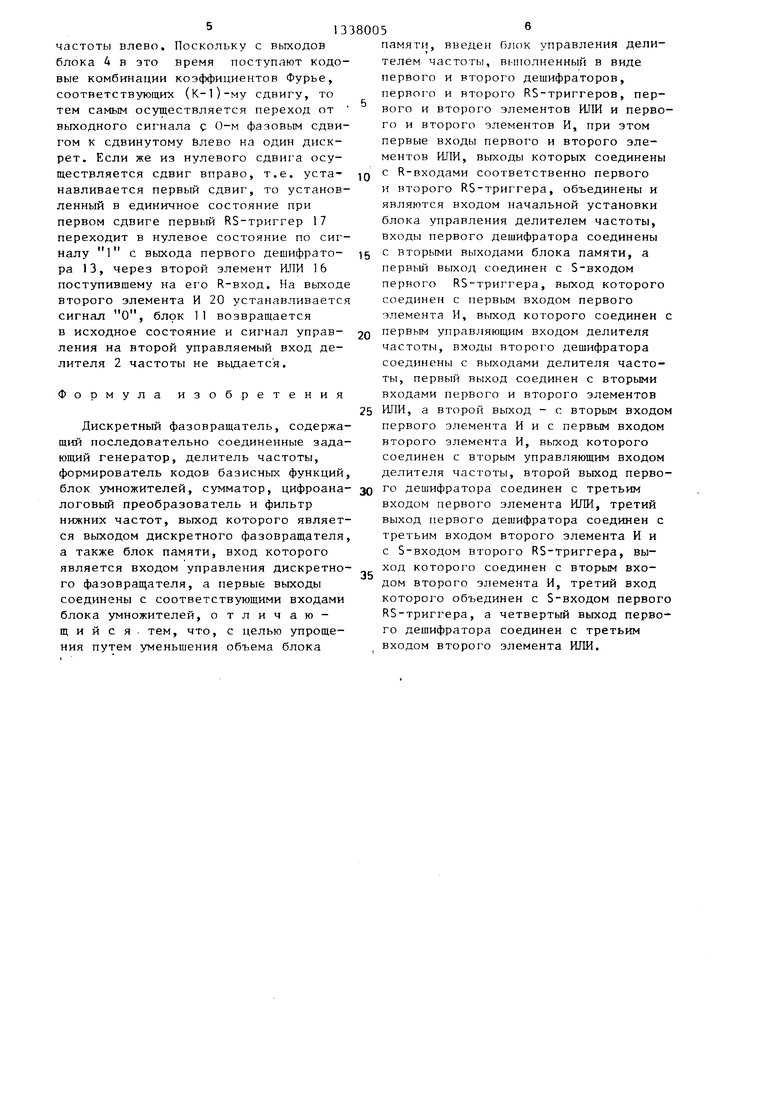

управления делителем частоты.

Дискретный фазовращатель (фиг.1) содержит задающий генератор I, делитель 2 частоты, формирова ель 3 кодов базисных функций, блок 4 памяти, сумматор 5, цифроаналог ов1.1Й преобразователь (ПАП) 6, фильтр 7 нижних частот, блок 8 умножителей, вход 9 управления дискретным фазовращателем выход 10 дискретного фазовращателя, блок 11 управления делителем частоты, вход 12 начальной установки блока управления делителем частоты.

Блок 11 управления делителем частоты (фиг. 2) содержит нервьи 13 и BTopoii 14 дещифраторы, первый 15 и второй 16 элементы ИЛИ, первый 17и второй 18 RS-триггеры, первый 19 и второй 20 элементы И.

Дискретный фазовращатель работает следующим образом.

В блок 4 памяти записаны коэффициенты Фурье для всех дискретных фазовых сдвигов в пределах одного период следования импульсов задающего генератора 1. В начале работы дискретног фазовращателя на вход 12 нaчaJПJHOй установки блока управления де.тштелем частоты подается импульс, KOTcipbrfi, проходя через первый 15 и } торой 16 элемеьггы ИЛИ, ycTanaBJuinaeT в нулевое состояние первый 17 и второй 18 К5-три1теры.

Если фазовые сдвиги п 1оису.одят в

пределах периода Т следе)вания импуль- 45 один дискрет на выходе блока 4 памяти

сов задающего ()ра 1 , то блок 11 не оказывает в.тшяния на работу делителя 2. В этом случае синхронно с работо | генератора I на вход 9 подаются коды, представляющие собой адреса ячеек памяти блока 4, в которых занисаны )ициенты Фурье. Эти коз1} фициенты соотнетствуют требуемому фазовому сдвигу и поступают на первые входы умножителей (8-1)-(8-4), входя- щие в состав блока 8 умножителей (рассматривается случай использования четырех г армоник базисно функции) . В качестве базисных функций

даваемые на

могут быть использованы различньГё функции, например функции Уолта W|(д), где i - номер базисной функции; 9 t/Tj - нормированное текущее время t; Тд - период выходного сигнала. По сиг-налу с выхода делите- 2 формирователь 3 кодов базисных функций формирует функции Уолша, по- вторые пход)1 умножителей

(8-1)-(8-4). На их в,1ходах формируются коды произведения функций Уолща на коэффициенты Фурь е С; , которые могут быть вычислены путем разложения в ряд 5 Фурье синусоидальной функции с заданным фазовым сдвигом 2 оП/г

С; где г

sin 2-(9 - -)W; (Gjde,

количество дискретов сдвига фазы в одном периоде выходного сит нала;

п - ко1шчестБо введенных дискретов сдвига фазы.

Результаты ум}южения с т-1мируются в сумматоре 5 и после цифроаналого- вого пресзбразования в цифроаяалоговом преобразователе 6 и фильтрации в фильтре 7 на В1,гходе 10 формируется гармонический сигнал, фаза которого дискретно изменяется в гц)еделах каждого периода сигнала задающего генератора 1 .

При фазовом сдвиге, превьпиающем период Т задающего генератора 1, рассмотрим сначала случай, когда фазовый сдвиг вправо выходного сигнала оказался такой, что он на один дискрет сдвига меньше фазового сдвига, равного периоду Т. Если обозначить за К число дискретов в периоде Т, то такой сдвиг является сдвигом на (К-1) дискрет относитель}1о, нулевого исходного сдвига. При сдви1 е 1зправо еше на

0

g

кодовые комбинации оказываются точно такими же, как и при нулевом сдвиге. Поэтому, если не принять соответствующих мер, произойдет возврат фазового сдвига сигнала па выходе устройства к исходному нулевому сдвигу. Но при фазовом сдвиге на (К-1) дискрет на входы дешифратора 1 3 с BI,кодов блока 4 постунает кодовая комбинация, соответствующая в данном случае (К-1)- му фазовому сдвиг у. При ттом с В1.1хода дешифратора 13 на S-вход первого RS- тригт ера 17 поступает сигнал 1 и он нерехо/1ит в единичное состояние.

13

открыБая по первому входу первый элемент И 19.

При сдвиге вправо еще на один дискрет с выходов блока 4 памяти на входы множителей (8-1)-(8-4) поступает кодовая комбинация, соответствующая нулевому сдвигу выходного сигнала. Первый дешифратор 13 выделяет информацию о том, что сдвиг равен нулю и сигнал 1 с его выхода открывает первый элемент И 19 по третьему входу Делитель 2 частоты в данном примере при отсутствии управляющих возде(1ст- вий осуществляет деление входных импульсов на 8. При этом можно условно считать, что делитель 2 частоты последовательно переходит из состояния в Г -е, во , в и т.д. до , из которого он возвращается в состояние. При состоянии делителя 2 частоты с выхода второго дешифратора 14 сигнал 1 через открытый по первому и второму входам,первый элемент И 19 поступает на первый управляющий вход делителя 2 частоты, который меняет коэффициент деления с 8 на 9. Следовательно, по очередному счетному сигналу на его входе из состояния 7 он переходит не в состояние О, как при коэффициенте деления, равном В, а в состояние. По следующему счетному импульсу делитель 2 частоты переходит в состояние, затем в , во и т.д. При состоянии 2 делителя 2 частоты с выхода второго дешифратора 14 через первый элемент ИЛИ 15 сигнал 1 поступает на R-вход первого RS-триггера 17, которьй переходит в нулевое состояние и закрывает первый элемент И 19. Тем самым блок 1 1 возвращается в ис-. ходное состояние. При этом сигнал управления с первого управляющего входа делителя 2 частоты снимается. Таким образом, делитель 2 частоты на один период сигнала с выхода его старшего разряда увеличивает коэффициент деления на единицу, чем обеспечивает сдвиг выходного сигнала на один период Т счетных импульсов делителя 2 частоты вправо. Тем самым осуществляется переход из (K-l)-ro сдвига не в 0-й, а в К-й сдвиг.

Если из (K-l)-ro сдвига происходит сдвиг влево, т.е. устанавливается (К-2)-й сдвиг, то с выхода первого дешифратора 13 через первый элемент

8005

1ШИ 15 поступает сигнал, который переводит первьш RS-триггер н исходное нулевое состояние, вследствие чего на выходе первого элемента И 19 устанавливается сигнал нулевого уровня. При дальнейших сдвигах влево работа устройства не отличается от работы устройства при дискретном сдвиге Q в пределах периода сигналов задающего

генератора 1 вплоть до достижения фазового сдвига, когда с выхода первого дешифратора 13 на S-вход второго RS-триггера 18 поступает сиг- 5 нал -, по которому он переходит в единичное состоение, открывая по второму входу второй элемент И 20.

При сдвиге влево еще на один дискрет с выходов блока 4 памяти на Q входы умножителей (8-l)-(8-4) поступает кодовая комбинация, соответствующая (К-1)-му сдвигу выходного сигнала дискретного фазовращателя. Первый дешифратор выделяет информацию о 5 том, что имеется (К-1)-й сдвиг, и сигнал с его выхода открывает второй элемент И 20 по третьему входу. В данном примере при состоянии 7 делителя 2 частоты с выхода второго де- 0 шифратора 14 сигнал 1 через откры- , тый по второму и третьему входам второй элемент И 20 поступает на второй управляющий вход делителя 2 частоты. Делитель 2 частоты меняет коэффициент деления в данном примере с на 7, а именно по очередному счетному сигналу на его входе из состояния 7 он переходит не в состояние О, как при коэффициенте деления, равном 8, 0 а в Г -е состояние. По следующему счетному импульсу делитель 2 частоты переходит во состояние и т.д. При состоянии 2 делителя 2 частоты с выхода второго дешифратора 14 через 5 второй элемент ИЛИ 16 сигнал 1 поступает на R-вход второго RS-триггера 18. Эт от RS-триггер переходит в нулевое состояние и закрьшает второй элемент И 20. Тем самым блок 11 воз- Q вращается в исходное состояние. При этом снимается сигнал управления с второго входа делителя 2 частоты.

Таким образом, делитель 2 частоты на один период сигнала с выхода его старшего разряда уменьшает коэффициент деления на единицу, чем обеспечивается сдвиг выходного сигнала дискретного фазовращателя на один период Т счетных импульсов делителя 2

5

частоты влево. Поскольку с выходов блока 4 в это время поступают кодовые комбинации коэффициентов Фурье, соответствующих (К-1)-му сдвигу, то тем самым осуществляется переход от выходного сигнала с 0-м фазовым сдвигом к сдвинутому Ёлево на один дискрет. Если же из нулевого сдвига осуществляется сдвиг вправо, т.е. устанавливается первый сдвиг, то установленный в единичное состояние при первом сдвиге первый RS-триггер 17 переходит в нулевое состояние по сигналу 1 с выхода первого дешифратора 13, через второй элемент ИЛИ 16 поступившему на его R-вход. На выходе второго элемента И 20 устанавливается сигнал О, блок 11 возвращается в исходное состояние и сигнал управления на второй управляемый вход делителя 2 частоты не выдается.

Формула изобретения

Дискретный фазовращатель, содержащий последовательно соединенные задающий генератор, делитель частоты, формирователь кодов базисных функций блок умножителей, сумматор, цифроана- логовый преобразователь и фильтр нижних частот, выход которого является выходом дискретного фазовращателя а также блок памяти, вход которого является входом управления дискретного фазовращателя, а первые выходы соединены с соответствующими входами блока умножителей, отличающийся тем, что, с целью упрощения путем уменьшения объема блока

5

0

5

о

5

памяти, введен блок управления делителем частоты, выполненный в виде первого и второго дешифраторов, первого и второго RS-триггеров, первого и второго элементов ИЛИ и первого и второго элементов И, при этом первые входы первого и второго элементов ИЛИ, выходы которых соединены с R-входами соответственно первого и второго RS-триггера, объединены и являются входом начальной установки блока управления делителем частоты, входы первого дешифратора соединены с вторыми выходами блока памяти, а первый выход соединен с S-входом первого RS-триггера, выход которого соединен с первым входом первого элемента И, выход которого соединен с первым управляющим входом делителя частоты, входы второго дешифратора соединены с выходами делителя частоты, первый выход соединен с вторыми входами первого и второго элементов ИЛИ, а второй выход - с вторым входом первого элемента И и с первым входом второго элемента И, выход которого соединен с вторым управляющим входом делителя частоты, второй выход первого дешифратора соединен с третьим входом первого элемента ИЛИ, третий выход первого дешифратора соединен с третьим входом второго элемента И и с 5-входом второго RS-триггера, выход которого соединен с вторым входом второго элемента И, третий вход которого объединен с S-входом первого RS-триггера, а четвертый выход первого дешифратора соединен с третьим входом второго элемента ИЛИ.

3

Ч

Составитель Э.Борисов Редактор И.Киштулинец Техред В.Кадар Корректор Л. Бескнд

4142/53

Тираж 901Подписное

ВПИШИ Государственного комитета СССР

по делам изобретений и открытий 13035, Москва, Ж-35, Раушская наб., д.4/5

Проично;1(тприно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

15

/7

Ко блоду

управляемого

19

делителя частоты //

18

20

Ко Bfody - упрадляемого

делителя частоты 11

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазометрическое устройство | 1983 |

|

SU1170873A1 |

| Фазометрическое устройство | 1984 |

|

SU1221611A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Фазометрическое устройство | 1982 |

|

SU1064225A1 |

| Фазометрическое устройство | 1980 |

|

SU917123A1 |

| Резервированный генератор импульсов | 1989 |

|

SU1619440A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1988 |

|

SU1700751A1 |

| ИЗМЕРИТЕЛЬ ФАЗ ОСЦИЛЛОГРАФИЧЕСКИЙ | 2005 |

|

RU2314543C2 |

| ПЕЛЕНГАТОР | 1991 |

|

RU2073880C1 |

Изобретение относится к радиотехнике и обеспечивает упрощение путем уменьшения объема блока памяти (БП). Дискретный фазовращатель (ДФВ) содержит задающий генератор (ЗГ) 1, делитель 2 частоты, формирователь 3 кодов базисных функний, БП 4, сумматор 5, ПАП 6, фильтр 7 нижних частот, блок 8 умножителей, блок II управления делителем частоты. В БП 4 записаны коэф. Фурье для всех дискретных фазовых сдвигов в пределах одного периода следования импульсов .ЗГ 1, на вход 9 подается сигнал управления в виде кодов, представляющих собой адреса ячеек памяти БП 4. Коэф. Фурье соответствует требуемому фазовому сдвигу. В качестве базисных функций, которые умножаются на коэф. Фурье, могут использоваться, например, функции Уолша. В результате сложения результатов перемножения, преобразования и фильтрации на выходе 10 формируется гармонический сигнал, фаза которого дискретно изменяется в пределах периода ЗН 1. Если фазовый сдвиг превышает период ЗГ 1, то с помощью блока 11, работа которого поясняется, осуществляется изменение на один период сигнала коэф. деления делителя 2. В результате происходит сдвиг выходного сигнала ДФВ на один период счетных импульсов делителя 2. В фазовращатель введен блок 11, состоящий из двух дещифра- торов, двух элементов RFTH, двух RS- триггеров и двух элементов И. 2 ил. « (Л Фиг ttiiof

| Механический грохот | 1922 |

|

SU41A1 |

| Радиотехнические цепи и сигналы | |||

| М.: Советское радио, 1971 , с.25. | |||

Авторы

Даты

1987-09-15—Публикация

1985-04-09—Подача