Изобретение относится к элек ро - технике и может быть испо:1ьзовано для раздельного управления непосре,т- стаенным преобразователем часто-ьь

Цель изобретения - повьи ение надежности работы и упр ощенио устройства.

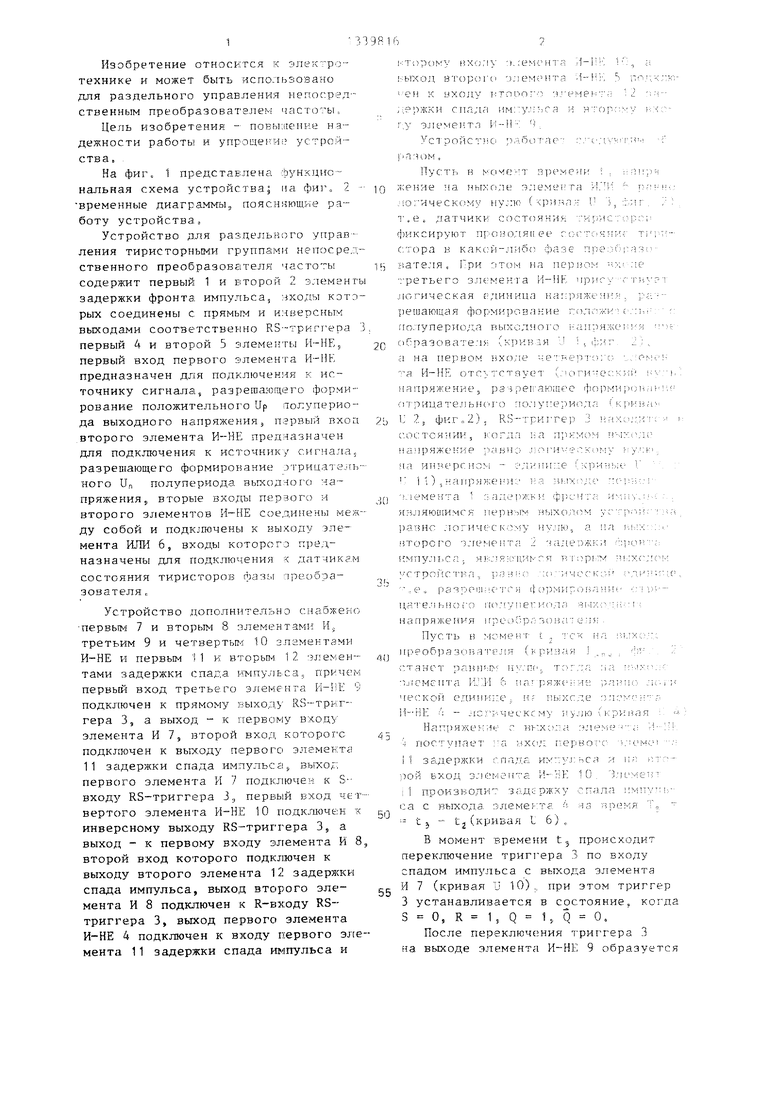

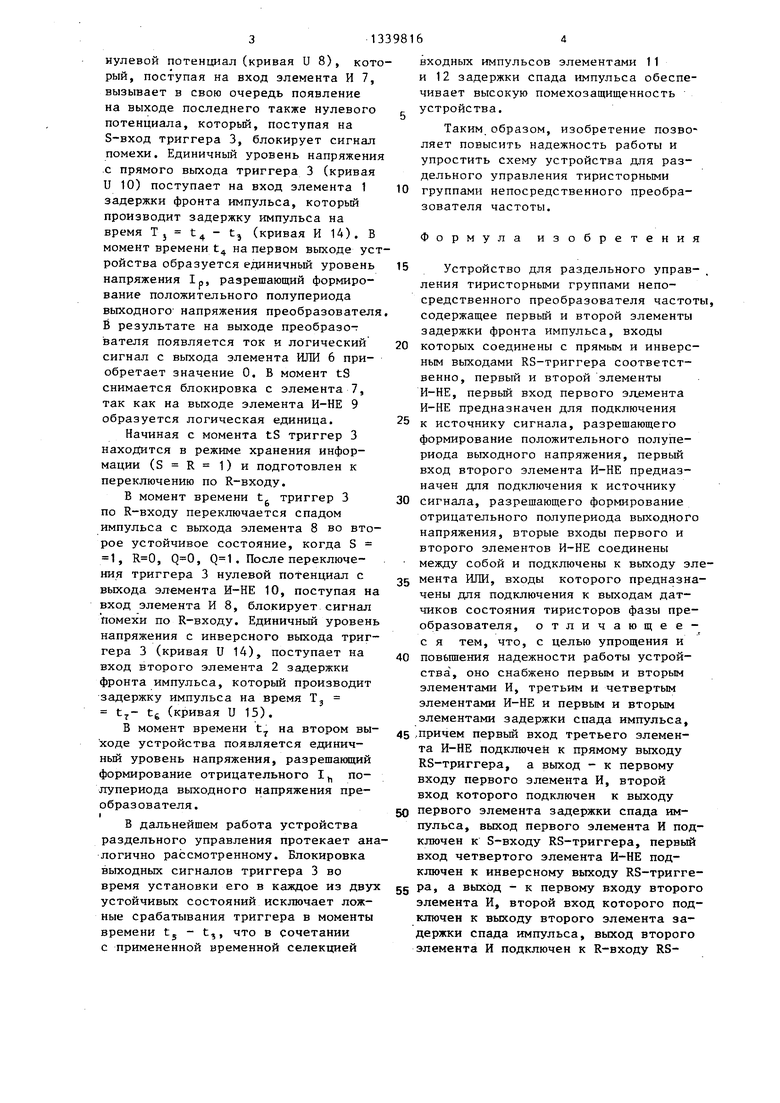

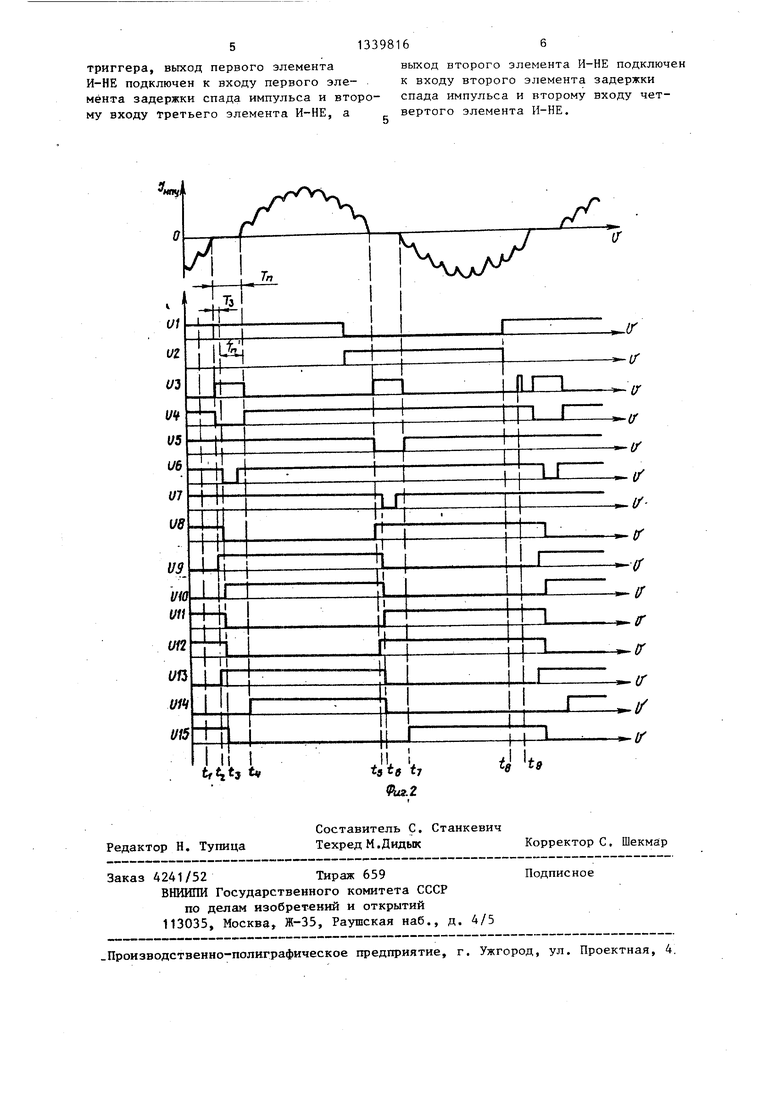

На фиг. 1 представлена функциональная схема устройства; иа фиг„ 2 временные диаграммы, поясняющие ра-- боту устройства

Устройство для раздельного управ - ления тиристорными группами непосре.Д ственного преобразователя часто гы содержит первый 1 и второй 2 элемент задержки фронта импульса, которых соединены с прямым и инверсным выходами соответственно К5- Триггера первый 4 и второй 5 злемемгты И-НЕ, первый вход первого элемента предназначен для подключенн к источнику сигнала, разрешающего формирование положительного Up полупериода выходного напряжения, пэрвый вход второго элемента И-НЕ пред;- азначен для подключения к источник/ сигнала, разрешающего формирование отрицате.иь кого Un полупериода выходного напряжения, вторые входы перзогс и второго элементов И-НЕ соединены между собой и подключены к выходу элемента ИЛИ 6, входы которого предназначены для подключения к датчикам состояния тиристоров фазы преобра- зователя.

Устройство дополнительно снабжено первым 7 и вторым 8 элементами И третьим 9 и четвертым: 10 злемектами И-НЕ и первым 11 и вторьм 12 элехен- тами задержки спада импульса, причем первый вход третьего элемента И-iiii подключен к прямому выходу Я3-три:г-- гера 3, а выход - к первому входу элемента И 7, второй вход которого подключен к вых.оду первого эл8мев:та 11 задержки спада импульса,, выход первого элемента И 7 подключен к S-входу RS-триггера 3, первый вход чет

вертого элемента И-НЕ 10 подключен к инверсному выходу КЗ-триггера 3, а выход - к первому входу элемента И 8 второй вход которого подключен к выходу второго элемента 12 задержки спада импульса, выход второго эле- мента И 8 подключен к R-входу RS- триггера 3, выход первого элемента И-НЕ 4 подключен к входу первого элемента 11 задержки спада импульса и

1-:тор)му :к:емента u-i: м., ;i --ыход BTciporo Л-и; 3 П т;-;. СМ к uxojiy Т тпоот о ij eiHei: ; ;: / ;- спада им::у. :ьса i; нтор: :;,- :;. гл i-i-H -: .

Усаройстж работ-ЛР г/ (-Л /ч i-Hi-i pa:U)M,

Пусть н ьч;1ме-т зреме-ги ; . л;ение ia ныхоле злемесга vipH - D;: т.е. датчики состояния Dpr i фиксируют П о}иэ;|;я11 ее гогтс яи;--; TIP стора в каксй-либо оазе гп ;е:: б; з гзателя , | ри на nepiiOM ле третьего sJitiN eH ia И-11К. upi ry логическая t-диница нагртиже ния . рл- - решающая формирование с ;:i,- fio. гупериода выходного т-апляжсм;: л юбраэователя чьржвтя J i ibnr j : , а на первом ixo;ie лр : яерлглгс; -..лом. а И-НЕ отпргстоуст (,, 4irii--е ллл ;- напряжение. рЗ -1 ре1гаю;цее формнр1Л,:л О7 рица тельнс ГО нол уперилрк; ( кг -лга- и 2, фиг. 2). RS-триггер 3 1Л1л; л,;лл лостсиниИ; 1 С;ГДП 1:а тлнллл; ,л гн .-е;:клг у г улкл на ит1черС1 ом - Лм )ил::.;г V П) , наиряженн:; -а лыхллл л(лалл ллемента ;-агр; ржки И л; ,лл, янляюишмск nepHbiM } ыхолпм ;,Л Р ЛЛ )авнс логи-lec , а на :. iiTopopo олемеллга 2 чалелжки импульса ; я1Л я;{лил- г п тлг;:р|:м н

рГТрПЙС ГНа, panip- :ci ЛЧССЛСЛЛ Л.

Л е рэярРШаС ТС-и ;м)мирО аиИ|- : иате.ч ьно го :( мегглтла ллл нааряже ия ирел(:ра лзиа : еas;

ПУСТЬ в ;-к: мент t , лрк и а :а.лл;- Л

i.iiCMCHTpi |p ;.i-i 6 па. ( ралпл л(.,1 ческой 5 и; пыхсде на/. -л- а И-Л1Ь :; - jic л-чнекс му ( :

НапряжегЛИ: г rirax; aa олелл- л: а- Р 4 поступает аа лхср: -iepBorc i 1 задержки ггшдк. има;л:ьса л па irv - V)OH БХОД э iiT iс i а с; Ь гм - KJ . лК Матл :1 производи задержку ргта.пл имтулап- са с выхода- элеме -:та -: аа лремя : , - t 5 tj(кривая L 6/ ,

В момент времени t. происходит переключение триггера 3 по входу спадом импульса с выхода элемента И 7 (кривая и 10)„ при этом триггер 3 устанавливается в состояние, когда 3 0, .,Q 0.

После переключения триггера 3 на выходе элемента И-НЕ 9 образуется

нулевой потенциал (кривая U 8), котрый, поступая на вход элемента И 7, вызывает в свою очередь появление на выходе последнего также нулевого потенциала, который, поступая на S-вход триггера 3, блокирует сигнал помехи. Единичный уровень напряжени .с прямого выхода триггера 3 (кривая и 10) поступает на вход элемента 1 задержки фронта импульса, который производит задержку импульса на время Tj t - t, (кривая И 14). В момент времени t на первом выходе усройства образуется единичный уровень напряжения „, разрешающий формирование положительного полупериода выходного напряжения преобразовател В результате на выходе преобразователя появляется ток и логический сигнал с выхода элемента ИЛИ 6 приобретает значение 0. В момент tS снимается блокировка с элемента 7, так как на выходе элемента И-НЕ 9 образуется логическая единица.

Начиная с момента tS триггер 3 находится в режиме хранения информации (S R 1) и подготовлен к переключению по R-входу.

В момент времени t триггер 3 по R-входу переключается спадом импульса с выхода элемента 8 во второе устойчивое состояние, когда S 1, , , . После переключения триггера 3 нулевой потенциал с выхода элемента И-НЕ 10, поступая на вход элемента И 8, блокирует сигнал Помехи по R-входу. Единичньш уровень напряжения с инверсного выхода триггера 3 (кривая и 14), поступает на вход второго элемента 2 задержки фронта импульса, который производит задержку импульса на время Tj tj (кривая и 15).

В момент времени t на втором выходе устройства появляется единичный уровень напряжения, разрешающий формирование отрицательного 1, по- Лупериода выходного напряжения преобразователя. I

В дальнейшем работа устройства

раздельного управления протекает анлогично рассмотренному. Блокировка выходных сигналов триггера 3 во время установки его в каждое из дву устойчивых состояний исключает ложные срабатывания триггера в моменты времени t - t,, что в сочетании с примененной временной селекцией

входных импульсов элементами 11 и 12 задержки спада импульса обеспечивает высокую помехозащищенность

устройства,

Таким образом, изобретение позволяет повысить надежность работы и упростить схему устройства для раздельного управления тиристорными группами непосредственного преобразователя частоты.

Формула изобретения

Устройство для раздельного управления тиристорными группами непосредственного преобразователя частоты, содержащее первый и второй элементы задержки фронта импульса, входы

которых соединены с прямым и инверсным выходами RS-триггера соответственно, первый и второй элементы И-НЕ, первый вход первого элемента И-НЕ предназначен для подключения

к источнику сигнала, разрешающего формирование положительного полупериода выходного напряжения, первый вход второго элемента И-НЕ предназначен для подключения к источнику

сигнала, разрешающего формирование отрицательного полупериода выходного напряжения, вторые входы первого и второго элементов И-НЕ соединены между собой и подключены к выходу элемента ИЛИ, входы которого предназначены для подключения к выходам датчиков состояния тиристоров фазы преобразователя, отличающее - с я тем, что, с целью упрощения и

повьш1ения надежности работы устройства , оно снабжено первым и вторым элементами И, третьим и четвертым элементами И-НЕ и первым и вторым элементами задержки спада импульса,

..причем первый вход третьего элемента И-НЕ подключен к прямому выходу RS-триггера, а выход - к первому входу первого элемента И, второй вход которого подключен к выходу

первого элемента задержки спада импульса, выход первого элемента И подключен к S-входу RS-триггера, первый вход четвертого элемента И-НЕ подключен к инверсному выходу RS-триггера, а выход - к первому входу второго элемента И, второй вход которого подключен к выходу второго элемента задержки спада импульса, выход второго элемента И подключен к R-входу RS513398166

триггера, выход первого элемента выход второго элемента И-НЕ подключен И-НЕ подключен к входу первого эле- . к входу второго элемента задержки мента задержки спада импульса и второ- спада импульса и второму входу четму входу третьего элемента И-НЕ, а

вертого элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство раздельного управления вентильными группами преобразователя частоты для асинхронного электропривода | 1988 |

|

SU1545305A1 |

| Логическое переключающее устройство для раздельного управления группами тиристорного циклоконвертора | 1980 |

|

SU1010715A1 |

| Устройство фиксации переходов через нуль периодического сигнала | 1984 |

|

SU1187145A1 |

| Логическое переключающее устройство для раздельного управления группами непосредственного преобразователя частоты | 1985 |

|

SU1319201A1 |

| Устройство для управления преобразователем постоянного напряжения,включающем резонансный тиристорный инвертор с транзисторным ключем на входе | 1982 |

|

SU1030945A1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| Устройство для моделирования графов Петри | 1986 |

|

SU1405070A1 |

| Резистивная нагревательная установка | 1984 |

|

SU1248082A1 |

| Импульсный преобразователь переменного тока в переменный | 1988 |

|

SU1508321A1 |

| Устройство для формирования управляющих импульсов @ -фазного преобразователя | 1983 |

|

SU1274092A1 |

Изобретение относится к электротехнике и может быть использовано и непосредственных преобразователях частоты. Цель изобретения - повышение надежности и упрощение. Блокировка выходных сигналов триггера 3 во время установки его в одно из устойчивых состояний исключает ложные срабатывания триггера, что в сочетании с временной селекцией входных импульсов элементами задержки 11 и 12 спада импульса обеспечивает поме- - .озашищенность устройства. 2 ил. S СО Х 00

| УСТРОЙСТВО РАЗДЕЛЬНОГО УПРАВЛЕНИЯ ТИРИСТОРНЫМИ ГРУППАМИ РЕВЕРСИВНОГО ПРЕОБРАЗОВАТЕЛЯ | 0 |

|

SU261547A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-09-23—Публикация

1985-11-21—Подача