Изобретение относится к измерительной технике и предназначено для использования при контроле динамических характеристик цифроаналоговых преобразователей.

Цель изобретения - повьшюние точности измерения времени установления

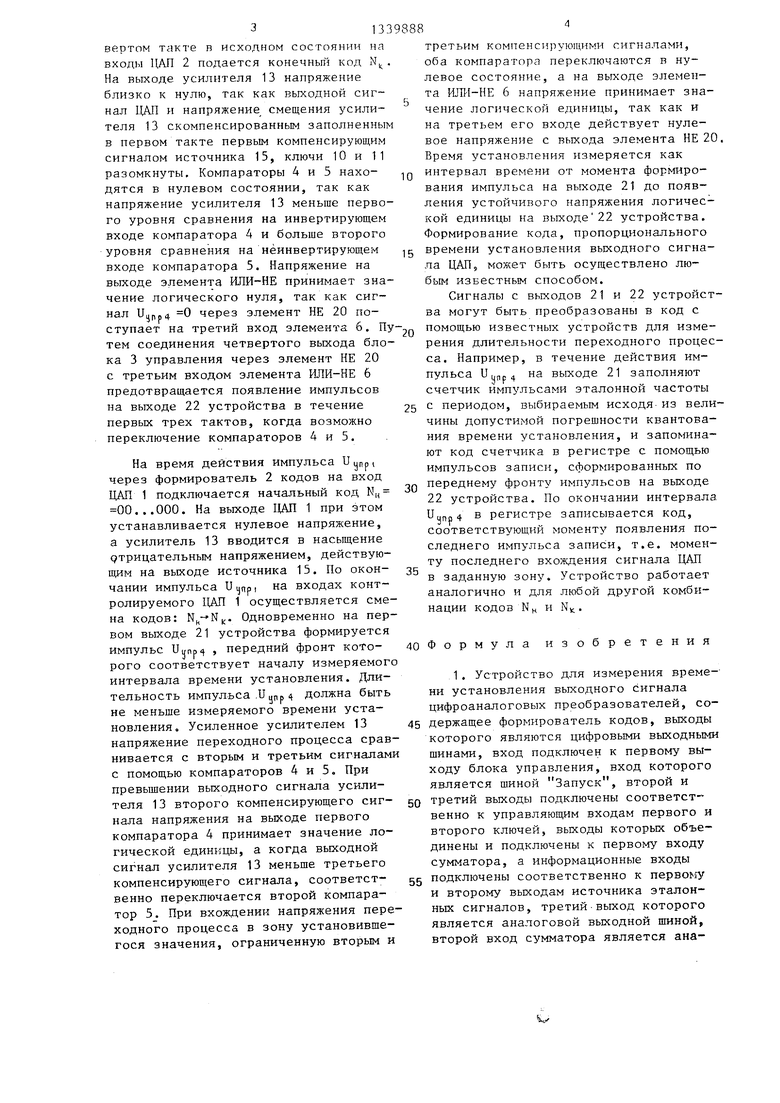

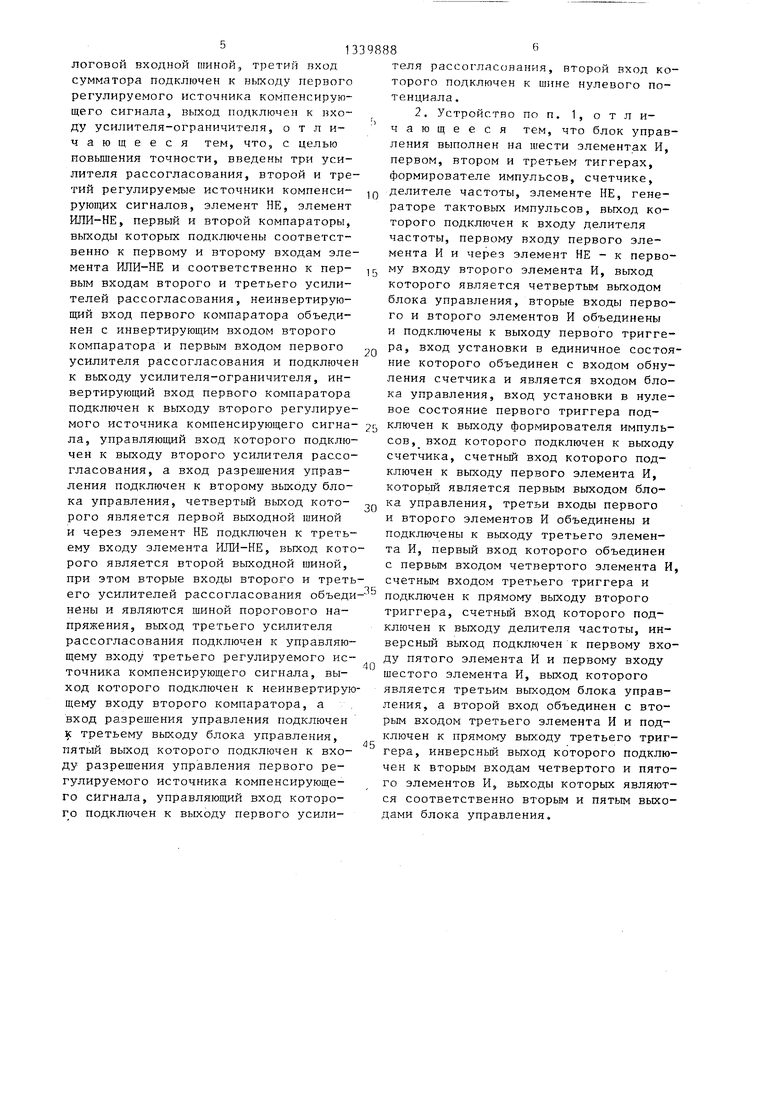

На фиг. 1 приведена функциональная схема устройства для измерения времени установления выходного сигнала цифроаналоговых преобразователей; на фиг. 2 - функциональная схема блока управления.

Контролируемый цифроаналоговый преобразователь (ЦАП) 1 (фиг. 1) подключается через соответствующие входные и выходные шины к устройству, ко- горое. содержит формирователь 2 кодов, блок 3 управления, первый и второй компараторы 4 и 5, элементы ИЛИ-НЕ 6, источник 7 эталонных сигналов, шину 8 Запуск, шину 9 порогового напряжения, первый и второй ключи 10 и 11, сумматор 12, усилитель-ограничитель 13, первый усилитель 14 рассогласования, первый и второй регулируемые источники 15 и 16 компенсирующих сигналов, второй усилитель 17 рассогласования, третий регулируемый источник 18 компенсирующего сигнала, третий усилитель 19 рассогласования, элемент НЕ 20, первую и вторую выходные шины 21 и 22„

Блок 3 управления (фиг. 2) выполнен на генераторе 23 тактовых импульсов, делитель 24 частоты, втором и третьем триггера : 25 и 26, третьем, пятом, четвертом и шестом элементах И 27 - 30, первом триггере 31, первом элементе И 32, элементе НЕ 33, втором элементе И 34, счетчике 35, формирователе 36 импульсов.

Устройство для измерения времени установления выходного сигнала цифроаналоговых преобразователей работает следующим образом,

В первых трех тактах на вход ЦАП 1 подключен конечньй код N, В первом

т акте сигналом Uyppj замыкается система автоматического регулирования, включающая сумматор 12., усилители 13 и 14 и первый источник 15 компенсирующего сигнала. Выходной сигнал усилителя 13 усиливается усилителем 14 и поступает на вход источника 15. Первый компенсирующий сигнал на выходе источника 15 изменяется до тех ndp, пока сигнал на выходе усилителя не

98882

станет равным нулю. Минимальная длительность первьк трех тактов зависит от быстродействия управляемых источ- g НИКОВ 13, 16 и 18. По окончании первого такта сигнал принимает значение логического нуля, источник 15 переводится в режим запоминания. Во втором такте сигналом Un.j замыкает10 ся ключ 10, на вход сумматора подключается сигнал сравнения с первого выхода источника 7 эталонных сигналов. С выхода усилителя 13 усиленный сигнал сравнения поступает на входы ком15 параторов 4 и 5. Во втором такте сигналом и

ijnpz

замыкается также система автоматического регулирования выходного сигнала компаратора 4, включающая гсомпаратор 4, источник 16 второго

0 компенсирующего сигнала и усили- ,

тель 17. Выходное напряжение компаратора 4 сравнивается с напряжением , Второй компенсирующий сигнал на выходе источника 16 в результате действия

5 отрицательной обратной связи автоматически изменяется до тех пор, пока выходное напряжение компаратора 4 не

сравняется с „ор Величина второго сигнала источника 16 зависит от по0 данного во втором такте сигнала на неинвертирующий вход компаратора 4, т.е. от величины сигнала сравнения, коэффициентов передачи сумматора 12 и усилителя 13, некомпенсированного

5 уровня на выходе усилителя 13, а также от величины напряжения смещения компаратора 4 и его чувственности (коэффициента усиления). По окончании второго такта ключ 10 раз0 мыкается, а источник 16 переводится в режим хранения. Второй компенсирующий сигнал на выходе источника 16 не измеряется до второго такта следующего цикла. В третьем такте сигна5 лом Uynp .замыкается ключ 11, подключающий на вход сумматора 12 проин- вертированньм сигнал сравнения с второго выхода источника 7 эталонных сигналов. На входы компараторов 4 и 5

Q поступает усиленный сигнал сравнения противоположного знака. Сигналом Unnpj замыкается система автоматического регулирования выходного напряжения компаратора 5. На выходе источника 18 устанавливается третий компенсирующий сигнал соответствующей величины и знака. По окончании третьего такта ключ 11 р.азмыкается, а источник 18 переносится в режим хранения. В чет5

3133

вертом такте в исходном состоянии на входы ДАЛ 2 подается конечньш код N. На выходе усилителя 13 напряжение близко к нулю, так как выходной сигнал ЦА11 и напряжение смещения усилителя 13 скомпенсированным заполненным в первом такте первым компенсирующим сигналом источника 15, ключи 10 и 11 разомкнуты. Компараторы 4 и 5 находятся в нулевом состоянии, так как напряжение усилителя 13 меньше первого уровня сравнения на инвертирующем входе компаратора 4 и больше второго уровня сравнения на неинвертирующем входе компаратора 5. Напряжение на выходе элемента Ш1И-НЕ принимает значение логического нуля, так как сигнал Uijf,p4 0 через элемент НЕ 20 поступает на третий вход элемента 6. Путем соединения четвертого выхода блока 3 управления через элемент НЕ 20 с третьим входом элемента ИЛИ-НЕ 6 предотвращается появление импульсов на выходе 22 устройства в течение первых трех тактов, когда возможно переключение компараторов 4 и 5.

На время действия импульса Uynp, через формирователь 2 кодов на вход ЦАП 1 подключается начальный код К ц 00...000. На выходе ПДП 1 при этом устанавливается нулевое напряжение, а усилитель 13 вводится в насыщение отрицательным напряжением, действующим на выходе источника 15. По окончании импульса U

на входах контролируемого ЦАП 1 осуществляется смена кодов: . Одновременно на первом выходе 21 устройства формируется импульс Uijnp j , передний фронт которого соответствует началу измеряемого интервала времени установления. Длительность импульса ,и upр 4 должна быть не меньше измеряемого времени установления. Усиленное усилителем 13 напряжение переходного процесса сравнивается с вторым и третьим сигналами с помощью компараторов 4 и 5. При превьш1ении выходного сигнала усилителя 13 второго компенсирующего сигнала напряжения на выходе первого компаратора 4 принимает значение логической единицы, а когда выходной сигнал усилителя 13 меньше третьего компенсирующего сигнала, соответственно переключается второй компаратор 5. При вхождении напряжения переходного процесса в зону установившегося значения, ограниченную вторым и

третьим компенсирующими сигналами, оба компаратора переключаются в нулевое состояние, а на выходе элемента ИЛИ-НЕ 6 напряжение принимает значение логической единицы, так как и на третьем его входе действует нулевое напряжение с выхода элемента НЕ 20. Время установления измеряется как интервал времени от момента формирования импульса на выходе 21 до появления устойчивого напряжения логической единицы на выходе 22 устройства. Формирование кода, пропорционального времени установления выходного сигнала ЦАП, может быть осуществлено любым известным способом.

Сигналы с выходов 21 и 22 устройства могут быть преобразованы в код с помощью известных устройств для измерения длительности переходного процесса. Например, в течение действия импульса U(n на выходе 21 заполняют

счетчик импульсами эталонной частоты с периодом, выбираемым исходя-из величины допустимой погрешности квантования времени установления, и запоминают код счетчика в регистре с помощью импульсов записи, сформированных по переднему фронту импульсов на выходе 22 устройства. По окончании интервала Uunn4 в регистре записывается код, соответствующий моменту появления последнего импульса записи, т.е. моменту последнего вхождения сигнала ЦАП в заданную зону. Устройство работает аналогично и для любой другой комбинации кодов NH и Ny.

Формула изобретения

1. Устройство для измерения време-- ни установления выходного сигнала цифроаналоговых преобразователей, со- держащее формирователь кодов, выходы которого являются цифровыми выходными шинами, вход подключен к первому выходу блока управления, вход которого является шиной Запуск, второй и третий выходы подключены соответственно к управляю цим входам первого и второго ключей, выходы которых объединены и подключены к первому входу сумматора, а информационные входы подключены соответственно к первому и второму выходам источника эталонных сигналов, третий-выход которого является аналоговой выходной шиной, второй вход сумматора является ана

лотовой входной шиной, третий вход сумматора подключен к выходу первого регулируемого источника компенсирующего сигнала, выход подключен к входу усилителя-ограничителя, отличающееся тем, что, с целью повышения точности, введены три усилителя рассогласования, второй и третий регулируемые источники компенси- руюп1ИХ сигналов, элемент НЕ, элемент ИЛИ-НЕ, первый и второй компараторы, выходы которых подключены соответственно к первому и второму входам элемента ИЛИ-НЕ и соответственно к первым входам второго и третьего усилителей рассогласования, неинвертирующий вход первого компаратора объединен с инвертирующим входом второго компаратора и первым входом первого усилителя рассогласования и подключен к выходу усилителя-ограничителя, инвертирующий вход первого компаратора подключен к выходу второго регулируемого источника компенсирующего сигна- 25 ключен к выходу формирователя импуль

ла, управляющий вход которого подключен к выходу второго усилителя рассогласования, а вход разрешения управления подключен к второму выходу блока управления, четвертый выход кото- рого является первой выходной шиной и через элемент НЕ подключен к третьему входу элемента ИЛИ-НЕ, выход которого является второй выходной шиной, при этом вторые входы второго и третьего усилителей рассогласования объеди нены и являются шиной порогового напряжения, выход третьего усилителя рассогласования подключен к управляющему входу третьего регулируемого источника компенсирующего сигнала, выход которого подключен к неинвертирующему входу второго компаратора, а вход разрешения управления подключен к третьему выходу блока управления, пятый выход которого подключен к входу разрешения управления первого регулируемого источника компенсирующего сигнала, управляющий вход которого подключен к выходу первого усили

0

5

0

теля рассогласования, второй вход которого подключен к шине нулевого потенциала .

2. Устройство по п. 1, отличающееся тем, что блок управления выполнен на шести элементах И, первом, втором и третьем тиггерах, формирователе импульсов, счетчике, делителе частоты, элементе НЕ, генераторе тактовых импульсов, выход которого подключен к входу делителя частоты, первому входу первого элемента И и через элемент НЕ - к первому входу второго элемента И, выход которого является четвертым выходом блока управления, вторые входы первого и второго элементов И объединены и подключены к выходу первого триггера, вход установки в единичное состояние которого объединен с входом обнуления счетчика и является входом блока управления, вход установки в нулевое состояние первого триггера под5

0

5

СОВ, вход которого подключен к выходу счетчика, счетньй вход которого подключен к выходу первого элемента И, который является первым выходом блока управления, третьи входы первого и второго элементов И объединены и подключены к выходу третьего элемента И, первый вход которого объединен с первым входом четвертого элемента И, счетным входом третз его триггера и подключен к прямому выходу второго триггера, счетный вход которого подключен к выходу делителя частоты, ин- версньй выход подключен к первому входу пятого элемента И и первому входу шестого элемента И, выход которого является третьим выходом блока управления, а второй вход объединен с вторым входом третьего элемента И и подключен к прямому выходу третьего триггера, инверсный выход которого подключен к вторым входам четвертого и пятого элементов И, выходы которых являются соответственно вторым и пятым выходами блока управления.

„ Пуск

блон t/прадленир

Я орпиродитель

Упр.

Ugnp.lt

Срие. 2

Составитель В.Першиков Редактор Л.Гратшшо Техред Л.Сердюкова Корректор М.Пожо

Заказ 4245/55 Тираж 901Подписное

ВНИРШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская иаб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения времени установления выходного тока цифро-аналоговых преобразователей | 1986 |

|

SU1464287A1 |

| Устройство для измерения времени установления цифроаналогового преобразователя | 1986 |

|

SU1432776A1 |

| Измеритель динамических параметров цифроаналоговых преобразователей | 1986 |

|

SU1370787A1 |

| Устройство для измерения времени установления выходного сигнала цифроаналоговых преобразователей | 1985 |

|

SU1275766A1 |

| КАЛИБРОВОЧНОЕ УСТРОЙСТВО ДЛЯ УЛЬТРАЗВУКОВОГО РАСХОДОМЕРА | 1995 |

|

RU2082951C1 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1990 |

|

SU1716601A2 |

| Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления | 1987 |

|

SU1494216A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1425832A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

Изобретение относится к измерительной технике и предназначено для использования при контроле динамических характеристик цифроаналоговых преобразователей (ЦАП). Цель - повышение точности. Контролируемый ЦАП 1 подключается через соответствующие входные и выходные шины к устройству, которое содержит формирователь 2 кодов, блок 3 управления, первый и второй компараторы 4, 5, элемент 6 РШИ-НЕ, источник 7 эталонных сигналов, шину 8 Запуск, шину 9 порогового напряжения, первый и второй ключи 10, 11, сумматор 12, усилитель- ограничитель 13, первый усилитель 14 рассогласования, первый и второй регулируемые источники 15, 16 компенсирующих сигналов, второй усилитель 17 рассогласования, третий регулируемый источник 18 компенсирз тощего сигнала, третий усилитель 19 рассогласования, элемент 20 НЕ, первую и вторую выходные шины 21, 22. Точность измерения времени установления повышается благодаря тому, что операции сравнения выходного сигнала ЦАП с сигналами, формирующими зону установления, осуществляется с помощью компараторов 4, 5. 1 з.п. ф-лы, 2 ил. ( С fJOff со со со 00 00 00 „Пуск fJynp.if Физ.г

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1979 |

|

SU790298A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для измерения времени установления выходного сигнала цифроаналоговых преобразователей | 1985 |

|

SU1275766A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-23—Публикация

1985-08-27—Подача