Изобретение относится к автоматике и вычислительной технике и может . быть использовано для связи аналого- источников информации с цифровым вычислительным устройством,

Цель изобретения - уменьшение ди- намической погрешности преобразователя путем уменьшения времени переходных процессов при отработке рас- Согласований.

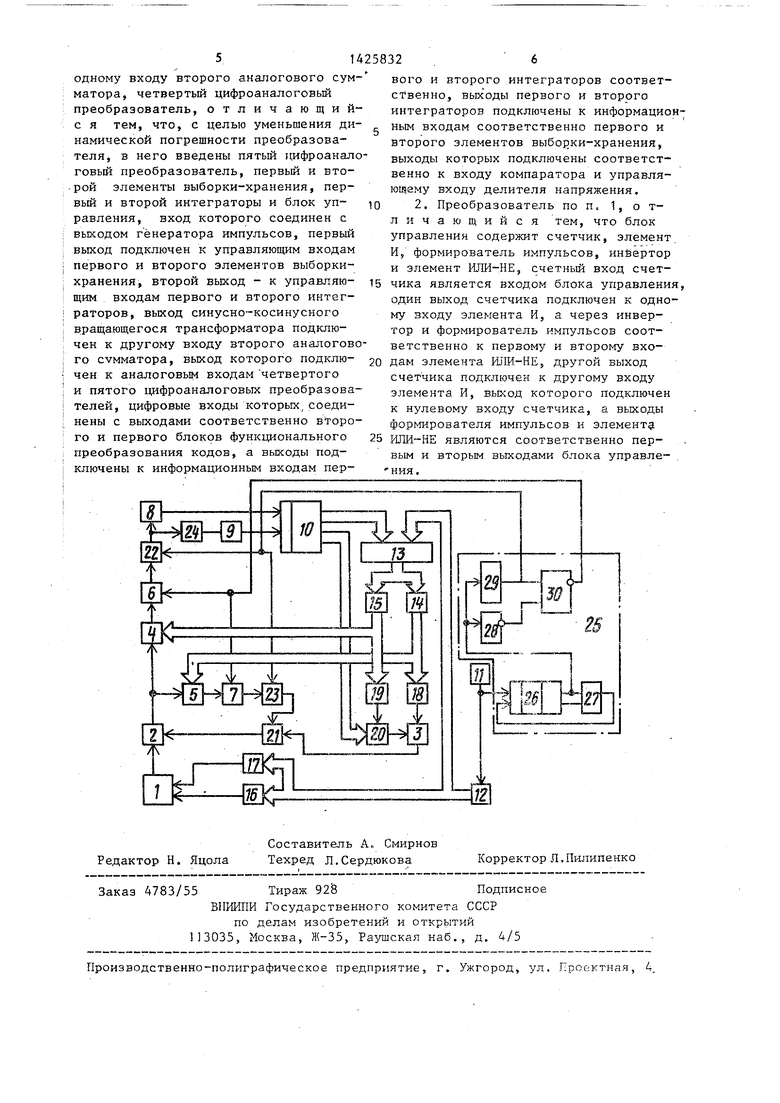

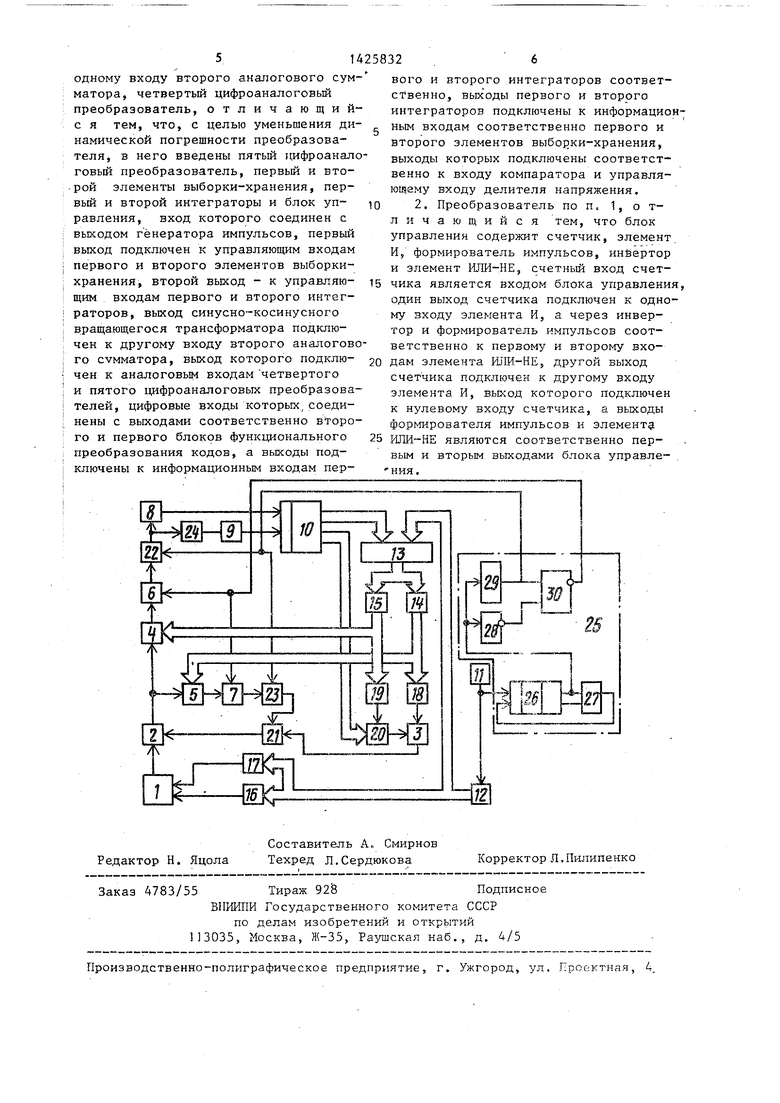

; На чертеже представлена структурная схема преобразователя.

Преобразователь содержит синусно- косинусный вращаюЕЩЙся трансформатор ;(СКВТ) 1, аналоговые сумматоры 2 и 3 эцифроаналоговые преобразователи (ЦАП 4 и 5, интеграторы 6 и 7, компаратор 8, блок 9 преобразования напряжения в частоту, реверсивньй счетчик 10, генератор 11 импульсов, делитель 12 частоты, цифровой сумматор 13, блоки 14 и 15 функционального преобразования кодов, формирователи 16 и 17 питающих напряжений, ЦАП 18-20, делитель 21 напряжения, элементы 22 ;и 23 выборки - хранения, блок 24 вы- ;Деления модуля, блок 25 з правленияа |Влок 25 управления содержит счетчик 26, элемент И 27, инвертор 28, фор- шpoвaтeль 29 импульсов и элемент lOTi-HE 30.

Преобразователь угла поворота на- ла и код работает следующим образомо

От генератора 11 импульсы посту- -яают- на делитель 12 частоты Значени разрядов делителя 12 частоты подаются на входы формирователей 16 и 17 синусоидальных «напряжений питания, |соторые подаются на входы СКВТ 1 .

Компенсационное напряжение, посту иающее на вход аналогового сумматора 2 со сдвигом фазы, задаваемым кодом реверсивного счетчика 10, формируется грубо-точным способом. Формиррва- ние синусоидального сигнала со сдви гом фазы в преде/iax п старших разрядов реверсивного счетчика 10 осуществляется путем И, сложения с выходами разрядов делителя 12 частоты в сумматоре 13. Выходной код сумматора 13, представляющий собой линейно изменяющийся код со сдвигом фазы относительно выходного кода делителя 1 частоты на величину, задаваемую кодо п старших разрядов реверсивного счет чика 10, преобразуется блокаь и 14 и в коды синуса и косинуса. Блоки 14 SS 15 представляют собой блоки пос.то

янной памяти с прошивкой функций синуса и косинуса. ЦАП 18 и 19 преобразуют выходные коды блоков 14 и 15 в напряжение. На выходах ЦАП 18 и 19 формируются напряжения, аппроксимирующие синусоидальные и косинусоидаль- ные функции выходных кодов сумматора 13 со сдвигом фаз относительно выходных сигналов формирователей 16 и 17 синусоидальных напряжений на величину, задаваемую грубо кодом старпгах п разрядов реверсивного счётчика 10. Фазовый сдвиг выходного сигнала ЦАП 18 в пределах кванта выходного кода сзжматора 13 осуществляется путем его суммирования в аналоговом сумматоре 3 с выходным сигналом ЦАП 19, промодулированным по амгшитуде в ЦАП 20 кодом m млацпшх разрядов реверсивного счетчика 10. Согласование величин сдвигов фаз, задаваемых кодами младших и старших разрядов реверсивного счетчика 10, осуществляется при помощи задания коэффициентов суммиро- вания в аналоговом сумматоре 3 выходных напряжений ЦАП 18 и 20.

Сформированное компенсащ-юнное напряжение с выхода аналогового сумматора 3 через управляемый делитель 21 напряжения и выходное напряжение СКВТ 1 подаются на входы аналогового сумматора 2.. .

Для .малых значений разбалансов фаз ,щ и амплитуд U, соответствующих основному режиму работы преобразователя угла повороти вала в код, выходной сигнал .сулкатора 2 на основной частоте СЭ можно представить выражением

и.: UCaUsinot + 6.i|cosut).

Выходное напряжение аналогового сумматора 2 умножается в ЦАП 4 и 5 на коды косинуса и синуса, сформированные в блоках 15 и 14 соответственно. Выходные сигналы ЦАП 4 и 5 интег- i рируются в течение периода Т -г- в

ш

интеграторах 6 и 7 сооветственно. Выходные напряжения интеграторов 6 и 7 в момент времени Т после начала интегрирования пропорциональны соответ- ственно разности фаз ucf и разбалансу амплитуд ьи между выходным напряжением СКВТ 1 и компенсирующим напряжением с выхода делителя 21.

Временные режимы (циклы) работы интеграторов 6 и 7 элементов 22 и 23 выборки-хранения задаются при по- мопщ блока 25 управления. Один цикл преобразования задается немногим больше времени одно1 о периода Т напряже-. НИИ питания СКВТ 1 при помощи деления частоты генератора 11 на 2 + 2 в делителе и его сброса выходным им- пульсом элемента И 27.

Управляющий импульс элементов 22 и 23 выборки -хранения вырабатывает злемен7 29 по переднему фронту импульсов П+1-ГО разряда делителя часто- ты. Импульс, управляющий сбросом интеграторов 6 к 7, вырабатывается гфи ПОМОЯ1И элемента И и элемента ШШ-НЕ 30 из импульсов n+t-ro разряда делителя частоты и выходных импульсов элемента 29. Р1мпульсы сброса интегр а- торов 6 и 7 начинаются в моменты окончания импульсов, управляющих элементами 22 и 23 выборки-хранения, и

оканчиваются в моменты, когда начина- 25 ется новый цикл деления делителя частоты. Таким образом, в каждом цикле преобразования на выходе элементов 22 JH 23 выборки-хранения выделяются и хранятся постоянные напряжения, и второго формирователей питающих на- порциональные соответственно величи- пряжений, выходы которых подключены

1. Преобразователь угла поворота вала в код, содержащий компаратор, генератор импульсов, выход которого подключен к входу делителя частоты, выходы разрядов делителя частоты подключены к первой группе входов цифрового сумматора и входам первого

преобразования, то требуется автоматически регулировать ее до минимума. Минимизация разности амплитуд bU осуществляется при помощи следящей системы, состоящей из аналогового сумматора 2, ЦАП 5р интегратора 7, элемента 23 выборки-хранения и управляемого делителя 2 напряжения, путем преобразования величины разности амплитуд ли выходного напряжения СКВТ 1 и компенсирующего напряжения в про- пор1щокальное ему постоянное напряжение которое изменяет величину коэффициента передачи управляемого делителя 21 напряжения, изменяя таким образом амплитуду компенсирующего напряжения до сведения к нулю разности амплитуд..

Формула изобретения

и второго формирователей питающих на- пряжений, выходы которых подключены

1. Преобразователь угла поворота вала в код, содержащий компаратор, генератор импульсов, выход которого подключен к входу делителя частоты, выходы разрядов делителя частоты подключены к первой группе входов цифрового сумматора и входам первого

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478331A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1312737A1 |

| Следящий преобразователь угла поворота вала в код | 1983 |

|

SU1116446A1 |

| Преобразователь угла поворота вала в код | 1989 |

|

SU1633492A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478332A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1451861A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ В КОД | 1991 |

|

RU2007027C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ МНОГОЭЛЕМЕНТНОГО ПРИЕМНИКА | 1992 |

|

RU2025905C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1320902A1 |

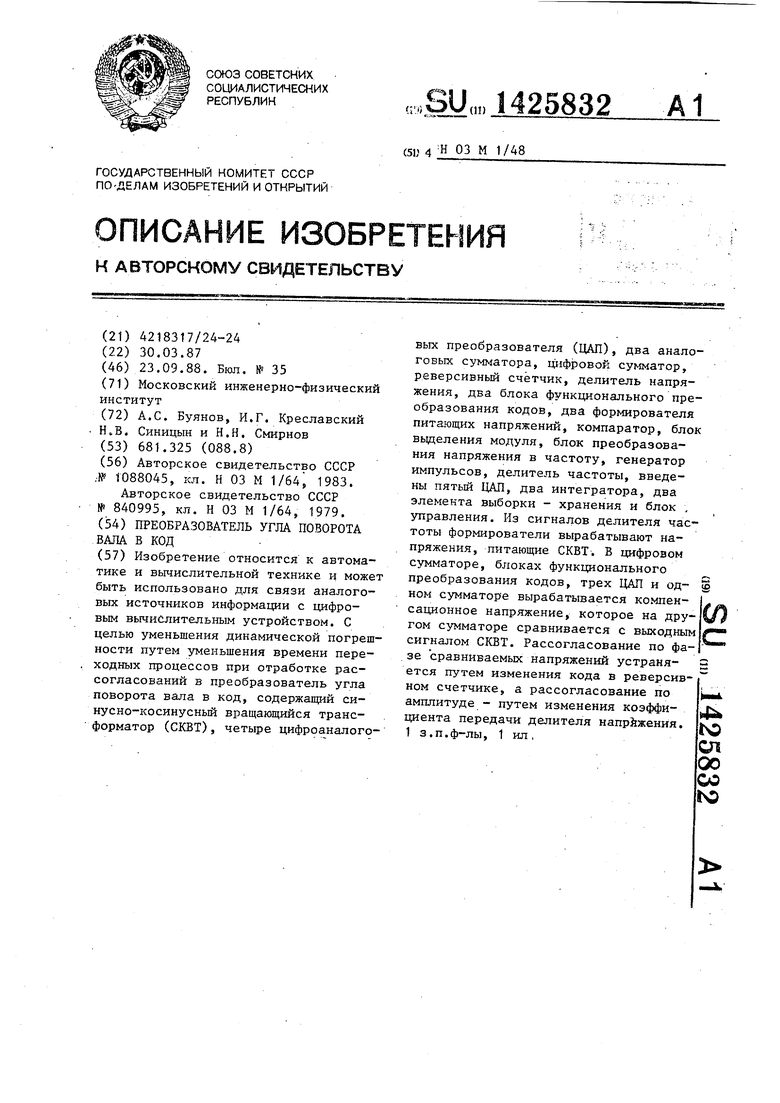

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью уменьшения динамической погрешности путем уменьшения времени переходных процессов при отработке рассогласований в преобразователь угла поворота вала в код, содержапщй си- нусно-косинусньй вращающийся трансформатор (СКВТ), четыре цифроаналоговьгх преобразователя (ЦАП), два аналоговых сумматора, 1Ц1фровой сумматор, реверсивный счётчик, делитель напряжения, два блока функционального преобразования кодов, два формирователя питающих напряжений, компаратор, блок выделения модуля, блок преобразования напряжения в частоту, генератор импульсов, делитель частоты, введены пятьш ЦАП, два интегратора, два элемента выборки - хранения и блок , управления. Из сигналов делителя частоты формирователи вырабатывают напряжения, питающие СКВТ. В цифровом сумматоре, блоках функционального преобразования кодов, трех ЦАП и одном сумматоре вырабатывается компенсационное напряжение, которое на другом сумматоре сравнивается с выходным сигналом СКВТ. Рассогласование по фазе сравниваемых напряжений устраняется путем изменения кода в реверсивном счетчике, а рассогласование по амплитуде - путем изменения коэффициента передачи делителя напрйженйя. 1 3.п.ф-лы, 1 ил, с 4 ГО 01 00 со to

нам фазового ЛСр и амплитудного U.U разбалансов выходного напряжения СКВТ 1 и компенсирующего напряжения.

Информацию о разности сдвигов фаз выходного напряжения СКВТ 1 и компен- сирующе.го напряжения, т.е. о разности углового положения вала СКВТ 1 и выходного кода преобразователя, представленного кодом реверсивного счетчика 10, несет напряжение на выходе элемента 22 выборки-хранения, которое преобразуется компаратором 8 .в сигнал направления счета реверсив35

40

к входам синусно-косинусного вращающегося трансформатора, вход компаратора соединен с входом блока выделения модуля, выход.которого подключен к входу блока преобразования напряжения в частоту, выход которого и выход компаратора подключены соответственно к счетному и управляющему входам реверсивного счетчика, выходы старших разрядов реверсивного счетчика под-, ключены к второй rpjTine входов цифрового сумматора, а выходы младших

50

разрядов - к Цифровым входам первого него счетчика 10, а блоком 24 выделе- цифроаналогового преобразователя, вы- ния модуля напряжения и блоком 9 пре- ходы цифрового сумматора подключены образования напряжения в частоту - в последовательность счетных импульсов реверсивного счетчика. 10. Код реверсивного счетчика 10 изменяется до сведения к нулю разности фаз выходного напряжения СКВТ 1 и компенсирующего напряжения.

Разность амплитуд uU выходного напряжения СКВТ 1 и компенсирующего на- , .. ..

пряжения не является носителем инфор- рого цифроаналоговых преобраэовате- мации об угловом положении вала СКВТ лей подключены к входам первого ана- 1. Однако поскольку наличие разности логового сумматора, выход которого че- амгош уд uU приводит к погрешности рез делитель напряжения подключен к

к входам первого и второго блоков функционального преобразования кодов, выходы которых подключены к входам соответственно второго, и третьего цифроаналоговых преобразователей, j выход третьего цифроаналогового пре-, образователя подключен к аналоговому входу первого цифроаналогового преобразователя, выходы первого и вто

к входам синусно-косинусного вращающегося трансформатора, вход компаратора соединен с входом блока выделения модуля, выход.которого подключен к входу блока преобразования напряжения в частоту, выход которого и выход компаратора подключены соответственно к счетному и управляющему входам реверсивного счетчика, выходы старших разрядов реверсивного счетчика под-, ключены к второй rpjTine входов цифрового сумматора, а выходы младших

разрядов - к Цифровым входам первого цифроаналогового преобразователя, вы- ходы цифрового сумматора подключены

, .. ..

рого цифроаналоговых преобраэовате- лей подключены к входам первого ана- логового сумматора, выход которого че- рез делитель напряжения подключен к

к входам первого и второго блоков функционального преобразования кодов, выходы которых подключены к входам соответственно второго, и третьего цифроаналоговых преобразователей, j выход третьего цифроаналогового пре-, образователя подключен к аналоговому входу первого цифроаналогового преобразователя, выходы первого и вто

| Преобразователь угла поворота вала в код | 1983 |

|

SU1088045A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Двухотсчетный преобразователь углапОВОРОТА ВАлА B КОд | 1979 |

|

SU840995A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-30—Подача