5

верок. При двойной ошибке разряды синдрома дают четную комбинацию, так как сумма по модулю два двух вектор- столбцов проверочной матрицы, соот113398982

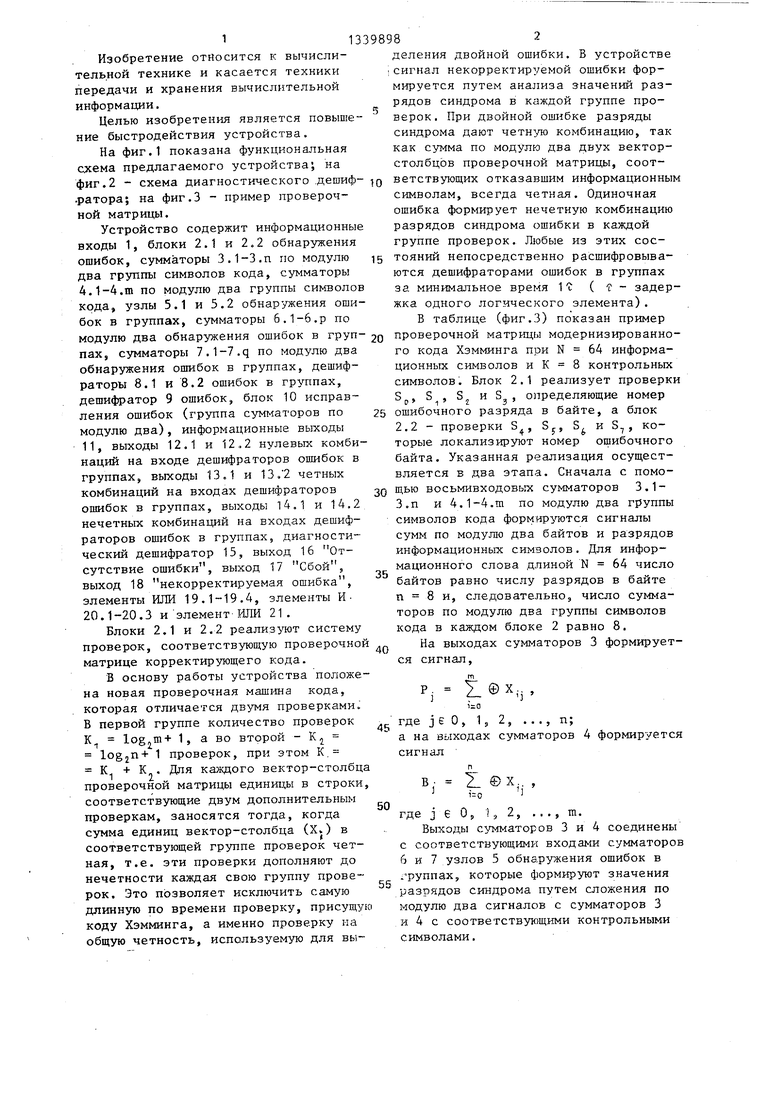

Изобретение относится к вычисли- деления двойной ошибки. В устройстве тельной технике и касается техники :сигнал некорректируемой ошибки фор- передачи и хранения вычислительной мируется путем анализа значений раз- информации. рядов синдрома в каждой группе проЦелью изобретения является повышение быстродействия устройства.

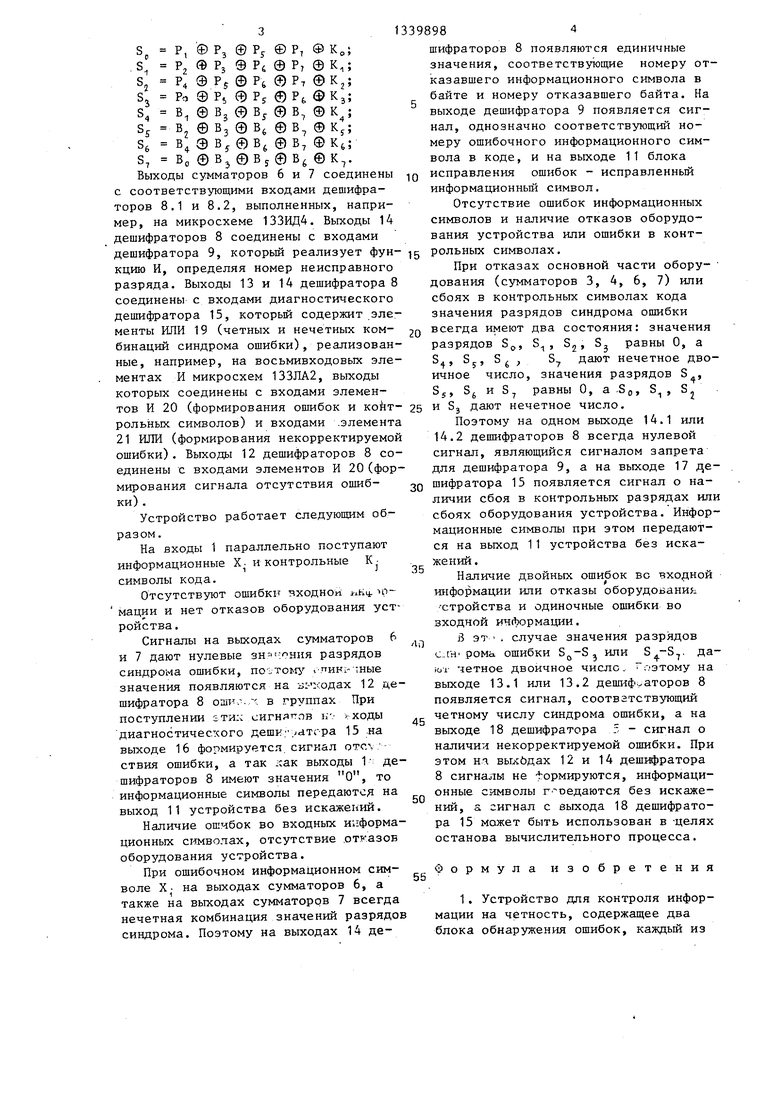

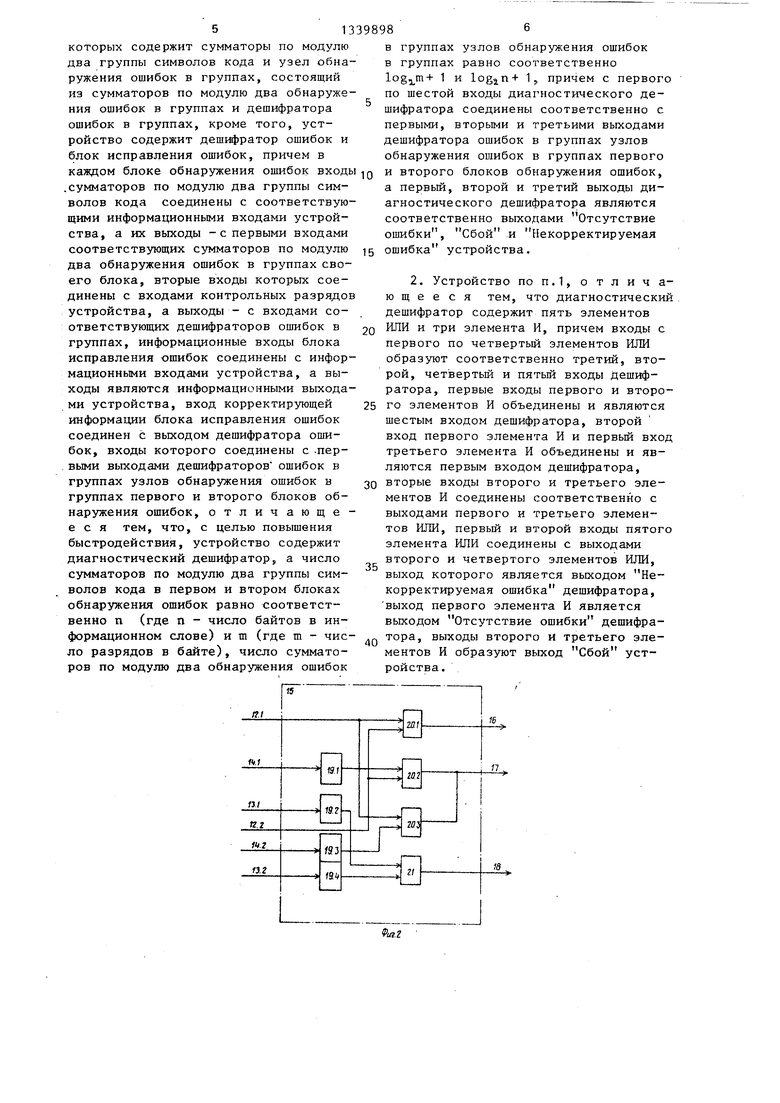

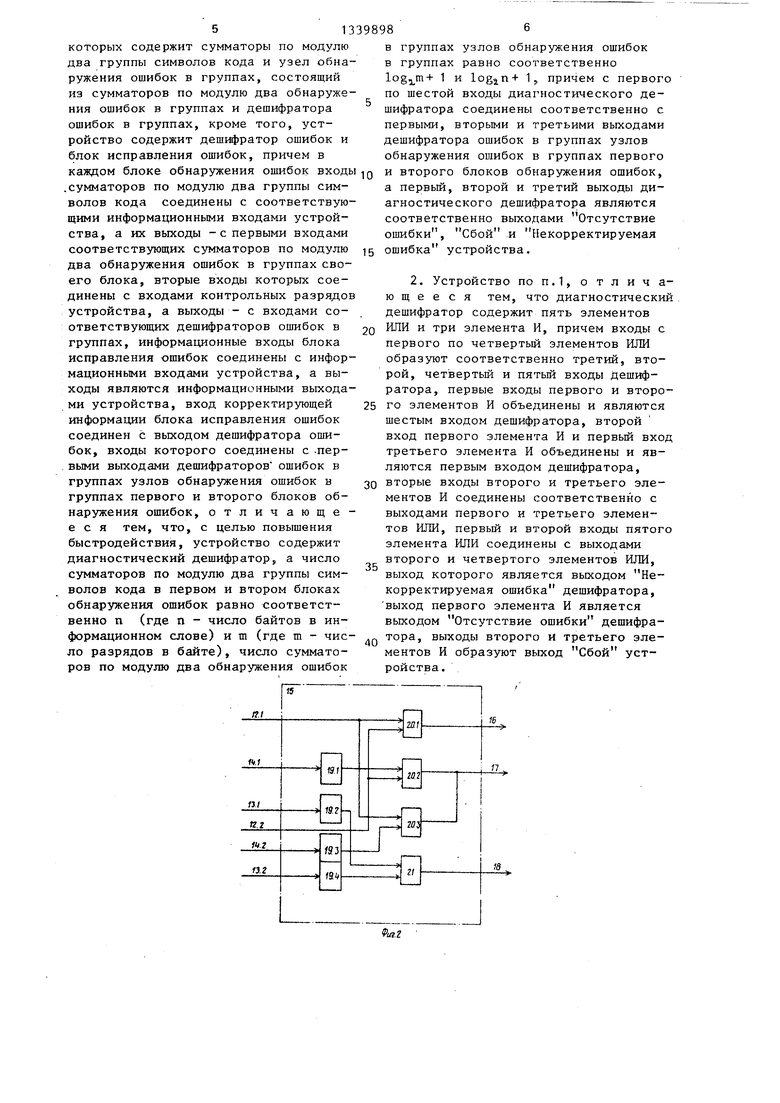

На фиг.1 показана функциональная схема предлагаемого устройства; на фиг.2 - схема диагностического дешиф- ig ветствующих отказавшим информационным .ратора; на фиг.З - пример провероч- символам, всегда четная. Одиночная ной матрицы.ошибка формирует нечетную комбинацию

Устройство содержит информационные разрядов синдрома ошибки в каждой входы 1, блоки 2.1 и 2.2 обнаружения группе проверок. Любые из этих сос- ошибок, сумматоры 3.1-З.п по модулю 15 тояний непосредственно расшифровыва- два группы символов кода, сумматоры ются дешифраторами ошибок в группах 4.1-4.tn по модулю два группы символов за минимальное время 1 L ( f - задер- кода, узлы 5.1 и 5.2 обнаружения оши- жка одного логического элемента). бок в группах, сумматоры 6.1-6.р по В таблице (фиг.З) по казан пример модулю два обнаружения ошибок в груп- 2о проверочной матрицы модернизированно- пах, сумматоры 7.1-7.q по модулю два го кода Хзмминга при N 64 информационных символов и К 8 контрольньгх символов. Блок 2.1 реализует проверки

обнаружения ошибок в группах, дешифраторы 8.1 и 8.2 ошибок в группах, дешифратор 9 ошибок, блок 10 исправления ошибок (группа сумматоров по модулю два), информационные выходы 11, выходы 12.1 и 12,.2 нулевых комбинаций на входе дешифраторов ошибок в группах, выходы 13.1 и 13. 2 четных комбинаций на входах дешифраторов ошибок в группах, выходы 14.1 и 14.2 нечетных комбинаций на входах дешифраторов ошибок в группах, диагностический дешифратор 15, выход 16 Отсутствие ошибки, выход 17 Сбой, выход 18 некорректируемая ошибка, элементы ИЛИ 19.1-19.4, элементы И- 20.1-20.3 и элемент ИЛИ 21.

Блоки 2.1 и 2.2 реализуют систему

с с

}

5 II 5 , определяющие номер 25 ошибочного разряда в байте, а блок 2.2 - проверки S, S, S и S, которые локализируют номер ошибочного байта. Указанная реализация осуществляется в два этапа. Сначала с помо- 30 Щью восьмивходовьж сумматоров 3.1- З.п и 4.1-4.m по модулю два группы символов кода формируются сигналы сумм по модулю два байтов и разрядов информационных символов. Для информационного слова длиной N 64 число байтов равно числу разрядов в байте п 8 и, следовательно, число сумматоров по модулю два группы символов

35

j 1.©Х,.,,

g- где je О, 1, 2, ..., п;

а на выходах сумматоров 4 формируется

сигнал

кода в каждом блоке 2 равно 8. проверок, соответствующую проверочной На выходах сумматоров 3 формирует- матрице корректирующего кода.ся сигнал,

В основу работы устройства положена новая проверочная машина кода, которая отличается двумя проверками. В первой группе количество проверок К log,m+ 1, а во второй - К 1о§2П+ 1 проверок, при этом К. К + К . Для каждого вектор-столбца проверочной матрицы единицы в строки, соответствующие двум дополнительным проверкам, заносятся тогда, когда сумма единиц вектор-столбца (Х.) в соответствующей группе проверок четная, т.е. эти проверки дополняют до нечетности каждая свою группу проверок. Это позволяет исключить самую длинную по времени проверку, присущую коду Хэмминга, а именно проверку на общую четность, используемую для выВ

- Z ® X . ,

50

55

где j 6 О, I, 2га.

Выходы сумматоров 3 и 4 соединены с соответствующими входами сумматоров 6 и 7 узлов 5 обнаружения ошибок в группах, которые формируют значения разрядов синдрома путем сложения по модулю два сигналов с сумматоров 3 и 4 с соответствующими контрольными символами.

верок. При двойной ошибке разряды синдрома дают четную комбинацию, так как сумма по модулю два двух вектор- столбцов проверочной матрицы, соотделения двойной ошибки. В устройстве :сигнал некорректируемой ошибки фор- мируется путем анализа значений раз- рядов синдрома в каждой группе проветствующих отказавшим информационным символам, всегда четная. Одиночная ошибка формирует нечетную комбинацию

с с

}

5 II 5 , определяющие номер ошибочного разряда в байте, а блок 2.2 - проверки S, S, S и S, которые локализируют номер ошибочного байта. Указанная реализация осуществляется в два этапа. Сначала с помо- Щью восьмивходовьж сумматоров 3.1- З.п и 4.1-4.m по модулю два группы символов кода формируются сигналы сумм по модулю два байтов и разрядов информационных символов. Для информационного слова длиной N 64 число байтов равно числу разрядов в байте п 8 и, следовательно, число сумматоров по модулю два группы символов

j 1.©Х,.,,

g- где je О, 1, 2, ..., п;

а на выходах сумматоров 4 формируется

сигнал

В

- Z ® X . ,

где j 6 О, I, 2га.

Выходы сумматоров 3 и 4 соединены с соответствующими входами сумматоров 6 и 7 узлов 5 обнаружения ошибок в группах, которые формируют значения разрядов синдрома путем сложения по одулю два сигналов с сумматоров 3 и 4 с соответствующими контрольными символами.

3

P, © РЗ © Py © P, Ф К„;

. P ® РЗ ® PS ® P7 @K,;

Sj P ® Pj ©РЬ ©PT

Sj Po ©PI ® PS ©Pfc

B, © БЗ © Bj ® B,

Sj Bj 8 Вз 0 Bj ® B, © K,;

Sfe B 8 By ©B 8 B, ©Kt;

s, BO ® Bj©Bj©B ек.

Выходы сумматоров 6 и 7 соединены с соответствующими входами дешифраторов 8,1 и 8.2, выполненных, например, на микросхеме 133ИД4. Выходы 14 дешифраторов 8 соединены с входами дешифратора 9, который реализует функцию И, определяя номер неисправного разряда. Выходы 13 и 14 дешифратора 8 соединены с входами диагностического дешифратора 15, которьй содержит .элементы ИЛИ 19 (четных и нечетных комбинаций синдрома ошибки), реализованные, например, на восьмивходовых элементах И микросхем 133ЛА2, выходы которых соединены с входами элементов И 20 (формирования ошибок и койт- рольных символов) и входами .элемента 21 ИЛИ (формирования некорректируемой ошибки). Выходы 12 дешифраторов 8 соединены с входами элементов И 20(формирования сигнала отсутствия ошибки) .

Устройство работает следуюшлм образом.

На входы 1 параллельно поступают информационные Х. и контрольные символы кода.

Отсутствуют ошибки входной лКчг п: мации и нет отказов оборудования устройства .

Сигналы на выходах сумматоров 6 и 7 дают нулевые зн-| .г ния разрядов синдрома ошибки, погтог-о 1 Дин1- тные значения появляются на з:- :содах 12 дешифратора 8 отиио. - . в группах При поступлении зти;: сигняттпв ходы диагностичес:сого дешк.атг-ра 15 .на выходе 16 формируется сигнал ствия ошибки, а так ;сак выходы l-i дешифраторов 8 имеют значения О, то информационные символы передаются на выход 11 устройства без искажений.

Наличие ошибок во входных информационных символах, отсутствие .отказов оборудования устройства.

При ошибочном информационном символе Х- на выходах сумматоров 6, а также на выходах сумматоров 7 всегда нечетная комбинация значений разрядов синдрома. Поэтому на выходах 14 де398984

шифраторов 8 появляются единичные значения, соответствующие номеру отказавшего информационного символа в байте и номеру отказавшего байта. На выходе дешифратора 9 появляется сигнал, однозначно соответствующий номеру ошибочного информационного символа в коде, и на выходе 11 блока Q исправления ошибок - исправленный информационный символ.

Отсутствие ошибок информационных символов и наличие отказов оборудования устройства или ошибки в конт- 5 рольных символах.

При отказах основной части оборудования (сумматоров 3, 4, 6, 7) или сбоях в контрольных символах кода значения разрядов синдрома ошибки Q всегда имеют два состояния: значения разрядов SP, S, Sj, Sj равны О, а S, Sj, S , S дают нечетное двоичное число, значения разрядов S , 85, Sj и S равны О, а -So, S, Sj 5 и Sj дают нечетное число.

Поэтому на одном выходе 14.1 или 14.2 дешифраторов 8 всегда нулевой сигнал, являющийся сигналом запрета для дешифратора 9, а на выходе 17 де- Q шифратора 15 появляется сигнал о наличии сбоя в контрольных разрядах или сбоях оборудования устройства. Информационные символы при этом передаются на выход 11 устройства без искажений.

Наличие двойньпс ошибок во входной информации или отказы оборудоБани5 стройства и одиночные ошибки во входной информации.

и эт случае значения разрядов слн poMci ошибки S(-Sj или S -S. дают четное двоичное число, оэтому на выходе 13.1 или 13.2 дешх фуаторов 8 появляется сигнал, соотвзтствующий четному числу синдрома ошибки, а на выходе 18 дешифратора 5 - сигнал о наличии некорректируемой ошибки. При этом нч вы.с6дах 12 и 14 дешифратора 8 сигналы не Нормируются, информационные символы Г оедаются без искажений, а сигнал с выхода 18 дешифратора 15 может быть использован в -целях останова вычислительного процесса.

5

0

0

55

.Формула изобретения

1. Устройство для контроля информации на четность, содержащее два блока обнаружения ошибок, каждый из

которых содержит сумматоры по модулю два группы символов кода и узел обнаружения ошибок в группах, состоящий из сумматоров по модулю два обнаружения ошибок в группах и дешифратора ошибок в группах, кроме того, устройство содержит дешифратор ошибок и блок исправления ошибок, причем в

каждом блоке обнаружения ошибок входы Q и второго блоков обнаружения ошибок, сумматоров по модулю два группы сим- а первый, второй и третий выходы диагностического дешифратора являются соответственно выходами Отсутствие ошибки, Сбой и Некорректируемая

волов кода соединены с соответствующими информационными входами устрой20

ства, а их выходы - с первыми входами соответствующих сумматоров по модулю ig ошибка устройства, два обнаружения ошибок в группах своего блока, вторые входы которых соединены с входами контрольных разрядов устройства, а выходы - с входами соответствующих дешифраторов ошибок в группах, информационные входы блока исправления ошибок соединены с информационными входами устройства, а выходы являются информационными выходами устройства, вход корректирующей информации блока исправления ошибок соединен с выходом дешифратора ошибок, входы которого соединены с -первыми выходами дешифраторов ошибок в группах узлов обнаружения ошибок в группах первого и второго блоков обнаружения ошибок, отличающееся тем, что, с целью повышения быстродействия, устройство содержит диагностический дешифратор, а число сумматоров по модулю два группы символов кода в первом и втором блоках обнаружения ошибок равно соответственно п (где п - число байтов в ин2. Устройство по п.1, о т л и ч а- ю щ е е с я тем, что диагностический дешифратор содержит пять элементов ИЛИ и три элемента И, причем входы с первого по четвертый элементов ИЛИ образуют соответственно третий, второй, четвертью и пятый входы Дешифратора, первые входы первого и второ25 го элементов И объединены и являются шестым входом дешифратора, второй вход первого элемента И и первьш вход третьего элемента И объединены и являются первым входом дешифратора,

30 вторые входы второго и третьего элементов И соединены соответственно с выходами первого и третьего элементов ИЛИ, первый и второй входы пятого элемента ИЛИ соединены с выходами второго и четвертого элементов ИЛИ, выход которого является выходом Некорректируемая ошибка дешифратора, выход первого элемента И является выходом Отсутствие ошибки дешифраформационном слове) и m (где m - чис- „ тора, выходы второго и третьего эле- ло разрядов в байте), число суммато- ментов И образуют выход Сбой устров по модулю два обнаружения ошибок

в группах узлов обнаружения ошибок в группах равно соответственно log. 1 и I, причем с первого по шестой входы диагностического дешифратора соединены соответственно с первыми, вторыми и третьими выходами дешифратора ошибок в группах узлов обнаружения ошибок в группах первого

ошибка устройства,

2. Устройство по п.1, о т л и ч а- ю щ е е с я тем, что диагностический дешифратор содержит пять элементов ИЛИ и три элемента И, причем входы с первого по четвертый элементов ИЛИ образуют соответственно третий, второй, четвертью и пятый входы Дешифратора, первые входы первого и второго элементов И объединены и являются шестым входом дешифратора, второй вход первого элемента И и первьш вход третьего элемента И объединены и являются первым входом дешифратора,

вторые входы второго и третьего элементов И соединены соответственно с выходами первого и третьего элементов ИЛИ, первый и второй входы пятого элемента ИЛИ соединены с выходами второго и четвертого элементов ИЛИ, выход которого является выходом Некорректируемая ошибка дешифратора, выход первого элемента И является выходом Отсутствие ошибки дешифраройства.

Редактор О.Юрковецкая

Заказ 4351/56Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

. со

Составитель И.Хазова Техред М.Ходанич

Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 1999 |

|

RU2210805C2 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Устройство для коррекции ошибокС САМОКОНТРОлЕМ | 1977 |

|

SU796847A1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2014 |

|

RU2542665C1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2297032C2 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297030C2 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297034C2 |

| ОТКАЗОУСТОЙЧИВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2297035C2 |

| Устройство для обнаружения и исправления ошибок | 1982 |

|

SU1149263A1 |

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

Изобретение относится к области вычислительной техники и касается техники передачи и хранения информации. Цель изобретения - повышение быстродействия устройства. Отличительная особенность устройства состоит в том, что за счет введения дополнительных проверок в каждую группу проверок значения разрядов синдрома ошибки при одиночных отказах информационных символов дают нечетную сумму по модулю два, при сбоях в контрольных символах кода и сбоях в аппаратуре устройства - нечетная сумма только в одной группе проверок при нулевых значениях разрядов синдрома в другой группе проверок, при двойной ошибке в информационных символах значения разрядов синдрома дают четную сумму по модулю два. Это позволяет за время If после формирования значений разрядов синдрома получить с выходов дешифраторов ошибок в-группах сигналы номера неисправного байта и номера неисправного разряда в байте. Кроме того, введение диагностического дешифратора 15, .входы которого соединены с выходами дешифраторов ошибок в группах 8.1, 8.2, обеспечивает оперативную локализацию и диагностику отказов. Устройство содержит блоки обнаружения ошибок 2.1, 2,2, дешифратор 9 ошибок, блок 10 исправления ошибок. 1 з.п. ф-лы, 3 ил. (Л Ю 11 оо оо г 00 ( 00 15 ;/7 18

| Устройство для декодирования кодов с к проверками на четность | 1972 |

|

SU451084A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для декодирования кодов с @ проверками на четность | 1980 |

|

SU1257648A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1985-12-26—Подача