Изобретение относится к вычисли- тельной технике я может быть использовано для обнаружения и исправления ошибок в тракте приема - передачи дискретных данных, например, при считывании данных из оперативной памяти в процессор вычислительно машины или записи данных из процессора в оперативную память. Известно устройство для обнаружения и исправления ошибок, содержащее входной регистр с прямым выходом, формирователь синдрома ошибки, дешифратор ошибок, корректор информа-. дни 113.1 Недостатком известного устройства является низкая степень достоверности передачи данных ввиду отсутствия контроля работы оборудования устройства, Наиболее близким к предлагаемому техническим решением является устрой ство для обнаружения и исправления ошибок в блоках вычислительной машины, содержащее входной регистр, уп-. равляющИй вход которого является первым управляющим входом устройства, контрольный вход - контрольным входом устройства, а выход подключен к информационному входу блока коррек ции информации, адресный вход которо го соединен с выходом дешифратора, а выход - с информационным входом выходного регистра, управляющий вход которого является вторым управляющим входом устройства, а первый выход - информационным выходом устройства, первый формирователь синдрома ошибки, выход синдрома которого подкхпочен к первому входу первой схемы сравнения, вькод которой является первым выходом ошибки устройства, блок коррекции четности, вход коррек ции которого подключен к выходу корректируемой ошибки дешифратора, вторую схему сравнения, блок контроля дешифратора, формирователь контрольного кода по четности скорректирован ной информации и второй формирова- ; тель синдрома ошибки, выход которого соединен с вторьм входом первой схемы-сравнения, а вход - с выходом входного регистра и входом первого формирователя синдрома ошибки, выход контроля по четности которого подключен к входу контроля по .четности блока коррекции четности, а выход синдрома - к входу дешифратора и к входу синдрома блока контроля дешифратора, входы корректируемой ошибки, некорректируемой ошибки и неразрешенных комбинаций которого соединены с выходами корректируемой ошибки, некорректируемой ошибки и неразрешенных комбинаций депиифратора соответственно, а выход является вторым выходом опшбки устройства, выход блока коррекции четности пoдкJПoчeн к первому входу второй схемы сравнения, второй вход которой соединен с выходом формирователя контрольного кода по четности скорректированной информации, вход которого подключен к второму выходу выходного регистра, а выход является Выходом контрольных разрядов по четности устройства, выход второй схемы сравнения является третьим выг ходом ошибки устройства, тактовый вход триггера ошибки коррекции является синхровходом признака ошибки устройства C2J. Однако объем контрольного обору дования очень высок при низкой степени его эффективности. Схемы контроля по четности позволяют обнаружить только одну Ошибку в блоке коррекции информации либо в выходном регистре. Двойная ошибка в этих узлах известного устройства либо одновременная одиночная в казкдом из них не может быть обнаружена. Дешифратор устройства сложен и требует для построения много оборудования. При дешифрации синдромного кода приходится декодировать все разрешенные комбинации, некорректируемые, а также недопустимые комбинации и формирователь признака указанных комбинаций, что приводит к незначительной временной задержке результатов контрольных проверок. Кроме того, функциональные возможности известного устройства Ограничены (нельзя применить в тракте передачи информации, так как оно не может присваивать передаваемой информации контрольный код). Цель изобретения - повьш1ение достоверности контроля передачи информации при одновременном сокращет НИИ оборудования и повьш1ении быстродействия . Поставленная цель достигается тем, что в устройство для обнаружеия и исправления ошибок в блоках выислительной машины, содержащее

входной и выходной регистры, формирователь синдрома ошибки, дешифратор, блок коррекции информации и схему сравнения, причем вход сообщения устройства соединен соответственно с первой и второй группами информационных входов входного регистра, выходы которого соединены соответственно с информационными входами бло ка коррекции информации, выходы формирователя синдрома ошибки соединены с входами схемы сравнения и входами дешифратора, выходы которого соединены с адресным входом блока коррекции, выходы которого соединены соответственно с информационными входами выходного регистра, выходы которого являются первой группой информационных выходов устройства, введены триггер ошибки коррекции, триггер признака одиночной ошибки, триггер признака двойной ошибки, элемент И, злемент ИЛИ и элемент НЕ, причем первая группа входов формирователя синдрома ошибки соединена соответственно с первой группой выходов входного и выходного регистров, вторая группа входов формирователя синдрома ошибки соединена соответственно с второй группой выходов входного и выходного регистров, выходы формирователя синдрома ошибки соединены с входами элемента ИЛИ, выход которо.го соединен с первьм входом элемента И и информационным входом триггера ошибки коррекции, выход схемы сравнения соединен с информационным входом триггера признака одиночной ошибки и.с входом элемента НЕ, выход которого соединен с вторым входом элемента И, выход элемента И соединен с информационным входом триггера признака двойной ошибки, прямые выходы триггеров ошибки коррекции, признака одиночной ошибки и признака двойной ошибки образуют контрольный выход устройства, вход сброса устройства соединен с входом установки Б ноль первой группы информационных входов входного регистра, первый вход разрешения устройства соединен с входом считывания первой и второй групп выходов входного регистра, второй вход разрешения устройства соединен с входом считывания первай и второй групп выходов выходного регистра, выходы входного регистра и формирователя синдрома ошибки образуют вторую группу информационных выходов устройства, тактовый вход I триггера ошибки коррекции является синхровходом йризнака ошибки устройства.

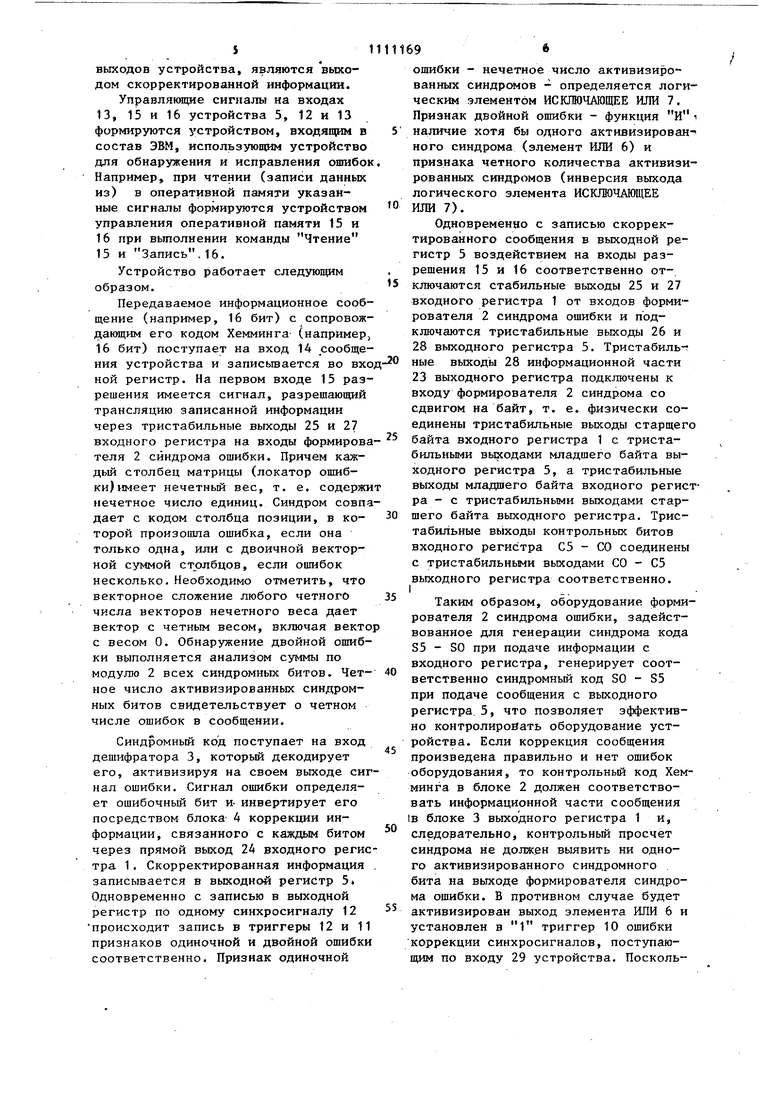

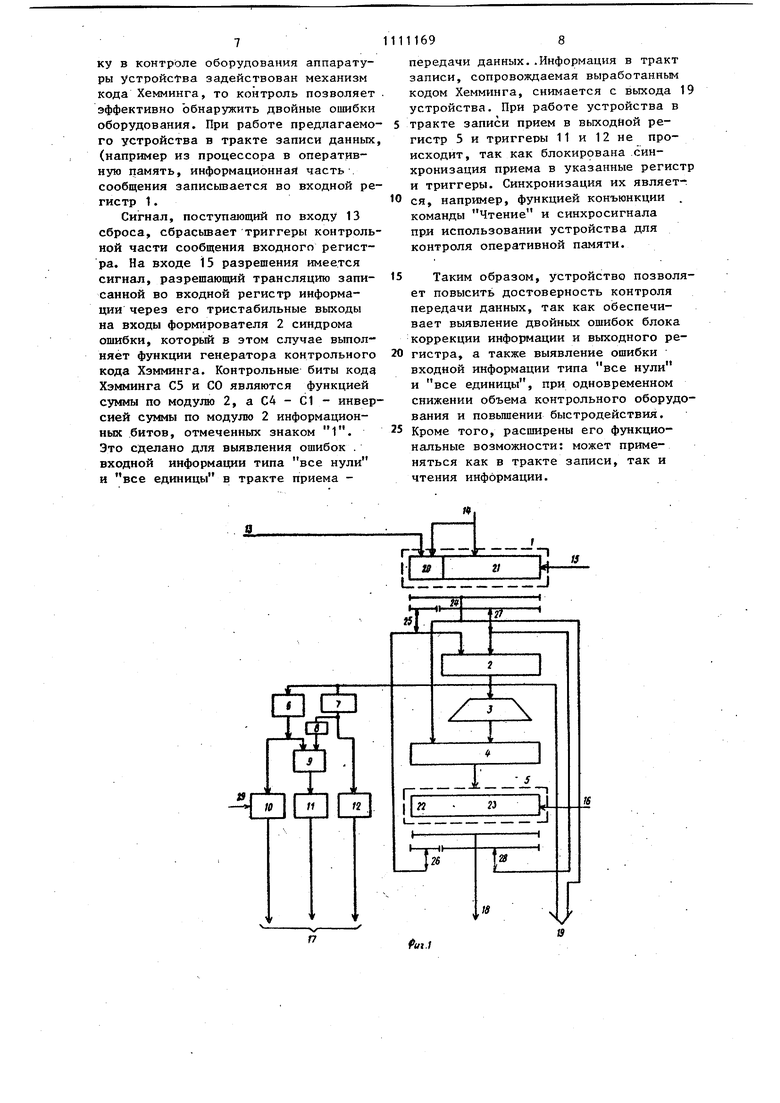

На фиг. 1 представлена блок-схема

устройства на фиг. 2 - матрица формирования синдрома ошибки; на фиг.Зматрица формирования контрольного кода Хэмминга.

Устройство содержит входной регистр 1, формирователь 2 синдрома ошибки, дешифратор 3, блок 4 коррект ции информации, выходной регистр 5, элемент ИЛИ 6, схему 7 сравнения, элемент НЕ 8, элемент И 9, триггер 10 ошибки коррекции, триггер 11 признака двойной ошибки, триггер 12 признака одиночной ошибки, вход 13 ; сброса, вход 14 сообщения, входы 15 и 16 разрешения, контрольный выход 17, группы 18 и 19 информационных выходов. На первую группу 20 информационных входов входного регистра

1поступает контрольная часть сообщения,, а на вторую группу 21 - информационная часть. Выходной регистр также разделен на две части: контрольную 22 и информационную 23. Входной и выходной регистры состоят из

J)-триггеров с прямыми и тристабильными выходами. При этом выходы 24 входного регистра образованы прямыми вькодами триггеров, а первые группы 25, 26 и вторые группы 27, 28 выходов соответственно входного и выходного регистров их тристабильными выходами. Вход 29 устройства является синхровходом признака ошибки.

Блок 4 коррекции информации представляет собой я (по числу разрядов сообщения) двухвходовых элементов, реализующих функцию суммы по модулю 2.

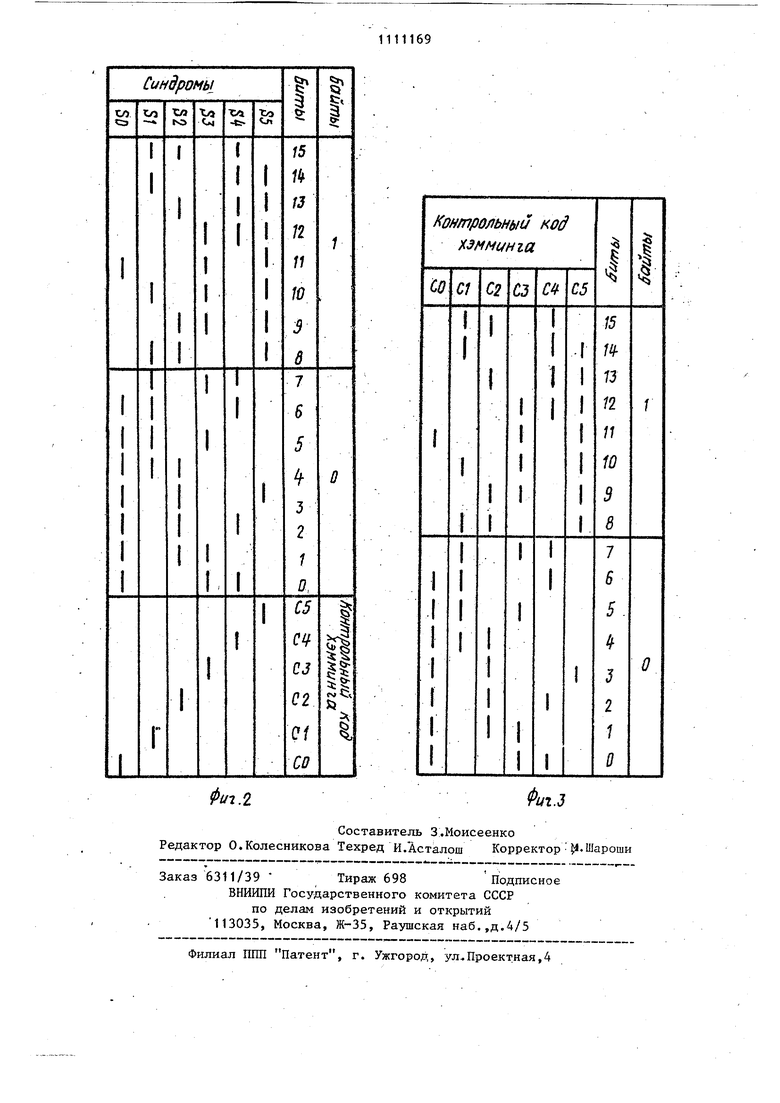

В основу построения формирователя

2синдрома ошибки положена симметричная матрица модифицированного кода Хемминга, состоящая из элементов, реализующих функцию ИСКЛЮЧАЮЩЕЕ ИЛИ.Выходы формирователя 2 синдрома ошибки совместно с прямыми выхо дами 24 входного регистра 1 составляющие вторую группу информационных выходов устройства являются его выходом в тракт записи. Прямые выходы выходного регистра 5, составляющие первую группу информационных вьпсодов устройства, являются выходом скорректированной информации. Управляющие сигналы на входах 13, 15 и 16 устройства 5, 12 и 13 формируются устройством, входящим в состав ЭВМ, использующим устройство для обнаружения и исправления оншбок Например, при чтении (записи данных из) в оперативной памяти указанные сигналы формируются устройством управления оперативной памяти 15 и 16 при вьшолнении команды Чтение 15и Запись.16. Устройство работает следующим образом. Передаваемое информационное сообщение (например, 16 бит) с сопровождающим его кодом Хемминга- (например, 16бит) поступает на вход 14 сообщения устройства и записывается во вхо ной регистр. На первом входе 15 разрешения имеется сигнал, разрешающий трансляцию записанной информации через тристабильные выходы 25 и 27 входного регистра на входы формирова теля 2 синдрома ошибки. Причем каждый столбец матрицы (локатор ошибки) имеет нечетньй вес, т. е. содержи нечетное число единиц. Синдром совп дает с кодом столбца позиции, в которой произошла ошибка, если она только одна, или с двоичной векторной суммой ст элбцов, если ошибок несколько. Необходимо отметить, что векторное сложение любого четного числа векторов нечетного веса дает вектор с четным весом, включая векто с весом 0. Обнаружение двойной ошибки выполняется анализом суммы по модулю 2 всех синдромных битов. Четное число активизированных синдромных битов свидетельствует о четном числе ошибок в сообщении. Синдромный код поступает на вход дешифратора 3, который декодирует его, активизируя на своем выходе сиг нал ошибки. Сигнал ошибки определяет ошибочный бит и- инвертирует его посредством блока 4 коррекции информации, связанного с каждым битом через прямой выход 24 входного регис тра 1. Скорректированная информация записывается в выходной регистр 5. Одновременно с записью в выходной регистр по одному синхросигналу 12 происходит запись в триггеры 12 и 11 признаков одиночной и двойной ошибки соответственно. Признак одиночной 1 9ft ошибки - нечетное число активизиро ванных синдромов - определяется логическ№4 элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 7. Признак двойной ошибки - функция наличие хотя бы одного активизированного синдрома (элемент ИЛИ 6) и признака четного количества активизированных синдромов (инверсия выхода логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7). Одновременно с записью скорректированного сообщения в выходной регистр 5 воздействием на входы разрешения 15 и 16 соответственно отключаются стабильные выходы 25 и 27 входного регистра 1 от входов формирователя 2 синдрома ошибки и подключаются тристабильные выходы 26 и 28 выходного регистра 5. Тристабиль-г ные выходы 28 информационной части 23 выходного регистра подключены к входу формирователя 2 синдрома со сдвигом на байт, т. е. физически соединены тристабильные выходы старщего байта входного регистра 1 с тристабильными выходами младшего байта выходного регистра 5, а тристабильные выходы младшего байта входного регистра - с тристабильньтми выходами старшего байта выходного регистра. Тристабильные выходы контрольных битов входного регистра СЗ - СО соединены с тристабильньми выходами СО - С5 выходного регистра соответственно. Таким образом, оборудование формирователя 2 синдрома ошибки, задействованное для генерации синдрома кода S5 - SO при подаче информации с входного регистра, генерирует соответственно СИНДРОМНЫЙ код SO - S5 при подаче сообщения с выходного регистра. 5, что позволяет эффективно контролировать оборудование устройства. Если коррекция сообщения произведена правильно и нет ошибок оборудования, то контрольный код Хемминга в блоке 2 должен соответствовать информационной части сообщения IB блоке 3 выходного регистра 1 и, следовательно, контрольньй просчет синдрома не должен выявить ни одного активизированного синдромного . бита на выходе формирователя синдрома ошибки. В противном случае будет активизирован выход элемента ИЛИ 6 и установлен в 1 триггер 10 ошибки коррекции синхросигналов, поступающим по входу 29 устройства, Поскольку в контроле оборудования аппаратуры устройства задействован механизм кода Хемминга, то контроль позволяет эффективно обнаружить двойные ошибки оборудования. При работе предлагаемого устройства в тракте записи данных (например из процессора в оперативную память, информационная часть сообщения записьшается во входной регистр 1.

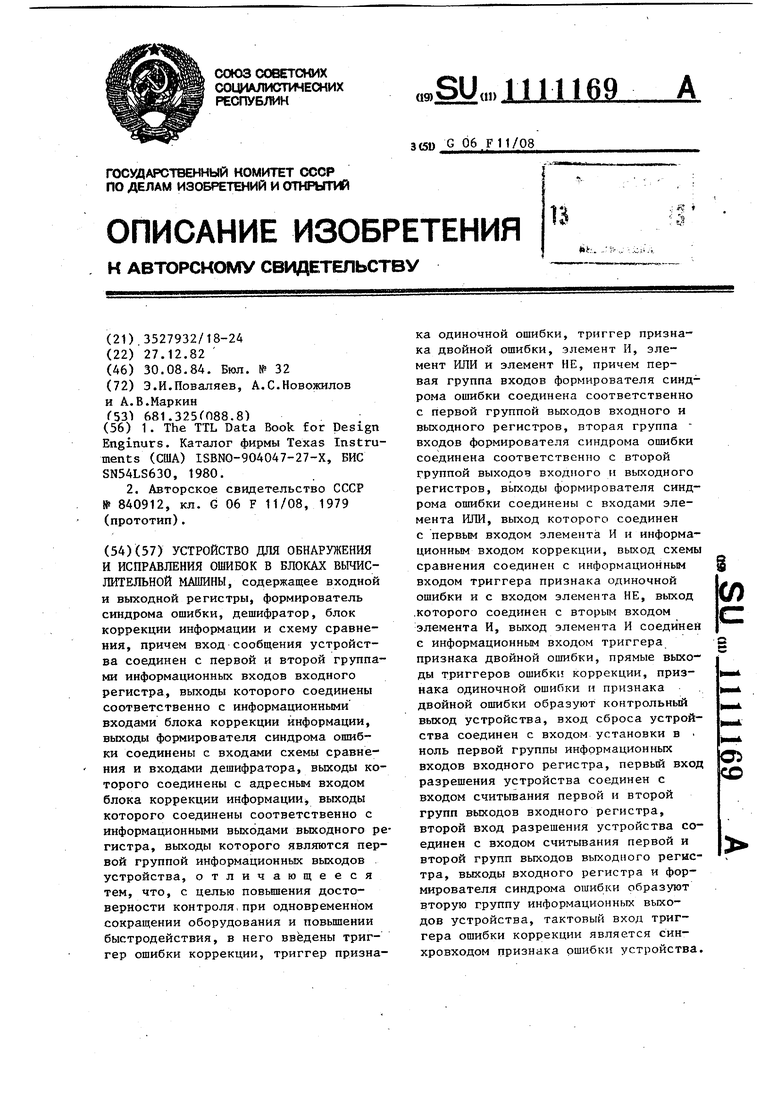

Сигнал, поступающий по входу 13 сброса, сбрасьтаеттриггеры контрольной части сообщения входного регистра. На входе 15 разрешения имеется сигнал, разрешающий трансляцию записанной во входной регистр информации через его тристабильные выходы на входы формирователя 2 синдрома ошибки, который в этом случае выполняет функции ген.ератора контрольного кода Хэмминга. Контрольные- биты кода Хэмминга С5 и СО являются функцией суммы по модулю 2, аСА-С1 - инверсией суммы по модулю 2 информационных битов, отмеченных знаком 1. Это сделано для выявления ошибок . входной информации типа все нули и все единицы в тракте приема передачи данных,.Информация в тракт записи, сопровождаемая выработанным кодом Хемминга, снимается с выхода 19 устройства. При работе устройства в тракте записи прием в выходной регистр 5 и триггеры 11 и 12 не происходит, так как блокирована .синхронизация приема в указанные регистр и триггеры. Синхронизация их является, например, функцией конъюнкции . команды Чтение и синхросигнала при использовании устройства для контроля оперативной памяти.

Таким образом, устройство позволяет повысить достоверность контроля передачи данных, так как обеспечивает выявление двойных ошибок блока коррекции информации и выходного регистра, а также выявление ошибки входной информации типа все нули и все единицы, при одновременном снижении объема контрольного оборудования и повьш1ении быстродействия.

Кроме того, расширены его функциональные возможности: может применяться как в тракте записи, так и чтения информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления двухкратных ошибок в блоках передачи и хранения информации | 1983 |

|

SU1173417A1 |

| Устройство для контроля оперативной памяти | 1978 |

|

SU752502A1 |

| Устройство для исправления двух ошибок в кодовой комбинации с самоконтролем в системах контроля и передачи информации | 1984 |

|

SU1239721A1 |

| Устройство для коррекции ошибокС САМОКОНТРОлЕМ | 1977 |

|

SU796847A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Корректор ошибок | 1989 |

|

SU1810909A1 |

| Запоминающее устройство | 1990 |

|

SU1801227A3 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

п

19

fut.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| The TTL Data Book for Design Enginurs | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для обнаружения и ис-пРАВлЕНия ОшибОК B блОКАХ ВычиСли-ТЕльНОй МАшиНы | 1979 |

|

SU840912A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-30—Публикация

1982-12-27—Подача