Изобретение относится к микроэлектронике и может быть использовано при изготовлении цифровых интегральных схем (НС) с высоким быстродействием.

Цель изобретения - повышение воспроизводимости параметров при увеличении быстродействия интегральной схемы.

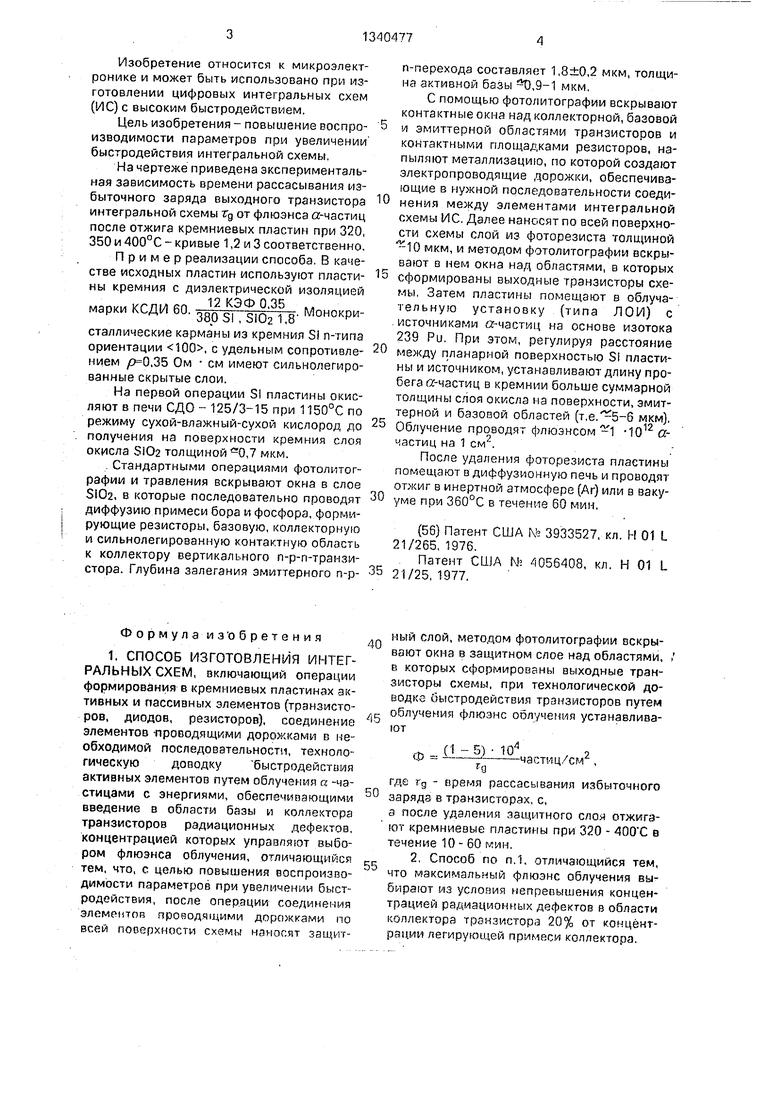

На чертеже приведена экспериментальная зависимость времени рассасывания избыточного заряда выходного транзистора интегральной схемы Гд от флюэнса а-частиц после отжига кремниевых пластин при 320, 350 и 400°С - кривые 1,2 и 3 соответственно.

Пример реализации способа. В качестве исходных пластин используют пластины кремния с диэлектрической изоляцией

марки КСДИ 60. 38osi ti02 8 сталлические карманы из кремния Si л-типа ориентации 100, с удельным сопротивлением .35 Ом см имеют сильнолегированные скрытые слои.

На первой операции Si пластины окисляют 8 печи СДО - }25/3-15 при 1150°С по режиму сухой-влажный-сухой кислород до получения на поверхности кремния слоя окисла S102 толщиной 0,7 мкм.

. Стандартными операциями фотолитографии и травления вскрывают окна в слое Si02, в которые последовательно проводят диффузию примеси бора и фосфора, формирующие резисторы, базовую, коллекторную и сильнолегированную контактную область к коллектору вертикального п-р-п-транзи- стора. Глубина залегания змиттерного п-рФормулаиз обретения

1, СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ, включающий операции формирования в кремниевых пластинах активных и пассивных злементов (транзисторов, диодов, резисторов), соединение элементов -проводящими дорожками в необходимой последовательности, технологическую доводку быстродейстоия активных элементов путем облучения а -частицами с энергиями, обеспечивающими введение в области базы и коллектора транзисторов радиационных дефектов. концентрацией которых управляют выбором флюэнса облучения, отличающийся тем, что, с целью повышения воспроизводимости параметров при увеличении быстродействия, после операции соединения элементов проводящими дорожками по всей поеерхности схемы наносят защитп-перехода составляет 1,8±0,2 мкм, толщина активной базы ,9-1 мкм.

С помощью фотолитографии вскрывают контактные окна над коллекторной, базовой

и эмиттарной областями транзисторов и контактными площадками резисторов, напыляют металлизацию, по которой создают электропроводящие дорожки, обеспечивающие в нужной последовательности соединения между элементами интегральной схемы ИС. Далее наносят по всей поверхности схемы слой из фоторезиста толщиной 10 мкм, и методом фотолитографии вскрывают в нем окна над областями, в которых

сформированы выходные транзисторы схемы. Затем пластины помещают в облуча- тельную установку (типа ЛОИ) с источниками а-частиц на основе изотока 239 PU. При этом, регулируя расстояние

между Планерной поверхностью SI пластины и источником, устанавливают длину пробега а-частиц в кремнии больше суммарной толщины слоя окисла на поверхности, змит- терной и базовой областей (т.е. 5-6 мкм).

Облучение проводят флюэнсом 1 -10 а- частиц на 1 см.

После удаления фоторезиста пластины помещают в диффузионную печь и проводят отжиг в инертной атмосфере (Аг) или в вакууме при 360°С в течение 60 мин.

(56) Патент США Kb 3933527, кл. Н 01 L 21/265, 1976.

. Патент США W; 4056408, кл. Н 01 L 21/25. 1977.

ный слой, методом фотолитографии вскрывают окна в защитном слое над областями, / в которых сформированы выходные транзисторы схемы, при технологической доводке быстродействия транзисторов путем облучения флюзнс облучения устанавливают

.. (1 - 5) .2

Ф - --частмц/см ,

а

где Гд - время рассасывания избыточного заряда в транзисторах, с, а после удаления защитного слоя отжигз- ют кремниевые пластины при 320 - 400 С в течение 10-60 мин.

2. Способ по П.1. отличающийся тем, что максимальный флюэнс облучения выбирают из услоЕ ия непрееышения концентрацией радиационных дефектов в области коллектора транзистора 20% от концентрации легирующей примеси коллектора.

W

--Ц г - i-Д-t II I 1 I 1 r I т- I I. .- J-- -.-fc,, .,|.|

3 5 Г Z 3 S 30 i 3 5 10

Ф -част.ем

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ изготовления биполярных транзисторов | 1991 |

|

SU1800501A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МЕХАНОЭЛЕКТРИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 1979 |

|

SU797454A1 |

| Способ изготовления интегральных схем | 1989 |

|

SU1671070A1 |

| Способ изготовления интегральной схемы | 1976 |

|

SU594838A1 |

| Способ изготовления интегральных схем | 1984 |

|

SU1223784A1 |

| Способ изготовления инжекционных интегральных схем | 1980 |

|

SU986236A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА С УПРАВЛЯЮЩИМ ЭЛЕКТРОДОМ СУБМИКРОННОЙ ДЛИНЫ | 1991 |

|

RU2031481C1 |

| СПОСОБ СОЗДАНИЯ СГЛАЖЕННОГО РЕЛЬЕФА В ИНТЕГРАЛЬНЫХ СХЕМАХ | 1990 |

|

SU1766214A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ВЫСОКОВОЛЬТНЫХ ИНТЕГРАЛЬНЫХ СХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1990 |

|

SU1739805A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВЫХ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1981 |

|

SU1116919A1 |

Изобретение относится к микроэлектронике, а более конкретно к технологии изготовления цифровых интегральных схем. Цель изобретения - повышение воспроизводимости параметров при увеличении быстродействия интегральных схем. В кремниевой плааине формируют известными техологическими приемами активные и пассивные элементы интефалькых схем Соед1« яют элементы токоведущими дфожками. Для достижения цели фотолитофафией вскрывают в фоторезисте окна под областями выходных транзисторов схем, облучают базовые и коллекторные области выходных транзиаоров с флюэнсом Ф, Ф(1-5)1oVт частиц на 1 см. где т фемя рас- плывания избыточного разряда в тран сторах из- uepeiwoe в секундах Удаляют слой фоторезиаа и в заключении от ю1гаЮт фемниевые пластины при 320 - 8 течение 10 - 60 мин 1 злф-лы: 1 ил.

Редактор Н.Тимонина

Составитель В.Устинов Техред М.Моргентал

Заказ 3333

Тираж. Подписное

НПО Поиск Роспатента 113035, Москва. Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул.Гагарина, 101

Корректор Л.Пилипенко

Авторы

Даты

1993-11-30—Публикация

1986-03-31—Подача